# TOSHIBA

## TC35815CF Flow Control 10/100Mbps Ethernet Controller

1 9 9 9

### PRELIMINARY

DATA SHEET

#### © 1999 Toshiba America Electronic Components, Inc.

#### Published in April, 1999

Toshiba products described in this document are not authorized for use as critical components in life support systems without the written consent of the appropriate officer of Toshiba America, Inc. Life support systems are either systems intended for surgical implant in the body or systems which sustain life. A critical component is any component of a life support system whose failure to perform may cause a malfunction or failure of the life support system, or may affect its safety or effectiveness.

The information in this document has been carefully checked and is believed to be reliable. However, no responsibility can be assumed for inaccuracies that may not have been caught.

All information in this document is subject to change without prior notice. Furthermore, Toshiba cannot assume responsibility for the use of any license under the patent rights of Toshiba or any third parties.

This technical data may be controlled under U.S. Export Administration Regulations and may be subject to the approval of the U.S. Department of Commerce prior to export. Any export or re-export, directly or indirectly, in contravention of the U.S. Export Administration Regulations is strictly prohibited.

Brand names and product names mentioned herein may be trademarks or registered trademarks of their respective companies.

## TOSHIBA

| Chapter 1 | Introduction1Document Definition1Features and Benefits3PCI System Block Diagram4Controller Application Configurations4Data Structures5System Control Models6Power Management7Reference Documents7 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2 | External Signals                                                                                                                                                                                  |

| -         | Signal and Power Supply Information                                                                                                                                                               |

|           | Peripheral Component Interconnect (PCI) Signals                                                                                                                                                   |

|           | PCI Address and Data Signals                                                                                                                                                                      |

|           | PCI Control Signals                                                                                                                                                                               |

|           | PCI Bus Arbitration Signals 12                                                                                                                                                                    |

|           | PCI Error Signals                                                                                                                                                                                 |

|           | PCI Interrupt Signals                                                                                                                                                                             |

|           | PCI System Signals                                                                                                                                                                                |

|           | Media Independent Interface (MII) Signals 14                                                                                                                                                      |

|           | Transmit MII Signals 14                                                                                                                                                                           |

|           | Receive MII Signals 15                                                                                                                                                                            |

|           | MII Station Management Signals 16                                                                                                                                                                 |

|           | External 10Mbps Endec Signals 16                                                                                                                                                                  |

|           | Transmit 10Mbps Signals 17                                                                                                                                                                        |

|           | Receive 10Mbps Signals 17                                                                                                                                                                         |

|           | 10Mbps Control Signals 18                                                                                                                                                                         |

|           | External EEPROM or ROM Interface                                                                                                                                                                  |

|           | External CAM Interface Signals                                                                                                                                                                    |

|           | Internal Scan Interface Signals                                                                                                                                                                   |

| Chapter 3 | Functional Blocks                                                                                                                                                                                 |

|           | Overview of Functional Blocks                                                                                                                                                                     |

|           | PCI and DMA Overview                                                                                                                                                                              |

|           | MAC Overview                                                                                                                                                                                      |

|           | MAC Overview                                                                                                                                                                                      |

|           | Peripheral Component Interconnect (PCI) Bus                                                                                                                                                       |

|           | DMA Functional Blocks                                                                                                                                                                             |

|           | PCI Arbiter                                                                                                                                                                                       |

|           | DMA Transmit Controller                                                                                                                                                                           |

|           | DMA Transmit Controller                                                                                                                                                                           |

|           | MAC Functional Blocks                                                                                                                                                                             |

|           | MAC Transmit Block                                                                                                                                                                                |

|           | MAC Receive Block                                                                                                                                                                                 |

|           |                                                                                                                                                                                                   |

|           | Flow Control Block                       | 29 |

|-----------|------------------------------------------|----|

|           | MAC Control and Status Registers         |    |

|           | MII Station Manager                      |    |

|           | PROM Controller.                         |    |

|           | Deviators                                | 04 |

| Chapter 4 | Registers                                |    |

|           | Overview                                 |    |

|           | Register Access                          |    |

|           | Register Address Summary                 | 34 |

|           | PCI Configuration Registers              |    |

|           | Vendor ID Register                       | 36 |

|           | Device ID Register                       | 36 |

|           | PCI Command Register                     | 37 |

|           | Status Register                          | 38 |

|           | Class Code Register                      | 39 |

|           | PCI Control Register                     |    |

|           | I/O and Memory Base Address Registers    | 40 |

|           | Subsystem Vendor ID Register             |    |

|           | Subsystem ID Register.                   |    |

|           | PCI Interrupt Register                   |    |

|           | DMA Control Registers                    |    |

|           | DMA Control.                             |    |

|           | Transmit Frame Pointer                   |    |

|           | Transmit Threshold Control.              |    |

|           | Transmit Polling Control Register        |    |

|           | Buffer List Frame Pointer                |    |

|           | Receive Fragment Size Register           |    |

|           | Interrupt Enable Register                |    |

|           | Descriptor Area Registers                |    |

|           | Interrupt Source Register                |    |

|           | Flow Control Registers                   |    |

|           | MAC Layer Registers                      |    |

|           | MAC Control Register.                    |    |

|           | CAM Control Register.                    |    |

|           | Transmit Control and Status Registers    |    |

|           | Receive Control and Status Registers     |    |

|           |                                          |    |

|           | Station Management Data Access Registers |    |

|           | CAM Access Registers                     |    |

|           | PROM Control Registers                   |    |

|           | System Error Count Registers             | 61 |

| Chapter 5 | Memory Organization                      | 63 |

| •         | Frame Descriptors                        |    |

|           | Next Frame Descriptor Field (FDNext)     |    |

|           | Frame Descriptor System Field (FDSystem) |    |

|           | Frame Descriptor System Field (FDStat)   |    |

|           | Frame Descriptor Length Field (FDLength) |    |

|           |                                          | 05 |

|           | Frame Descriptor Control Field (FDCtl)                        | 65   |

|-----------|---------------------------------------------------------------|------|

|           | Buffer Descriptors                                            | 67   |

|           | Buffer Descriptor Control (BDCtl).                            | 67   |

|           | Buffer Descriptor Status Field (BDStat)                       | 68   |

| Chapter 6 | MAC Operation                                                 | . 69 |

| -         | MAC Frame and Packet Formats                                  | 69   |

|           | Destination Address Format                                    | 71   |

|           | Special Flow Control Destination Address                      |      |

|           | Initialization                                                |      |

|           | MAC Register Access                                           | 72   |

|           | Special Register Clear Operations                             |      |

|           | Transmitting a Frame                                          |      |

|           | The IEEE 802.3 CSMA/CD MAC-layer Protocols                    | 73   |

|           | The MII Transmit Operation                                    | 74   |

|           | Receiving a Frame                                             | 75   |

|           | CAM Operation                                                 | 76   |

|           | Full Duplex PAUSE Operation                                   | 77   |

|           | Transmit Pause Operation                                      | 77   |

|           | Remote Pause Operation                                        | 77   |

|           | Error Signaling                                               | 78   |

|           | Reporting of Errors in Transmit                               | 78   |

|           | Reporting of Errors in Receive                                | 80   |

|           | Accessing Station Management Data                             | 81   |

|           | Accessing an EEPROM or ROM                                    | 81   |

| Chapter 7 | DMA Operation                                                 | . 83 |

|           | PCI Initialization.                                           | 83   |

|           | DMA and MAC Initialization.                                   | 83   |

|           | Queue Initialization                                          | 84   |

|           | Transmit Queue Initialization                                 | 84   |

|           | Buffer List Initialization                                    | 85   |

|           | Receive Descriptor Area Initialization                        | 85   |

|           | Transmitting a Frame                                          | 85   |

|           | Transmit Complete Notification                                |      |

|           | Receiving a Frame                                             | 86   |

|           | Processing Received Frame Descriptors                         | 86   |

|           | Freeing Buffers                                               | 87   |

|           | Processing Interrupts                                         | 87   |

| Chapter 8 | Timing                                                        | . 89 |

|           | PCI Clock Timing Parameters                                   |      |

|           | Detailed Timing Parameters for each PCI Operation/Transaction |      |

|           | PCI Measurement and Test Conditions                           |      |

|           | Detailed Timing Parameters for each MII Operation/Transaction |      |

| Chapter 9  | Electrical Specifications                                     | 93  |

|------------|---------------------------------------------------------------|-----|

| Chapter 10 | Mechanical Specifications                                     | 95  |

| Appendix A | Implementation Limits         Constants          Buffer Sizes | A-1 |

| Appendix B | Glossary                                                      |     |

| Appendix C | Unsupported Features                                          | C-1 |

| Figure 1-1  | Ethernet System Overview                           | 2  |

|-------------|----------------------------------------------------|----|

| Figure 1-1  | PCI System Block Diagram                           | 4  |

| Figure 1-1  | Configuration for 100BASE-T Showing Option         | 5  |

| Figure 1-1  | Data Structure Overview                            | 6  |

| Figure 2-1  | External Signals                                   | 9  |

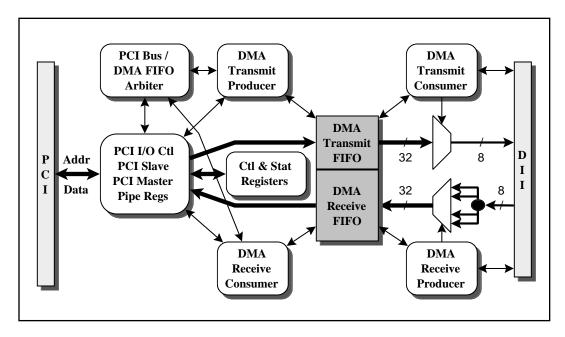

| Figure 3-1  | DMA Functional Blocks                              | 23 |

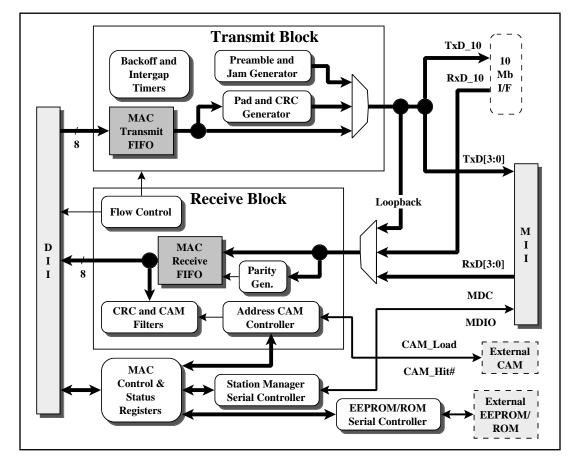

| Figure 3-2  | MAC Functional Blocks                              | 25 |

| Figure 4-1  | Address Map of PCI Configuration Registers         | 34 |

| Figure 4-1  | Address Map of DMA Control Registers               | 34 |

| Figure 4-3  | Address Map of Flow Control Registers              | 35 |

| Figure 4-4  | Address Map of MAC Control and Status Registers    | 35 |

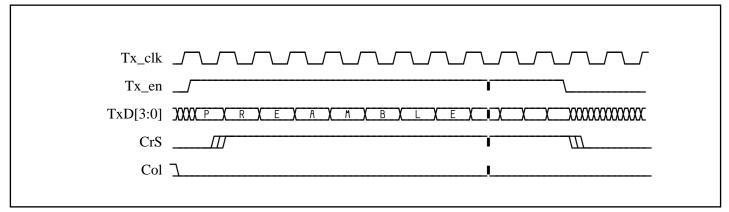

| Figure 6-1  | Transmission Without Collision                     | 74 |

| Figure 6-2  | Transmission With Collision in Preamble            | 75 |

| Figure 6-3  | CAM Memory Map                                     | 76 |

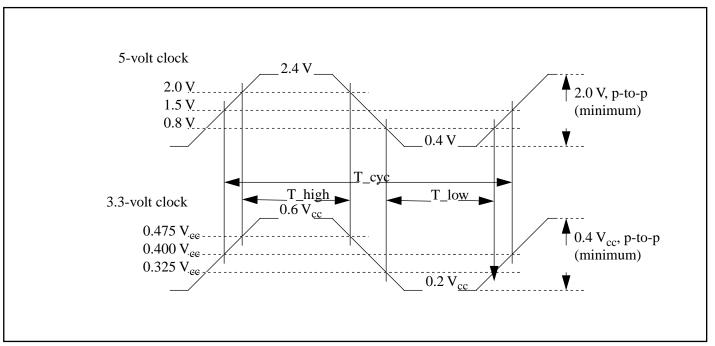

| Figure 8-1  | PCI Clock Waveforms                                | 89 |

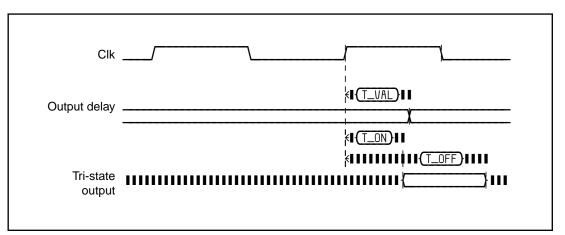

| Figure 8-2  | Output Timing Measurement Conditions               | 90 |

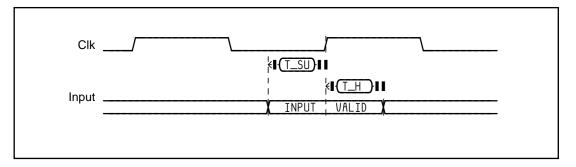

| Figure 8-3  | Input Timing Measurement Conditions                | 90 |

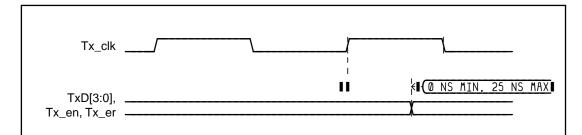

| Figure 8-4  | Transmit signal timing relationships at the MII    | 92 |

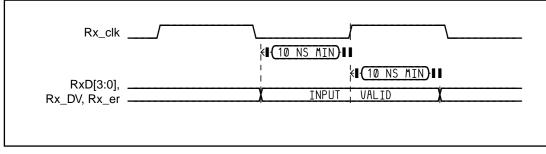

| Figure 8-5  | Receive signal timing relationships at the MII     | 92 |

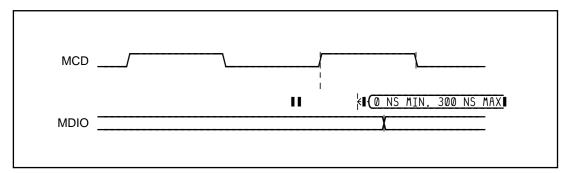

| Figure 8-6  | MDIO sourced by PHY                                | 92 |

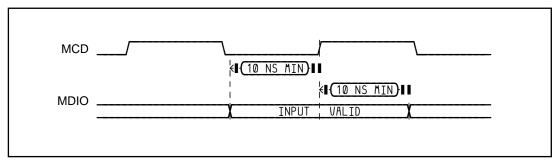

| Figure 8-7  | MDIO sourced by STA                                | 92 |

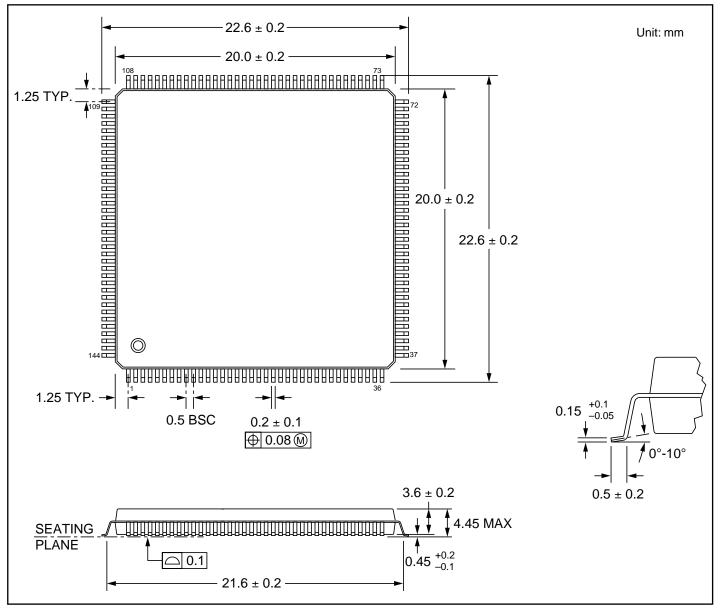

| Figure 10-1 | LQFP144-P-2020-0.50A [144-Pin LQFP (Thin Quad Flat |    |

|             | Package – 1.4mm)]                                  | 95 |

|             |                                                    |    |

This page left blank intentionally

| Table 1-1         | Features and Benefits                           | 3   |

|-------------------|-------------------------------------------------|-----|

| Table 2-1         | Power Supply Information                        | 9   |

| Table 2-2         | Peripheral Component Interconnect (PCI) Signals |     |

| Table 2-3         | Corresponding Between C_BE#[3:0] and AD[31:0]   |     |

| Table 2-4         | Big Endian Byte Order                           | 11  |

| Table 2-5         | Transmit MII Signals                            | 11  |

| Table 2-6         | Receive MII Signals                             | 15  |

| Table 2-7         | MII Station Management Signals                  | 16  |

| Table 2-8         | Transmit 10Mbps Signals                         | 17  |

| Table 2-9         | Receive 10Mbps Endec Interface                  |     |

| <b>Table 2-10</b> | 10Mbps Control Signals                          |     |

| <b>Table 2-11</b> | External EEPROM od ROM Interface                | 19  |

| <b>Table 2-12</b> | External CAM Interface Signals                  |     |

| <b>Table 2-13</b> | Internal Scan Interface Signals                 |     |

| Table 4-1         | PCI Configuration Registers                     |     |

| Table 4-2         | DMA Control Registers                           |     |

| Table 4-3         | Flow Control Registers                          |     |

| Table 4-4         | MAC Control and Status Registers                |     |

| Table 5-1         | Frame Descriptors Format                        | 64  |

| Table 5-2         | Buffer Descriptors Format                       | 67  |

| Table 6-1         | Fields of an IEEE 802.2/Ethernet packet (frame) | 69  |

| Table 8-1         | 5V and 3.3V Timing Parameters                   |     |

| <b>Table 8-2</b>  | Measurement and Test Condition Parameters       |     |

| Table 9-1         | Absolute Maximum Ratings                        |     |

| Table 9-2         | DC Characteristics (PCI Pins)                   |     |

| Table 9-3         | DC Characteristics (Other PCI Pins)             |     |

| <b>Table 10-1</b> | Ethernet Controller Pin Assignments             | 96  |

| Table A-1         | CAM Size                                        | A-1 |

| Table A-2         | Bus Latency and Buffer Sizes                    | A-1 |

|                   |                                                 |     |

This page left blank intentionally

This specification describes a flow control capable Ethernet controller which operates at either 10-Mbit/s or 100-Mbit/s. In half duplex mode, the controller implements the IEEE 802.3 Carrier Sense Multiple Access with Collision Detection (CSMA/CD) protocol. In full duplex mode, the controller implements IEEE 802.3x MAC Control Layer and the PAUSE Operation for flow control. The controller also supports flow control in half duplex mode, and includes programmable support for additional MAC Control functions. The controller supports direct connection to the 32-bit Peripheral Components Interconnect (PCI) Local Bus, and uses bus master burst transfer mode to efficiently move data to and from system memory. The controller has on-chip memory for buffering, so there is no need for external local buffer memory.

The new 100Mbps implementations of Ethernet increase the capacity of a network ten times, while using existing twisted-pair wiring. By keeping the Media Access Control (MAC) layer and the CSMA/CD protocol unchanged, network administrators can quickly adapt newer and faster implementations. This approach also lowers cost of deployment since it allows re-use of existing applications software. By supporting both 10- and 100Mbps speeds, new products may be deployed into markets which are in transition.

One recent advance in Ethernet is the use of full duplex links and switching hubs to greatly increase the capacity of a local area network. These hubs are more expensive than the traditional shared media and simple repeating hubs. But the increase in throughput is significant for a number of applications. Products which support full duplex are well established in the market place, and the demand for such products is expected to grow.

As part of the evolving support for the full duplex mode of operation, the IEEE 802.3x standards group has approved a new standard for flow control. This standard establishes an optional "MAC Control" sublayer and defines the PAUSE Operation, which is supported by this MAC Control sublayer. The PAUSE Operation provides an industry method of supporting flow control in full duplex Ethernet networks.

Toshiba has designed its TC35815CF Flow Control 10/100Mbps Ethernet Controller for use in highly integrated and cost-effective Ethernet solutions. By supporting direct connection to a PCI bus, the chip can be used with a media driver chip to provide a minimum-parts solution.

The TC35815CF Flow Control 10/100Mbps Ethernet Controller is register compatible with previous Toshiba designs, insuring that investments in system and software development can be leveraged in full duplex systems with flow control.

The controller supports an optional 10Mbps interface. The "7-wire interface" supports mother board applications, where systems developers wish to support older 10 Mb/s PHY's to ensure interoperability on installed 10 Mb/s networks.

### **Document Definition**

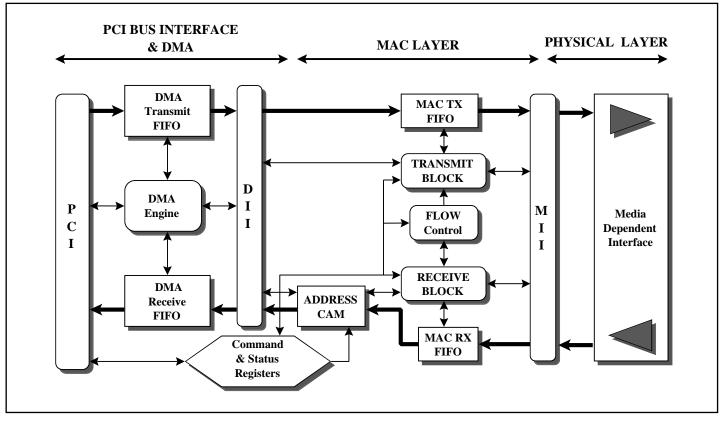

A complete Ethernet circuit is divided into three sections, as shown in Figure 1-1:

- 1. The system bus interface and Direct Memory Access (DMA) engine.

- 2. The Media Access Control (MAC) layer.

- 3. The physical or Medium Dependent Interface (MDI) layer.

The PCI bus interface section contains separate first-in, first-out (FIFO) buffers for transmit and receive, a DMA controller, and a register access module.

The MAC layer consists of transmit and receive blocks, the flow control block, a Content Addressable Memory (CAM) for recognizing addresses, and a number of control, status, and error counter registers. The DMA-Independent Interface (DII) is the interface between the MAC and the DMA section.

The TC35815CF Flow Control 10/100Mbps Ethernet Controller supports the Media Independent Interface (MII). The MII is a standard for a media-independent layer which separates physical-layer issues from the MAC layer. The MII is part of the ISO approved IEEE 802.3 100BASE-T standard for 100Mbps Ethernet.

This document specifies a single chip which implements a PCI bus interface, the DMA engine, and the MAC layer. It is intended as an interface specification and an architectural overview of the device and its operation.

Figure 1-1 Ethernet System Overview

### **Features and Benefits**

Table 1-1 summarizes the features and benefits of the TC35815CF Flow Control 10/ 100Mbps Ethernet Controller.

| Features                       | Benefits                                                     |

|--------------------------------|--------------------------------------------------------------|

| PCI bus interface.             | Direct connection, with no glue logic.                       |

| DMA engine using burst mode.   | Efficient data transfers.                                    |

| Large DMA FIFO buffers.        | No external buffer memory required.                          |

| 16-Byte Receive FIFO buffer    | Allow DMA Latency during PCI bursts.                         |

| 80-Byte Transmit FIFO buffer   | DMA latency; retransmit after collision without DMA action.  |

| Data alignment logic.          | Full data alignment freedom; high bus utilization.           |

| Endian translation.            | Operates with either Big-Endian or Little-Endian processors. |

| Support for old and new media. | Compatible with existing 10Mbps networks.                    |

| 100/10Mbps operation.          | Range of price/performance points. Phased conversion.        |

| Full IEEE 802.3 compatibility. | Compatible with existing applications software.              |

| MII compliant interface.       | Can be used with many 100BASE-T physical layers.             |

| Station management signaling   | External physical layer configuration and link negotiation.  |

| On-chip CAM                    | Address recognition for network traffic filtering.           |

| Optional external CAM          | Support hub and bridge applications with many addresses.     |

| Optional ROM or EEPROM         | Network address and configuration information.               |

| Optional 7-wire Interface      | Allow use of old 10Mps physical layer for compatibility      |

| Full duplex mode               | Doubles bandwidth.                                           |

| PAUSE Operation                | H/W support for full duplex flow control.                    |

| Flexible MAC Control Support   | Software can support future MAC Control Operations.          |

| Long packet mode               | Specialized environments.                                    |

| Short packet mode              | Specialized environments. Fast testing.                      |

| PAD generation                 | Ease of processing, reduced processing time.                 |

| Transmit polling mode          | Minimize system overhead to initiate transmission.           |

| Transmit wake-up control       | Minimize system latency to transmission initiation.          |

| Receive early-notify control   | Minimize system latency to processing received packet.       |

| Power Management               | Minimize power consumption connected to quiet network.       |

Table 1-1 Features and Benefits

### PCI System Block Diagram

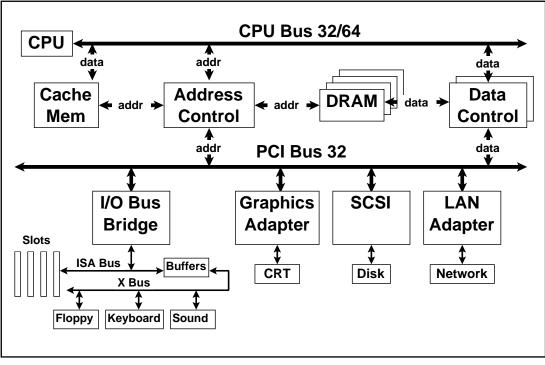

Figure 1-2 shows a typical block diagram for a computer using the TC35815CF Flow Control 10/100Mbps Ethernet Controller. The implementation may integrate various functions in a slightly different way. For example, the memory controller may be implemented as a single controller, or as separate address and data controllers. Also, the variety of available audio and video compression and other peripherals open up a wide range of possibilities.

Figure 1-2 PCI System Block Diagram

### **Controller Application Configurations**

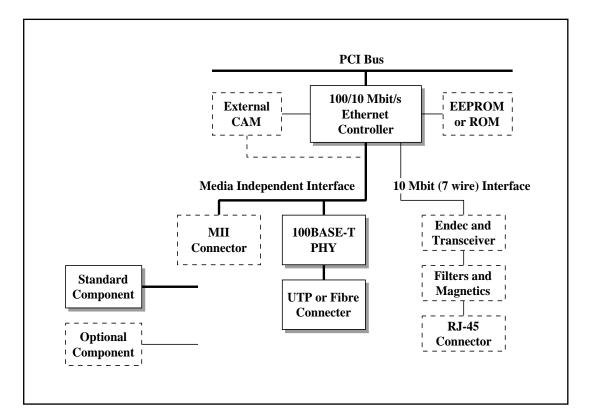

Figure 1-3 shows the components that are likely to be used with the TC35815CF Flow Control 10/100Mbps Ethernet Controller. The controller is normally connected to a 100BASE-T medium which can operate at either 100Mbps or 10Mbps. The MII provides transmit and receive clocks for four-bit parallel operation. The clocks operate at 25MHz for 100Mbps operation, or 2.5MHz for 10Mbps operation.

Optionally, the controller can also be connected to 10BASE-T, to provide customer selection of either old or fast Ethernet in the field. The controller supports a 10-MHz clock rate for serial 10Mbps operation, when connected to a 10Mbps Manchester encoder-decoder (endec).

The system designer has additional options: (1) One or more external CAMs can add many Ethernet addresses for the controller to receive. This is useful for applications such as switching hubs, routers, and bridges, where more addresses must be matched with precision than the controller supports with its on-chip CAM. (2) An inexpensive serial programmable ROM can provide the controller with its Ethernet station address automatically upon power-up. (3) An MII connector can be provided to allow the use of alternate external 100Mbps PHYs.

Figure 1-3 Configuration for 100BASE-T Showing Options

### **Data Structures**

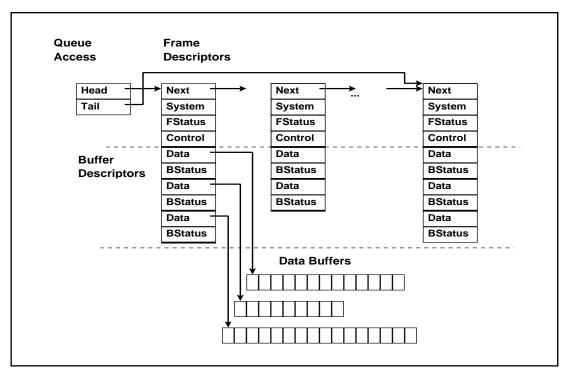

The TC35815CF Flow Control 10/100Mbps Ethernet Controller exchanges control information and data via three data structures:

- Frame descriptors

- Buffer descriptors

- Data buffers

Figure 1-4 shows how these data structures are related.

Frame descriptors have a four-byte pointer to the next frame, a field for the system or applications program to use exclusively, a frame status field, a control field for the entire frame, and an array of associated buffer descriptors. Buffer descriptors have a pointer to a data buffer and control field for the buffer. A data buffer is an array of bytes, which can be stored in either little endian or big endian order. For more details on these data structures, see Chapter 5, "Memory Organization."

The DMA engine supports transfer of data on byte boundaries. Frame descriptors must be aligned on 16 byte boundaries. Buffer descriptors must be aligned on eight-byte boundaries. The DMA engine employs bursts of full four-byte, aligned transfers whenever possible. Alignment in data buffers does not affect performance very much. The DMA engine avoids doing unaligned or partial word accesses, except at the beginning or end of block transfers.

Figure 1-4 Data Structure Overview

### **System Control Models**

The TC35815CF Flow Control 10/100Mbps Ethernet Controller can be programmed for two modes of operation.

- Interrupt on each packet, or group of packets, transmitted or received.

- Poll continuously for new packets to transmit. Post data and descriptors, but do not interrupt for packets received.

An interrupt for each packet or group of packets is the traditional way that Ethernet software is controlled. This is appropriate for occasional network traffic, such as electronic mail.

However, as processors increase in speed and complexity, the time to service an interrupt does not improve correspondingly. In fact, many modern processors have large amounts of state information and sophisticated caching schemes, which can slow the relative speed of interrupt processing even further. Combined with a faster network, where packets may arrive more frequently, the overhead for servicing network interrupts can become a significant burden to the system. Also, some applications, such as interactive conferences, require a much higher level of network traffic. These factors lead to the design of more efficient network control schemes.

By enabling or disabling interrupts for selected frame descriptors, the system can arrange for the controller to process multiple packets between interrupts. This reduces the overhead in servicing interrupts, and improves performance by caching code when the system processes several packets at once.

It is even possible to set up the controller so that it generates no interrupts at all unless serious errors occur. This requires enabling some additional controls, to ensure that the starting and stopping of traffic, and polling during idle times, is handled efficiently. For more details, see Chapter 7, "DMA Operation."

### **Power Management**

The TC35815CF Flow Control 10/100Mbps Ethernet Controller provides for dynamic power management. By reducing the clock rate to idle circuits, the controller consumes significantly less power, while maintaining full network functionality.

Given the current emphasis on the "green desktop", or PCs which meet governmental guidelines for energy efficiency, power management is becoming an issue that affects a broader market segment than just lap-tops and palm-tops. The TC35815CF Flow Control 10/100Mbps Ethernet Controller is designed to provide a fully-functional, yet power efficient solution for networking.

### **Reference Documents**

See the following documents for additional technical information:

*PCI Local Bus Specification*, Revision 2.1, June 1, 1995. PCI Special Interest Group, Hilsboro, Oregon, (800) 433-5177.

*PCI Local Bus Specification*, Production Version, Revision 2.0, April 30, 1993. PCI Special Interest Group, Hilsboro, Oregon, (800) 433-5177.

International Standard ISO/IEC 8802-3, ANSI/IEEE Std 802.3. "Information technology—Telecomunications and Information exchange between systems—Local and metropolitan area networks—Part 3: Carrier sense multiple access with collision detection (CSMA/CD) access method and physical layer specifications," Fifth Edition 1996-07-29.

IEEE Std 802.u-1995(Supplement to International Standard ISO/IEC 8802-3: 1993 [ANSI/IEEE Std 802.3, 1993 Edition]). IEEE Standards for Local and Metroploitan Area Networks: Supplement to Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications. "Media Access Control (MAC) Parameters, Physical Layer, Medium Attachment Units and Repeater for 100 Mb/s Operation, Type 100Base-T. (Clauses 21-30)". Approved June 14, 1995.

*PCI Hardware and Software*, by Edward Solari and George Willse, Second Edition, 1995. Annabooks, San Diego, CA, (619) 673-0870.

*PCI System Architecture*, Third Edition, by Tom Shanley and Don Anderson, February 1995. MindShare, Inc., published by Addison-Wesley.

IEEE Std. 802.3x - 1997 Supplement to Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications:

"Specification for 802.3 Full Duplex Operation".

*Project 802 Local & Metropolitan Area Networks*, Draft Guide to ANSI/IEEE Std 802.3 (CSMA/CD Access Method & Physical Layer Specifications), SYSTAG Network Guide, Draft 5.2, January 23, 1994.

The Ethernet. A Local Area Network. Data Link Layer and Physical Layer Specifications. Digital Equipment Corporation, Intel Corporation, and Xerox Corporation. Version 2.0. (*"The Blue Book"*) November, 1982.

### **Signal and Power Supply Information**

Figure 2-1 shows the 94 external signals for the TC35815CF Flow Control 10/ 100Mbps Ethernet Controller, divided into functional groups. This chapter groups the signal definitions by functional area, giving each signal's symbolic name, full name, direction, clock domain, and brief definition. The groups are:

- 37 for PCI address and data

- 13 for PCI control, arbitration, error reporting, interrupt, and system

- 18 for MII Transmit and Receive 9 for internal scan

- 4 for an optional external EEPROM/ROM

- 9 for an optional 10Mbps Manchester encoder-decoder (endec)

- 2 for an optional external CAM interface

- 5 for internal test

#### Table 2-1 Power Supply Information

| Signal | Pin #                                                                                                       | Function                    |

|--------|-------------------------------------------------------------------------------------------------------------|-----------------------------|

| VSS    | 1, 9, 19, 25, 31, 40, 44, 49, 52, 57, 64, 67, 73, 78, 81, 85, 88, 91, 96, 102, 110, 116, 118, 123, 127, 136 | Ground of power supply (0V) |

| VDD    | 6, 16, 18, 28, 37, 48, 55, 60, 68, 80, 82, 90, 94, 104, 109, 117, 126, 129, 140                             | 3.3V power supply           |

| ← C_BE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31:0] →<br>#[3:0] →<br>Par → PCI Address<br>and Data                                                                                   | Transmit<br>Media<br>Independent                                      | ← Col<br>← Tx_clk<br>TxD[3:0] →                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{ccc} \leftarrow & TT\\ \leftarrow & T$ | ame# →<br>Rdy# → PCI<br>Stop# → Control<br>vSel# →                                                                                     | Interface (MII)<br>Receive<br>Media<br>Independent<br>Interface (MII) | $ \begin{array}{c} -Tx_{-}en  \rightarrow \\ -Tx_{-}er  \rightarrow \\ \leftarrow CrS  - \\ \leftarrow Rx_{-}clk  - \\ \leftarrow RxD[3:0]  - \\ \leftarrow Rx_{-}DV  - \end{array} $                                                                                 |

| ← 1<br>← P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Gnt# → PCI Arbitration<br>Req# → PCI Errors                                                                                            | MII Station<br>Management                                             | $\begin{array}{ccc} & & \\ & \leftarrow \mathbf{Rx}_{er} & - \\ & - \mathbf{MDC} & \rightarrow \\ & \leftarrow \mathbf{MDIO} & \rightarrow \end{array}$                                                                                                               |

| <<br>—                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IntA# PCI Interrupt                                                                                                                    | Transmit<br>10-Mbit/s<br>Endec                                        | $\begin{array}{ccc} \leftarrow \operatorname{Col}_{-10} &\\ \leftarrow \operatorname{TxC}_{-10} &\\\operatorname{TxD}_{-10} &\end{array}$                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Rst# $\rightarrow$ TCT System<br>T1 $\rightarrow$<br>T2 $\rightarrow$<br>T3 $\rightarrow$ Test<br>T4 $\rightarrow$<br>T5 $\rightarrow$ | Receive<br>10-Mbit/s<br>Endec<br>10-Mbit/s<br>Control                 | $\begin{array}{ccc} -\mathrm{TxEn_10} & \longrightarrow \\ \leftarrow \mathrm{CrS_10} & \longrightarrow \\ \leftarrow \mathrm{RxC_10} & \longrightarrow \\ \leftarrow \mathrm{RxD_10} & \longrightarrow \\ \leftarrow \mathrm{Link_10} & \longrightarrow \end{array}$ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $SCA \rightarrow$ $SCA2 \rightarrow$ $SCB2 \rightarrow$ $SCB2 \rightarrow$ $SO -$ $SI2 \rightarrow$ $SO2 -$ $STM \rightarrow$          | External<br>EEPROM/<br>ROM<br>External<br>CAM                         | ← PROM_DI —<br>— PROM_DO →<br>— PROM_CIk →<br>— PROM_CS →<br>— CAM_load →<br>← CAM_hit# —                                                                                                                                                                             |

**Figure 2-1 External Signals**

### Peripheral Component Interconnect (PCI) Signals

Table 2-2 shows the 50 Peripheral Component Interconnect (PCI) signals for the TC35815CF Flow Control 10/100Mbps Ethernet Controller. These include the 49 signals required for a PCI master, plus the Interrupt A signal. The part drives sustained tristate signals high for one clock before returning them to the high-impedance state. Signals whose symbols end in "#" are active-low signals. All signals are referenced to the rising edge of Clk, except SErr#, Rst# and IntA#. The SErr# signal is asserted synchronous, and deasserted asynchronous to the Clk.

| Function             | Symbol     | Name                         | Туре                   | Master          | Target           | Clock domain     |

|----------------------|------------|------------------------------|------------------------|-----------------|------------------|------------------|

| Address and data     | AD[31:0]   | Address and data bus         | Tri-state              | In/Out          | In/Out           | PCI clock        |

|                      | C_BE#[3:0] | Command and byte enable bus  | Tri-state              | Out             | In               | PCI clock        |

|                      | Par        | Parity                       | Tri-state              | In/Out          | In/Out           | PCI clock        |

| Interface<br>control | Frame#     | Cycle frame                  | Sustained<br>tri-state | Out             | In               | PCI clock        |

|                      | TRdy#      | Target ready                 | Sustained<br>tri-state | In              | Out              | PCI clock        |

|                      | IRdy#      | Initiator ready              | Sustained<br>tri-state | Out             | In               | PCI clock        |

|                      | Stop#      | Stop                         | Sustained<br>tri-state | In              | Out              | PCI clock        |

|                      | DevSel#    | Device select                | Sustained<br>tri-state | In              | Out              | PCI clock        |

|                      | IDSel      | Initialization device select | Input                  |                 | In               | PCI clock        |

| Arbitration          | Gnt#       | Grant                        | Input <sup>a</sup>     | In              |                  | PCI clock        |

|                      | Req#       | Request                      | Tri-state              | Out             |                  | PCI clock        |

| Error<br>reporting   | PErr#      | Parity error                 | Sustained<br>tri-state | In/Out          | In/Out           | PCI clock        |

|                      | SErr#      | System error                 | Open drain             | In <sup>b</sup> | Out <sup>c</sup> | PCI clock/Asynch |

| Interrupt            | IntA#      | Interrupt A                  | Open drain             | Out             | Out              | Asynchronous     |

| System               | Clk        | PCI clock                    | Input                  | In              | In               | PCI clock        |

|                      | Rst#       | Reset                        | Input                  | In              | In               | Asynchronous     |

Table 2-2 Peripheral Component Interconnect (PCI) Signals

a. Gnt# is a point-to-point signal. The PCI Specification specifies the use of a tri-state driver.

b. In master mode, the controller does not signal SErr#, but monitors it as an input.

c. In slave mode, the controller signals SErr# for address parity errors.

### **PCI Address and Data Signals**

#### AD[31:0]

Address and data bus Carries address information during the address phase, and data during the data phase.

#### C\_BE#[3:0]

Command and byte enable

During the address phase, C\_BE#[3:0] defines the type of transaction, and during the data phase, it indicates the validity of bytes carried on AD[31:0]. Table 2-3 shows the correspondence between the byte-enable signals and bytes on the address and data bus during the data phase.

#### Table 2-3 Correspondence Between C\_BE#[3:0] and AD[31:0]

|                     | Address and data bus AD[31:0] |    |    |    |    |    |    |    |    |    |    |      |      |    |    |    |    |    |     |      |      |     |   |   |   |   |   |   |   |   |   |

|---------------------|-------------------------------|----|----|----|----|----|----|----|----|----|----|------|------|----|----|----|----|----|-----|------|------|-----|---|---|---|---|---|---|---|---|---|

| 31                  | 30                            | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19   | 18   | 17 | 16 | 15 | 14 | 13 | 12  | 11   | 10   | 9   | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Byte 3 (MSB) Byte 2 |                               |    |    |    |    |    |    |    |    |    |    | Byte | 1    |    |    |    |    |    | Byt | te 0 | (LS  | SB) |   |   |   |   |   |   |   |   |   |

| C_BE#[3] C_BE#[2]   |                               |    |    |    |    |    |    |    |    |    | C  | L_BE | #[1] |    |    |    |    |    | С   | _B   | Ξ#[( | )]  |   |   |   |   |   |   |   |   |   |

#### Table 2-4 Big Endian Byte Order

|                     | Address and data bus AD[31:0] |    |    |    |    |    |    |    |    |    |    |      |      |    |    |    |    |    |    |      |      |    |   |   |   |   |   |   |   |   |   |

|---------------------|-------------------------------|----|----|----|----|----|----|----|----|----|----|------|------|----|----|----|----|----|----|------|------|----|---|---|---|---|---|---|---|---|---|

| 31                  | 30                            | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19   | 18   | 17 | 16 | 15 | 14 | 13 | 12 | 11   | 10   | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Byte 0 (MSB) Byte 1 |                               |    |    |    |    |    |    |    |    |    |    | Byte | 2    |    |    |    |    |    | By | te 3 | (LS  | B) |   |   |   |   |   |   |   |   |   |

|                     | C_BE#[3] C_BE#[2]             |    |    |    |    |    |    |    |    |    | C  | _BE  | #[1] |    |    |    |    |    | C  | C_BE | E#[C | )] |   |   |   |   |   |   |   |   |   |

Table 2-4 shows the byte ordering of data when Big Endian is enabled.

#### Par

#### Parity

Provides even parity for the information carried on AD[31:0] and C\_BE#[3:0], by causing AD[31:0], C\_BE#[3:0], and Par to contain an even number of bits equal to one. The Par signal is active during the clock period after AD and C\_BE# contain valid data.

### **PCI Control Signals**

#### Frame#

#### Cycle frame

Driven by the current master to signal how long an access lasts. In a bus transaction terminated by the master, the master asserts Frame# beginning with the first or address cycle, and holding it until the next to last cycle, when it deasserts it. (See the STOP# signal for a description of target abort.)

#### TRdy#

Target ready

During a read, the target asserts TRdy# to indicate that it is driving valid data on AD[31:0]. During a write, the target asserts TRdy# to indicate it is ready to receive data over AD[31:0]. A data transfer occurs in a cycle when both TRdy# and IRdy# are asserted.

#### IRdy#

Initiator ready

During a read, the initiator asserts IRdy# to indicate that it is ready to receive data on AD[31:0]. During a write, the initiator asserts IRdy# to indicate it is driving valid data over AD[31:0]. A data transfer occurs in a cycle when both TRdy# and IRdy# are asserted.

#### Stop#

#### Stop#

The target asserts Stop# to request that the master terminate or abort the current transaction.

#### DevSel#

Device select

Driven by the target to confirm that it has decoded the address as referring to itself.

#### IDSel

Initialization device select

Equivalent to chip select, IDSel is a fully-decoded addressing mechanism for configuration read and write transactions.

### **PCI Bus Arbitration Signals**

#### Gnt#

#### Grant

A point-to-point signal from the arbiter to an agent, signalling to the agent that the arbiter has granted it bus ownership.

#### Req#

Request

A point-to-point signal from an agent to the arbiter, signalling to the arbiter that

the agent desires bus ownership. In normal operation, Req#, is an output, but during reset it enters a high-impedance state.

### **PCI Error Signals**

#### PErr#

#### Parity error

Kept at a high-impedance state, unless an agent receives non-Special Cycle data with a parity error, in which case it asserts PErr# two clocks later, and then, as with all sustained tri-state signals (unlike SErr#), drives it high for one clock before returning to the high-impedance state.

#### SErr#

System error

The SErr# signal is used to signal parity errors during an address cycle of a bus transaction, and all errors other than parity errors.

#### **PCI Interrupt Signal**

#### IntA#

Interrupt A Requests an interrupt.

#### **PCI System Signals**

#### Clk

#### Clock

All inputs are sampled on rising edge of clock. The controller supports 100 Mbps Ethernet when operating at 16-33MHz frequency operation. May be held low at any time, to conserve power. May only be stopped in a low state.

#### Rst#

#### Reset

Causes all output signals to enter a high-impedance state, and clears all registers. Does not affect on-chip RAM or FIFOs. Upon deassertion, the software drivers are responsible to check for the presence of a serial ROM, and if present, to read in the station address, and other configuration parameters.

### Media Independent Interface (MII) Signals

The MII is the interface between the TC35815CF Flow Control 10/100Mbps Ethernet Controller and the Physical Layer (PHY).

#### **Transmit MII Signals**

Table 2-5 shows the MII signals supported by the TC35815CF Flow Control 10/ 100Mbps Ethernet Controller for transmitting packets. For a detailed description of these signals, see the MII sections of the 802.3u documents listed in the "Reference Documents" section.