# Low Profile Receiver Module

### **FEATURES**

- 1.5 µW optical sensitivity using 100/140 micron fiber

- Designed to operate with HFM2010 fiber optic transmitters

- SMA interface

- Standard TTL interface

- Low profile package only 0.32 in. high

- Signal quality latch designates module operation

- Case operating temperature range from -55 to +100°C

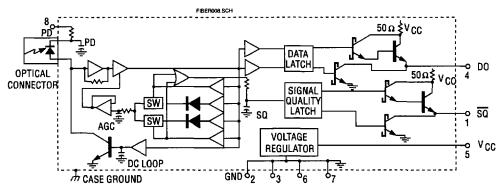

The HFM1011 fiber optic receiver module is designed for point-to-point digital data transmission. This low profile module converts bilevel or trilevel optical signals into a TTL level output.

The module contains an AC coupled bipolar MASTERSLICE IC and PIN photodiode. It requires periodic signal transitions such as those supplied by the trilevel transmitter module HFM2010. Internal voltage regulation allows adjustment-free operation over the full operating temperature range without external power supply filtering.

## **APPLICATION**

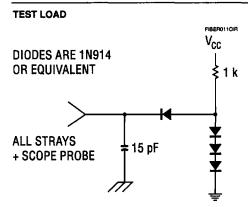

The HFM1011 receiver may be used with the trilevel HFM2010 transmitter for up to 10 Mbps data transmission. Light falls directly on the PIN photodiode. It drives a transimpedance pre-amp which uses a direct coupled (DC) feedback loop to soak up the DC component of the photodiode current.

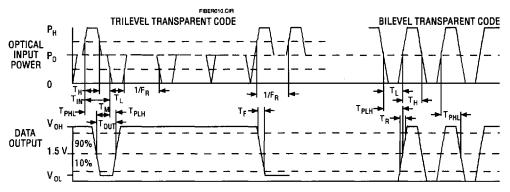

The AGC (automatic gain control) post-amp output constant amplitude peaks are averaged by a DC loop capacitor. The capacitor also AC couples the combination amplifier. A pair of comparators sets a positive and negative threshold with respect to the average value of the input signal. Their latched outputs reconstruct pulse widths from the trilevel transparent code. For bilevel code, the latch output follows the signal transitions.

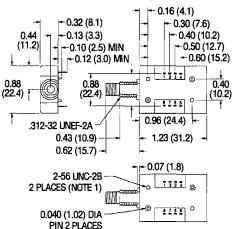

# **OUTLINE DIMENSIONS in inches (mm)**

# FIBER025 DIM

### Pinout

- 1. SQ signal quality

- 2. G ground

- G ground

- 4. DO output

- 5. V Vcc

- 6. G ground

- 7. G ground

- 8. PD photodiode bias

## Low Profile Receiver Module

## **APPLICATION** (continued)

The Signal Quality output derives its input from the comparators, which allow the peak detectors to keep the AGC capacitor charged to maintain correct post-amp gain. Signal peaks of either polarity cause the SQ capacitor to discharge, keeping SQ latch reset (SQ output low). Failure of both peaks to keep the SQ capacitor discharged results in a time out, and sets the SQ latch (SQ output high) to indicate a bad input signal. The AGC capacitor is also discharged, increasing the post-amp gain.

Power up requires 25 ms. An additional 10 ms is necessary following initial light input to the receiver. If a bilevel optical signal is used, it must have a 50% duty cycle with pulse widths as given in RECOMMENDED OPERATING CONDITIONS.

#### Notes

- Penetration greater than 0.09 in. (2.3 mm) into tapped holes may damage the module.

- Leads (pins 1 to 8) are 0.01 in. (0.25 mm) x 0.02 in. (0.50 mm).

- 3. Data Output and SQ Output are bipolar TTL type outputs.

- To keep SQ Output low, input transitions must occur at least every 1/fR period (refresh pulses).

- PD (pin 8) may be used to monitor photodiode current during testing. It must be connected to V<sub>CC</sub> (pin 5) or seperate 5 V supply for proper module operation.

# Low Profile Receiver Module

ELECTRO-OPTICAL CHARACTERISTICS (Values shown apply over ranges given in RECOMMENDED OPERATING CONDITIONS unless otherwise stated.)

| PARAMETER                       | SYMBOL                         | MIN | TYP   | MAX  | UNITS | TEST CONDITIONS                                         |

|---------------------------------|--------------------------------|-----|-------|------|-------|---------------------------------------------------------|

| High Level Logic Output Voltage | Vрон                           | 2.4 | 3.7   |      | V     | looн = Isoн = -400 µA,                                  |

|                                 | Vson                           | 2.4 | 3.7   | -    | V     | P <sub>H</sub> = 0 μW                                   |

| Low Level Logic Output Voltage  | VDOL                           |     | 0.2   | 0.4  | [ V   | $l_{DOL} = l_{SOL} = 4 \text{ mA},$                     |

|                                 | VsoL                           |     | 0.2   | 0.4  | v     | P <sub>H</sub> > 3 μW                                   |

| Supply Current                  | lcc                            |     | 35    | 60   | mA    | P <sub>H</sub> = 0 μW                                   |

| Output Short Circuit Current    | losc                           | -30 | -80   | -140 | mA    | $P_{H} = 0 \mu W^{(1)}$                                 |

| Transition Time                 | t <sub>r</sub> /t <sub>f</sub> |     | . 7   | 11   | ns    | $P_H > 3 \mu W$ , optical $t_r/t_f$                     |

|                                 |                                |     | ٠     | i    |       | < 25 ns, 10 Mbps                                        |

| Propagation Delay               | t <sub>PHL</sub>               | 38  | 62    | 100  | ns    | $P_H > 3 \mu W$ , optical $t_r/t_f$                     |

|                                 | tецн                           | 38  | 62    | 100  | ns    | < 25 ns, 10 Mbps                                        |

| Pulse Width Distortion          | PWD                            |     | 1     | 15   | %     | PH > 3 $\mu$ W, (tin - tout)/tin,                       |

| Program Strain                  |                                |     | 8. E. |      |       | optical t <sub>r</sub> /t <sub>r</sub> < 25 ns, 10 Mbps |

| Edge Jitter (RMS)               |                                |     | 1.3   | 2.5  | ns    | P <sub>H</sub> > 3 μW, optical                          |

|                                 |                                |     |       |      | Į l   | $t_r/t_f < 25$ ns, 10 Mbps                              |

| Input Sensitivity (2)           | PINBER                         | : . | 0.5   | 1.5  | μW    | BER≤10-9 (4) (5)                                        |

|                                 | Pinso                          | 0.2 | 0.4   | 0.8  | μW    | SQ Low Threshold                                        |

#### Notes

- 1. lose flows during momentary connection of DO (pin 4) to GND while DO is at VoH.

- 2. For typical values, Vcc= 5 volts and TAMB= 25°C.

- 3. K= (P<sub>H</sub> P<sub>O</sub>)/P<sub>O</sub> is a measure of the difference in amplitude for trilevel pulses.

- 4. Max edge jitter specified corresponds to a normalized Bit Error Rate (BER) of 10<sup>-9</sup> if the output is strobed with an ideally phased jitter-free clock. BER is guaranteed, but not normally tested.

- 5. Minimum Po for operation should be 2 dB higher than the rated Po of the part when refresh pulses only are present,

## **ABSOLUTE MAXIMUM RATINGS**

(25°C Free-Air Temperature unless otherwise noted)

Storage temperature -65 to +150°C

Case operating temperature -55 to +100°C

Lead solder temperature 260°C, 10 s

Supply voltage -0.5 to +7 V

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

## RECOMMENDED OPERATING CONDITIONS

Case operating temperature  $-55 \text{ to } +100^{\circ}\text{C}$  Supply voltage  $+5 \pm 10\% \text{ V}$  Average optical input power  $1.5 \text{ to } 200 \text{ } \mu\text{W}$  Optical input pulse width,  $t_L$  or  $t_H$  40 to 600 ns Refresh repetition rate,  $f_R$  1.0 Mbps Amplitude symmetry ratio, k 0.8 to 1.2  $^{(3)}$

# **Low Profile Receiver Module**

| ORDER GUIDE                                        |                 |  |  |  |  |

|----------------------------------------------------|-----------------|--|--|--|--|

| Description                                        | Catalog Listing |  |  |  |  |

| Standard low profile module, SMA optical connector | HFM1011-222     |  |  |  |  |

### FIBER INTERFACE

Honeywell detectors are designed to interface with multimode fibers with sizes (core/cladding diameters) ranging from 50/125 to 200/230 microns. Honeywell performs final tests using 100/140 micron core fiber.

## CAUTION

The inherent design of this component causes it to be sensitive to electrostatic discharge (ESD). To prevent ESD-induced damage and/or degradation to equipment, take normal ESD precautions when handling this product.

### **BLOCK DIAGRAM**

## **DECODING AND TIMING DIAGRAM**

# **Low Profile Receiver Module**