# **Radiation Hardened Ultra Low Noise, Precision Voltage** Reference

## ISL71090SEH12

The ISL71090SEH12 is an ultra low noise, high DC accuracy precision voltage reference with a wide input voltage range from 4V to 30V. The ISL71090SEH12 uses the Intersil Advanced Bipolar technology to achieve sub  $2\mu V_{P-P}$  noise at 0.1Hz with an accuracy over temperature and radiation of 0.15%.

The ISL71090SEH12 offers a 1.25V output voltage with 10ppm/°C temperature coefficient and also provides excellent line and load regulation. The device is offered in an 8 Ld Flatpack package.

The ISL71090SEH12 is ideal for high-end instrumentation, data acquisition and applications requiring high DC precision where low noise performance is critical.

## **Applications**

- · RH voltage regulators precision outputs

- · Precision voltage sources for data acquisition system for space applications

- · Strain and pressure gauge for space applications

## **Features**

| • Reference output voltage1.25V ±0.05%                      |

|-------------------------------------------------------------|

| Accuracy over temperature and radiation ±0.15%              |

| • Output voltage noise 1µ $V_{P\!-\!P}$ Typ (0.1Hz to 10Hz) |

| • Supply current                                            |

| • Tempco (box method) 10ppm/ °C Max                         |

| Output current capability 20mA                              |

| • Line regulation                                           |

| • Load regulation                                           |

| • Operating temperature range55°C to +125°C                 |

| Radiation environment                                       |

| - High dose rate (50-300rad(Si)/s)100krad(Si)               |

| - Low dose rate (0.01rad(Si)/s)100krad(Si)*                 |

| - SET/SEL/SEB86MeV•cm <sup>2</sup> /mg                      |

<sup>\*</sup>Product capability established by initial characterization. The "EH" version is acceptance tested on a wafer by wafer basis to 50krad(Si) at low dose rate

• Electrically screened to SMD 5962-13211

## **Related Literature**

- AN1862, "ISL71090SEH12 Evaluation Board User's Guide"

- AN1863, "SEE Testing of the ISL71090SEH12"

- AN1864, "Radiation Report of the ISL71090SEH12"

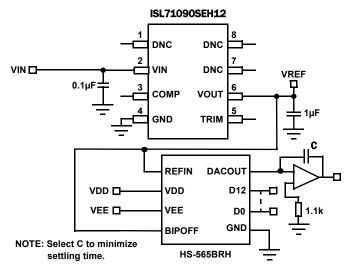

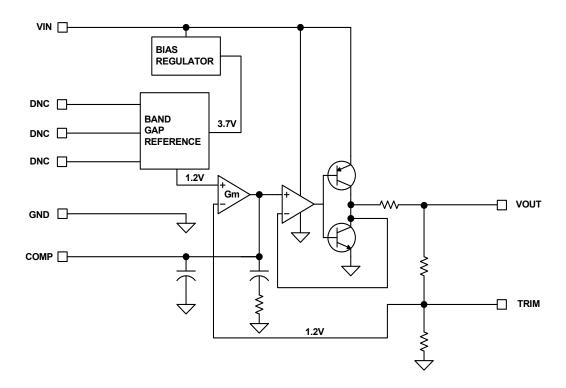

FIGURE 1. ISL71090SEH12 TYPICAL APPLICATION DIAGRAM

1

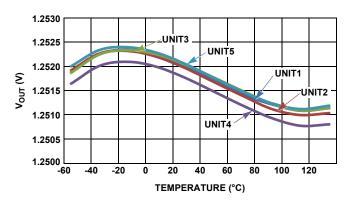

FIGURE 2.  $V_{OUT}$  vs TEMPERATURE

## **Ordering Information**

| ORDERING NUMBER<br>(Notes 1, 2, 3) | PART<br>NUMBER       | V <sub>OUT</sub> OPTION<br>(V) | TEMP RANGE (°C) | PACKAGE<br>TAPE & REEL<br>(Pb-Free) | PKG. DWG. # |

|------------------------------------|----------------------|--------------------------------|-----------------|-------------------------------------|-------------|

| 5962R1321101VXC                    | ISL71090SEHVF12      | 1.25                           | -55 to +125     | 8 Ld Flatpack                       | K8.A        |

| ISL71090SEHF12/PROTO               | ISL71090SEHF12/PROTO | 1.25                           | -55 to +125     | 8 Ld Flatpack                       | K8.A        |

| ISL71090SEHF12EVAL1Z               | Evaluation Board     |                                |                 |                                     |             |

#### NOTES:

- 1. These Intersil Pb-free Hermetic packaged products employ 100% Au plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

- 2. For Moisture Sensitivity Level (MSL), please see device information page for <a href="ISL71090SEH12">ISL71090SEH12</a>. For more information on MSL please see tech brief TB363

- 3. Specifications for Rad Hard QML devices are controlled by the Defense Logistics Agency Land and Maritime (DLA). The SMD numbers listed in this "Ordering Information" table must be used when ordering.

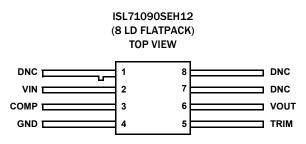

## **Pin Configuration**

# **Pin Descriptions**

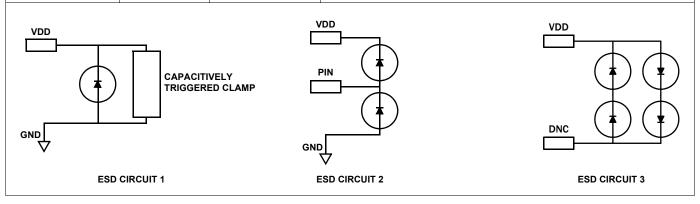

| PIN NUMBER | PIN NAME | ESD CIRCUIT | DESCRIPTION                                   |

|------------|----------|-------------|-----------------------------------------------|

| 1, 7, 8    | DNC      | 3           | Do not Connect. Internally terminated.        |

| 2          | VIN      | 1           | Input Voltage Connection                      |

| 3          | COMP     | 2           | Compensation and Noise Reduction Capacitor    |

| 4          | GND      | 1           | Ground Connection. Also connected to the lid. |

| 5          | TRIM     | 2           | Voltage Reference Trim input                  |

| 6          | VOUT     | 2           | Voltage Reference Output                      |

inter<sub>sil</sub>\*

# **Functional Block Diagram**

## ISL71090SEH12

## **Absolute Maximum Ratings**

| Max Voltage                                                       |

|-------------------------------------------------------------------|

| V <sub>IN</sub> to GND0.5V to +40V                                |

| $V_{IN}$ to GND at an LET = 86MeV·cm <sup>2</sup> /mg0.5V to +36V |

| V <sub>OUT</sub> to GND (10s)0.5V to V <sub>OUT</sub> + 0.5V      |

| Voltage on any Pin to Ground0.5V to +V <sub>OUT</sub> + 0.5V      |

| Voltage on DNC PinsNo connections permitted to these pins         |

| ESD Ratings                                                       |

| Human Body Model 2kV                                              |

| Machine Model                                                     |

| Charged Device Model                                              |

## **Thermal Information**

| Thermal Resistance (Typical)                      | $\theta_{JA}(^{\circC/W})$ | $\theta_{JC}$ (°C/W) |

|---------------------------------------------------|----------------------------|----------------------|

| 8 Ld Flatpack Package (Notes 4, 5)                | 140                        | 15                   |

| Storage Temperature Range                         | 6                          | 5°C to +150°C        |

| Maximum Junction Temperature (T <sub>JMAX</sub> ) |                            | +150°C               |

| Pb-Free Reflow Profile (Note 6)                   |                            | . see link below     |

| http://www.intersil.com/pbfree/Pb-FreeRe          | eflow.asp                  |                      |

## **Recommended Operating Conditions**

| V <sub>IN</sub>   | <br>4.0V to +30V   |

|-------------------|--------------------|

| Temperature Range | <br>55°C to +125°C |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 4. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief <u>TB379</u> for details.

- 5. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the ceramic on the package underside.

- 6. Post-reflow drift for the ISL71090SEH12 devices can be 100µV typical based on experimental results with devices on FR4 double sided boards. The engineer must take this into account when considering the reference voltage after assembly.

- 7. Product capability established by initial characterization. The "EH" version is acceptance tested on a wafer by wafer basis to 50krad(Si) at low dose rate.

- 8. The output capacitance used for SEE testing is  $C_{IN}$  = 0.1 $\mu$ F and  $C_{OUT}$  = 1 $\mu$ F.

# **Electrical Specifications** $V_{IN} = 5V$ , $I_{OUT} = 0$ , $C_L = 0.1\mu$ F and $C_C = 0.01\mu$ F unless otherwise specified. **Boldface limits apply over the operating temperature range, -55°C to +125°C.**

| PARAMETER                       | DESCRIPTION                                                  | CONDITIONS                                                                            | MIN<br>(Note 9) | TYP   | MAX<br>(Note 9) | UNIT              |

|---------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------|-------|-----------------|-------------------|

| V <sub>out</sub>                | Output Voltage                                               | V <sub>IN</sub> = 5V                                                                  |                 | 1.252 |                 | V                 |

| V <sub>OA</sub>                 | V <sub>OUT</sub> Accuracy @ T <sub>A</sub> = +25°C (Note 6)  | V <sub>OUT</sub> = 1.25V                                                              | -0.05           |       | +0.05           | %                 |

| V <sub>OA</sub>                 | V <sub>OUT</sub> Accuracy @ T <sub>A</sub> = -55°C to +125°C | V <sub>OUT</sub> = 1.25V                                                              | -0.15           |       | +0.15           | %                 |

| TC V <sub>OUT</sub>             | Output Voltage Temperature<br>Coefficient (Note 11)          |                                                                                       |                 |       | 10              | ppm/°C            |

| V <sub>IN</sub>                 | Input Voltage Range (Note 10)                                | V <sub>OUT</sub> = 1.25V                                                              | 4.0             |       | 30              | V                 |

| I <sub>IN</sub>                 | Supply Current                                               |                                                                                       |                 | 0.930 | 1.28            | mA                |

| $\Delta V_{OUT}/\Delta V_{IN}$  | Line Regulation                                              | V <sub>IN</sub> = 4.0V to 30V, V <sub>OUT</sub> = 1.25V                               |                 | 8     | 18              | ppm/V             |

| $\Delta V_{OUT}/\Delta I_{OUT}$ | Load Regulation                                              | Sourcing: 0mA ≤ I <sub>OUT</sub> ≤ 20mA                                               |                 | 35    | 55              | ppm/mA            |

| $V_D$                           | Dropout Voltage<br>(Note 10)                                 | V <sub>OUT</sub> = 1.25V @ 10mA                                                       |                 | 1.7   | 2.25            | V                 |

| I <sub>SC+</sub>                | Short Circuit Current                                        | T <sub>A</sub> = +25 °C, V <sub>OUT</sub> tied to GND                                 |                 | 53    |                 | mA                |

| I <sub>SC-</sub>                | Short Circuit Current                                        | T <sub>A</sub> = +25 °C, V <sub>OUT</sub> tied to V <sub>IN</sub>                     |                 | -23   |                 | mA                |

| t <sub>R</sub>                  | Turn-on Settling Time                                        | 90% of final value, $C_L = 1.0 \mu F$ , $C_C = open$                                  |                 | 250   |                 | μs                |

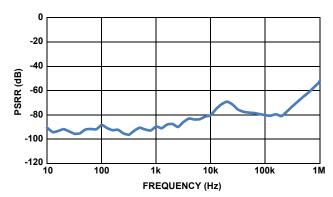

| PSRR                            | Ripple Rejection                                             | f = 120Hz                                                                             |                 | 90    |                 | dB                |

| e <sub>N</sub>                  | Output Voltage Noise                                         | $0.1 \text{Hz} \leq \text{f} \leq \text{10Hz},  \text{V}_{\text{OUT}} = \text{1.25V}$ |                 | 1.0   |                 | μV <sub>P-P</sub> |

| $V_N$                           | Broadband Voltage Noise                                      | <b>10Hz</b> $\leq$ <b>1</b> kHz, $V_{OUT}$ = <b>1.25</b> V                            |                 | 1.2   |                 | μV <sub>RMS</sub> |

|                                 | Noise Density                                                | f = 1kHz, V <sub>OUT</sub> = 1.25V, V <sub>IN</sub> = 6V                              |                 | 21    |                 | nV/√Hz            |

| $\Delta V_{OUT}/\Delta t$       | Long Term Drift                                              | T <sub>A</sub> = 125 °C, 1000hrs                                                      |                 | 15    |                 | ppm               |

#### NOTES:

- 9. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 10. V<sub>IN</sub>-V<sub>OUT</sub> measured at the point where V<sub>OUT</sub> drops 1mV from the nominal measured value.

- 11. Over the specified temperature range. Temperature coefficient is measured by the box method whereby the change in V<sub>OUT(max)</sub> V<sub>OUT(min)</sub> is divided by the temperature range; in this case, -55 °C to +125 °C = +180 °C.

- 12. Dropout Voltage is the minimum  $V_{IN}$   $V_{OUT}$  differential voltage measured at the point where  $V_{OUT}$  drops 1mV from  $V_{IN}$  = nominal at  $T_A$  = +25 °C.

FN8452.0

June 26, 2013

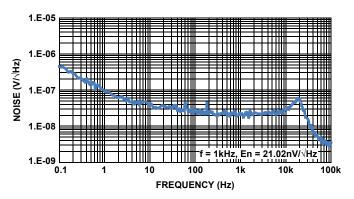

## Typical Performance Curves $v_{IN} = 5V$ , $v_{OUT} = 1.25V$ , $T_A = +25$ °C, unless otherwise specified.

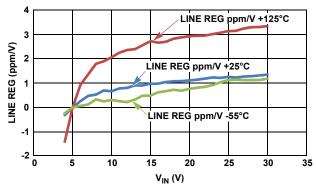

FIGURE 3. LINE REGULATION OVER TEMPERATURE (0mA)

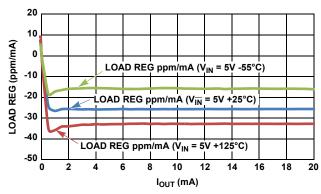

FIGURE 4. LOAD REGULATION OVER TEMPERATURE AT  $V_{IN} = 5V$  (ppm/mA)

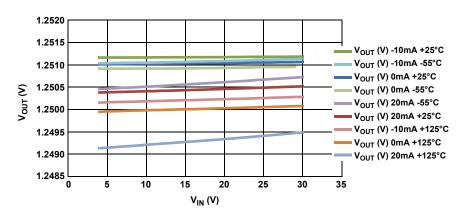

FIGURE 5. V<sub>OUT</sub> vs V<sub>IN</sub> AT 0mA, 20mA AND -10mA

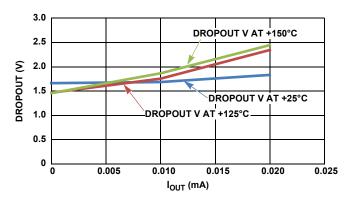

FIGURE 6. DROPOUT VOLTAGE FOR 1.25V

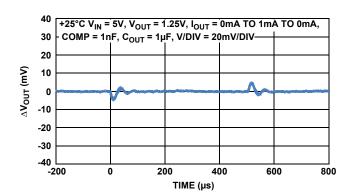

FIGURE 7. LOAD TRANSIENT (0mA TO 1mA)

## Typical Performance Curves $v_{IN}$ = 5V, $v_{OUT}$ = 1.25V, $T_A$ = +25°C, unless otherwise specified. (Continued)

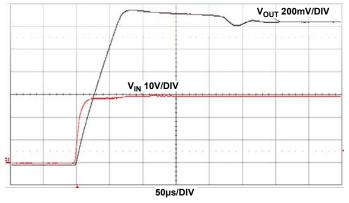

FIGURE 8. TURN-ON SETTLING TIME

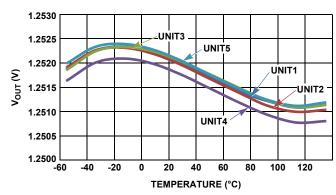

FIGURE 9. TYPICAL TEMPERATURE COEFFICIENT PLOT FOR 5 UNITS

FIGURE 10. NOISE DENSITY vs FREQUENCY (V<sub>IN</sub> = 6V, RI = OPEN)

$\begin{aligned} \text{FIGURE 11. PSRR (+25\,^{\circ}\text{C}, V_{\text{IN}} = 5\text{V}, V_{\text{OUT}} = 1.25\text{V}, I_{\text{OUT}} = 0\text{mA},} \\ C_{\text{IN}} &= 0.1\mu\text{F}, C_{\text{OUT}} = 1\mu\text{F}, \text{COMP} = 1\text{nF}, V_{\text{SIG}} = 300\text{mV}_{\text{P-P}}) \end{aligned}$

## **Device Operation**

### **Bandgap Precision Reference**

The ISL71090SEH12 uses a bandgap architecture and special trimming circuitry to produce a temperature compensated, precision voltage reference with high input voltage capability and moderate output current drive.

## **Applications Information**

## **Board Mounting Considerations**

For applications requiring the highest accuracy, board mounting location should be reviewed. The device uses a ceramic flatpack package. Generally, mild stresses to the die when the printed circuit (PC) board is heated and cooled, can slightly change the shape. Because of these die stresses, placing the device in areas subject to slight twisting can cause degradation of reference voltage accuracy. It is normally best to place the device near the edge of a board, or on the shortest side, because the axis of bending is most limited in that location. Mounting the device in a cutout also minimizes flex. Obviously, mounting the device on flexprint or extremely thin PC material will likewise cause loss of reference accuracy.

## **Board Assembly Considerations**

Some PC board assembly precautions are necessary. Normal output voltage shifts of typically 100 $\mu$ V can be expected with Pb-free reflow profiles or wave solder on multi-layer FR4 PC boards. Precautions should be taken to avoid excessive heat or extended exposure to high reflow or wave solder temperatures.

#### **Noise Performance and Reduction**

The output noise voltage over the 0.1Hz to 10Hz bandwidth is typically  $2\mu V_{P\text{-P}}$  ( $V_{OUT}$  = 1.25V). The noise measurement is made with a 9.9Hz bandpass filter. Noise in the 10Hz to 1kHz bandwidth is approximately 1.6 $\mu V_{RMS}$  ( $V_{OUT}$  = 1.25V), with 0.1 $\mu F$  capacitance on the output. This noise measurement is made with a band pass filter of 990Hz. Load capacitance up to 10 $\mu F$  (with COMP) can be added but will result in only marginal improvements in output noise and transient response.

#### **Turn-On Time**

Normal turn-on time is typically 250µs, the circuit designer must take this into account when looking at power-up delays or sequencing.

#### **Temperature Coefficient**

The limits stated for temperature coefficient (Tempco) are governed by the method of measurement. The overwhelming standard for specifying the temperature drift of a reference is to measure the reference voltage at two temperatures which provide for the maximum voltage deviation and take the total variation,  $(V_{HIGH} - V_{LOW}),$  this is then divided by the temperature extremes of measurement  $(T_{HIGH} - T_{LOW}).$  The result is divided by the nominal reference voltage (at T = +25  $^{\circ}$ C) and multiplied by  $10^{6}$  to yield ppm/  $^{\circ}$ C. This is the "Box" method for specifying temperature coefficient.

### **Output Voltage Adjustment**

The output voltage can be adjusted above and below the factory-calibrated value via the trim terminal. The trim terminal is the negative feedback divider point of the output op amp. The positive input of the amplifier is about 1.216V, and in feedback, so will be the trim voltage. The suggested method to adjust the output is to connect a  $1M\Omega$  external resistor directly to the trim terminal and connect the other end to the wiper of a potentiometer that has a  $100k\Omega$  resistance and whose outer terminals connect to  $V_{OUT}$  and ground. If a  $1M\Omega$  resistor is connected to trim, the output adjust range will be ±6.3mV. The TRIM pin should not have any capacitor tied to its output, also it is important to minimize the capacitance on the trim terminal during layout to preserve output amplifier stability. It is also best to connect the series resistor directly to the trim terminal, to minimize that capacitance and also to minimize noise injection. Small trim adjustments will not disturb the factory-set temperature coefficient of the reference, but trimming near the extreme values can.

### **Output Stage**

The output stage of the device has a push pull configuration with an high side PNP and a low side NPN. This helps the device to act as a source and sink. The device can source 20mA.

### **Use of COMP Cap**

The reference can be compensated for the  $C_{OUT}$  capacitors used by adding a capacitor from COMP pin to GND. See Table 1 for recommended values. of the COMP capacitor.

TABLE 1.

| С <sub>ОИТ</sub><br>(µF) | C <sub>COMP</sub><br>(nF) |

|--------------------------|---------------------------|

| 0.1                      | 1                         |

| 1                        | 1                         |

| 10                       | 10                        |

#### **SEE Testing**

The device was tested under ion beam at an LET of 86MeV • cm²/mg. The device did not latch up or burn out to a VDD of 36V and at +125°C. Single Event transients were observed and are summarized in the Table 2:

TABLE 2.

| V <sub>IN</sub> (V) | I <sub>ОИТ</sub><br>(mA) | C <sub>OUT</sub><br>(µF) | SET<br>(% V <sub>OUT</sub> ) |

|---------------------|--------------------------|--------------------------|------------------------------|

| 4                   | 5                        | 1                        | -4.6                         |

| 30                  | 5                        | 1                        | -4.4                         |

| 30                  | 5                        | 10                       | -1.0                         |

#### **DNC Pins**

These pins are for trimming purpose and for factory use only. Do not connect these to the circuit in any way. It will adversely effect the performance of the reference.

## **Package Characteristics**

## **Weight of Packaged Device**

0. 31 Grams (Typical)

### **Lid Characteristics**

Finish: Gold

Potential: Connected to lead #4 (GND) Case Isolation to Any Lead: 20 x 10<sup>9</sup>  $\Omega$  (min)

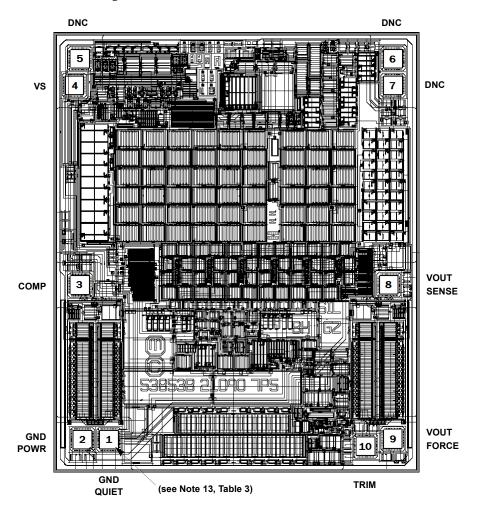

## **Die Characteristics**

### **Die Dimensions**

1464 $\mu$ m x 1744 $\mu$ m (58mils x 69mils) Thickness: 483 $\mu$ m  $\pm$  25 $\mu$ m (19mils  $\pm$  1 mil)

#### **Interface Materials**

#### **GLASSIVATION**

Type: Nitrox Thickness: 15kÅ

#### **TOP METALLIZATION**

Type: AlCu (99.5%/0.5%) Thickness: 30kÅ

#### **BACKSIDE FINISH**

Silicon

### **ASSEMBLY RELATED INFORMATION**

#### **SUBSTRATE POTENTIAL**

**Floating**

### **ADDITIONAL INFORMATION**

#### **WORST CASE CURRENT DENSITY**

$<2 \times 10^5 \text{ A/cm}^2$

#### **PROCESS**

Dielectrically Isolated Advanced Bipolar Technology- PR40 SOI

## **Metallization Mask Layout**

## ISL71090SEH12

**TABLE 3. DIE LAYOUT X-Y COORDINATES**

| PAD NAME   | PIN NUMBER | X<br>(μm) | Υ<br>(μm) | BOND WIRES<br>PER PAD |

|------------|------------|-----------|-----------|-----------------------|

| GND PWR    | 4          | -104      | 0         | 1                     |

| GND QUIET  | 4          | 0         | 0         | 1                     |

| COMP       | 3          | -108      | 589       | 1                     |

| VS         | 2          | -125      | 1350      | 1                     |

| DNC        | 1          | -108      | 1452      | 1                     |

| DNC        | 8          | 1089      | 1452      | 1                     |

| DNC        | 7          | 1089      | 1350      | 1                     |

| VOUT SENSE | 6          | 1072      | 598       | 1                     |

| VOUT FORCE | 6          | 1088      | 1         | 1                     |

| TRIM       | 5          | 985       | -25       | 1                     |

#### NOTES:

- 13. Origin of coordinates is the centroid of GND QUIET.

- 14. Bond wire size is 1.0 mil.

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE          | REVISION | CHANGE           |

|---------------|----------|------------------|

| June 26, 2013 | FN8452.0 | Initial Release. |

## **About Intersil**

Intersil Corporation is a leader in the design and manufacture of high-performance analog, mixed-signal and power management semiconductors. The company's products address some of the largest markets within the industrial and infrastructure, personal computing and high-end consumer markets. For more information about Intersil, visit our website at <a href="https://www.intersil.com">www.intersil.com</a>.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com/en/support/ask-an-expert.html">www.intersil.com/en/support/ask-an-expert.html</a>. Reliability reports are also available from our website at <a href="https://www.intersil.com/en/support/qualandreliability.html#reliability">https://www.intersil.com/en/support/qualandreliability.html#reliability</a>

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

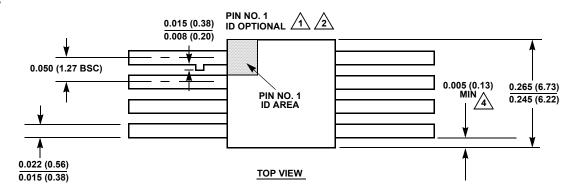

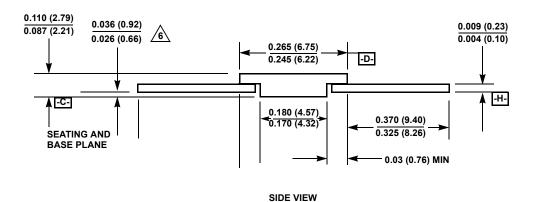

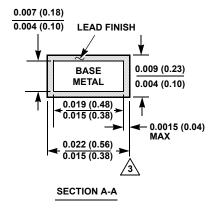

# **Package Outline Drawing**

#### **K8.A**

#### **8 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE**

Rev 3, 3/13

### NOTES:

1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark. Alternately, a tab may be used to identify pin one.

/2\f a pin one identification mark is used in addition to a tab, the limits of the tab dimension do not apply.

1/3. The maximum limits of lead dimensions (section A-A) shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

4. Measure dimension at all four corners.

5. For bottom-brazed lead packages, no organic or polymeric materials shall be molded to the bottom of the package to cover the leads.

6 Dimension shall be measured at the point of exit (beyond the meniscus) of the lead from the body. Dimension minimum shall be reduced by 0.0015 inch (0.038mm) maximum when solder dip lead finish is applied.

- 7. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 8. Controlling dimension: INCH.

intersil