### 1 Features Overview

- Integrated motor controller

- Full Bridge NFET predriver

- Double Charge pump with programmable NFET gate voltage

- HS NFET and Low Side NFET control

- Synchronous rectification with programmable dead time

- $_{\odot}$   $\,$  3 high voltage Wake up capable IO's on rising and falling edge

- $\circ$   $\,$  3 low voltage IO's with multiple configuration options

- Automotive Supply regulator

- Standard Operating range [7, 18]V, Tj=[-40, 125]C

- Extended operating range [4.5, 28]V, Tj = [-40, 150]C

- 45V Load dump protected

- Sleep current <50uA</li>

- Autosequence 10bit ADC with DMA avoids need for MCU interrupts to handle sampling. Multiple input channels

- Battery (VSUP) and motor supply (VDRAIN)

- Internal Temperature sensor (+/-15K)

- All IO's can be configured as analog inputs.

- Single shot NTC measurement with 3.3V ADC reference voltage.

- Low Side Shunt amplifier with

- Programmable gain,

- Programmable Overcurrent protection and Current limiting levels

- Synchronised measurements with programmable blanking time.

- 16bit Microcontroller

- Two 16 bit timers for PWM communication

- o 16 bit core timer

- o 512 Byte RAM

- 128 Byte data EEPROM

- 16kB OTP Program memory (Flash for engineering samples only).

- TSSOP28 exposed pad package

- AECQ100 automotive qualified, HTOL at Tj = 150C

### 2 Target Applications

- High current DC motor control applications with PWM communication interface.

- Fuel pumps

- HVAC Blowers

- $\circ$   $\;$  Engine cooling fans: dual and single fan control possible

### **3 Ordering Information**

| Part No. | Temperature Code     | Package Code    | Option Code |

|----------|----------------------|-----------------|-------------|

| MLX80153 | K (-40 to 125°C) (*) | GO (TSSOP28-EP) | AAA 000     |

| MLX80154 | Engineering samples  | (TSSOP28-EP)    |             |

(\*) operation up to Tj=150C possible after review of the mission profile.

**OTP Full Bridge motor controller**

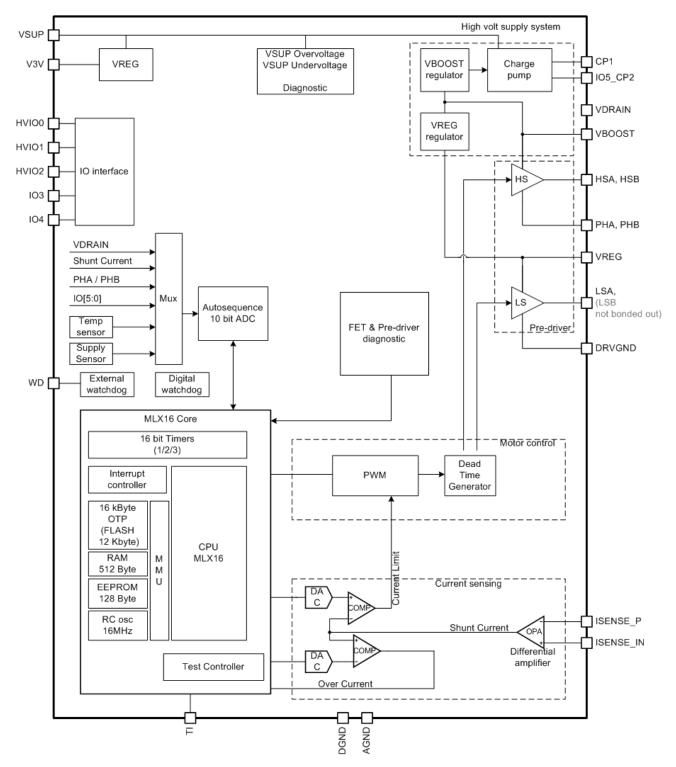

# 4 Block diagram

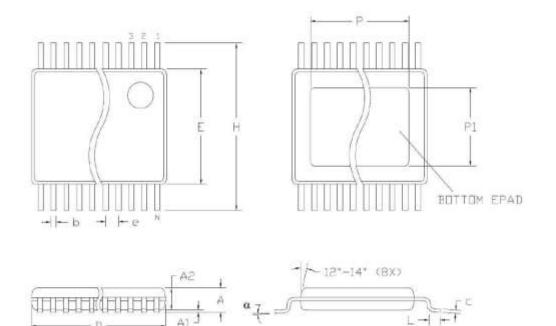

### 5 Package data: TSSOP28- exposed pad

|     | Α    | A1   | A2   | D    | E    | Н     | е     | L    | b    | С    | α  | Ρ     | P1    |

|-----|------|------|------|------|------|-------|-------|------|------|------|----|-------|-------|

| min |      | 0.05 | 0.85 | 9.60 | 4.30 | 6.4   | 0.65  | 0.5  | 0.19 | 0.09 | 0° | 3.00  | 5.50  |

| Max | 1.10 | 0.15 | 0.95 | 9.80 | 4.50 | B.S.C | B.S.C | 0.75 | 0.30 | 0.20 | 8° | B.S.C | B.S.C |

Table 1: Mechanical Dimensions TSSOP28\_EP, all dimensions in mm

Figure 1: Package dimensions in mm

# Abstract MLX80153

**OTP Full Bridge motor controller**

## 6 Pin out description MLX80153

| Pin<br>Number | Pin name<br>MLX80153<br>MLX80154 | remarks and description MLX80153                                                                                       |

|---------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 1             | HVIO2                            | High Voltage digital IO (-2V, +Vbat), analog input Wake up capable on rising edge.                                     |

| 2             | ISENSE_IN                        | Current Sense shunt, negative input                                                                                    |

| 3             | ISENSE_P                         | Current Sense shunt, positive input                                                                                    |

| 4             | AGND                             | Analog IC Ground                                                                                                       |

| 5             | WD                               | Watchdog input                                                                                                         |

| 6             | V3V                              | 3.3V regulated supply                                                                                                  |

| 7             | DGND                             | Digital IC Ground                                                                                                      |

| 8             | ТІ                               | Test input (connect to GND in application),<br>used for Flash/OTP programming and software debugging                   |

| 9             | n.c.                             | Not connected                                                                                                          |

| 10            | VDRAIN                           | High side VDS monitoring input                                                                                         |

| 11            | VBOOST                           | Charge pump voltage input                                                                                              |

| 12            | n.c.                             | Not connected                                                                                                          |

| 13            | PHB                              | Motor phase, (Sink output of HS driver)                                                                                |

| 14            | HSB                              | High side NFET driver                                                                                                  |

| 15            | PHA                              | Motor phase, (Sink output of HS driver)                                                                                |

| 16            | HSA                              | High side NFET driver                                                                                                  |

| 17            | VREG                             | Regulated supply voltage (used to drive NFETs)                                                                         |

| 18            | LSA                              | Low side NFET driver                                                                                                   |

| 19            | DRVGND                           | Ground for IC driver stage                                                                                             |

| 20            | CP1                              | 1 <sup>st</sup> stage Charge pump clock output                                                                         |

| 21            | IO5_CP2                          | 2 <sup>nd</sup> stage Charge pump clock output, or Low voltage IO5                                                     |

| 22            | n.c.                             | Not connected                                                                                                          |

| 23            | VSUP                             | Supply input (reverse polarity protection required)                                                                    |

| 24            | HVIO1                            | High Voltage digital IO (-2V, +Vbat), analog input<br>Wake up capable on rising edge.                                  |

| 25            | HVIO0                            | High Voltage digital IO (-2V, +Vbat)<br>Wake up capable on falling edge. Applicable for bidirectional<br>communication |

| 26            | n.c.                             | Not connected                                                                                                          |

| 27            | 103                              | Low Voltage digital IO (3.3V), analog input                                                                            |

| 28            | 104                              | Low Voltage digital IO (3.3V), analog input                                                                            |

Table 2: Pin out description

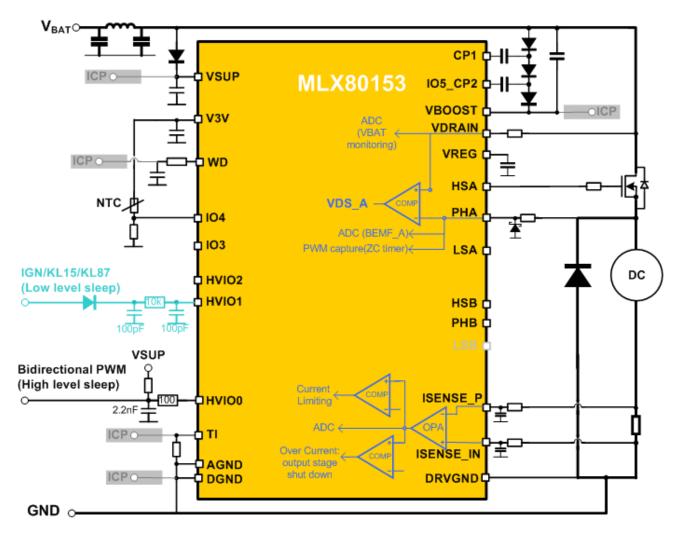

# 7 Application Schematic example

**NOTE:** Shown schematics are reference examples that give a realistic indication of typical external components. In actual applications additional components may be required, and component values will have to be revised.

#### 7.1 Basic pump / fan example

- Double charge pump allows controlling HS NFETs under low battery conditions.

- High side NFET VDS monitoring (programmable voltage levels and blanking time) protects for short circuits to ground.

- Phase voltage (BEMF) can be measured back via the phase pin.

- Applied Motor voltage is measured directly on the FET drains via VDRAIN pin.

- IC can wake up from either a falling or rising edge on one of its High Voltage inputs.

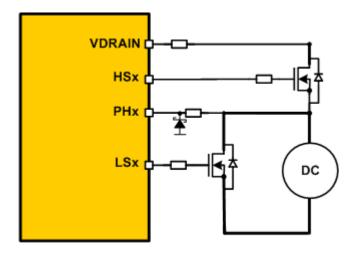

### 7.2 Freewheeling NFET control for reduced thermal dissipation

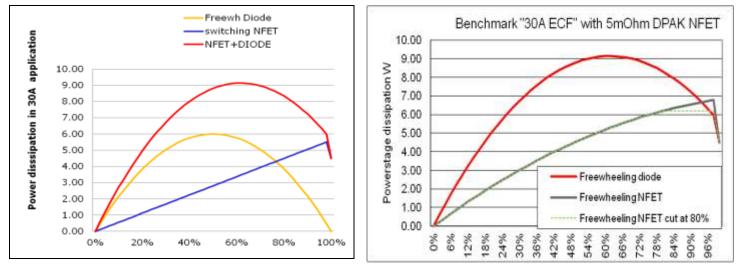

Applying a full NFET halfbridge allows extending the power range for thermally limited pcb designs by another 30% compared to designs with freewheeling diode. See below graphs.

Fig. 1: Contributions in power dissipation with Freewheeling Diode. Peak dissipation around 50% duty cycle

Fig. 2: Up to 30% lower peak dissipation with Freewheeling NFET. Peak dissipation at 80% duty cycle