# **ADS7800**

3μsec, 12-Bit SAMPLING A/D CONVERTER

#### **FEATURES**

- 333kHz Over Temperature

- ±5V and ±10V Input Ranges

- AC and DC Performance Completely Specified

- Internal Sample/Hold, Clock, Reference, 3-State Buffer

- 215mW Power Dissipation

- No-Missing-Codes Over Temperature

- 8-Bit or 12-Bit Output Format

- Package Options

Plastic DIP

Hermetic DIP

SOIC

### DESCRIPTION

The ADS7800 is a complete, low-cost, 12-bit successive-approximation A/D converter with an internal sample/hold function. The ADS7800 uses an innovative, capacitor-array internal D/A converter, based on CMOS technology. The use of a CMOS architecture results in extremely low power consumption. Total acquisition and conversion time of  $3\mu \rm sec$  results in a 333kHz sampling rate, over the entire operating temperature range. AC and DC performance are completely specified.

The ADS7800 is complete with internal clock, reference, control logic, and 3-state output buffer. The interface logic provides for easy handshaking with most popular 8- and 16-bit microprocessors. The ADS7800's 3-state output buffer connects directly to the  $\mu P$ 's data bus, and is readable as either one 12-bit word or two 8-bit bytes. Chip select, high-byte enable, and read/write (read/convert) control inputs enable the ADS7800 to connect directly to a system address bus and control lines, and to operate totally under processor control.

Internal scaling resistors allow a pin-selectable choice of two input ranges:  $\pm 5\text{V}$  and  $\pm 10\text{V}$ . The ADS7800 is available for operation over the commercial (0°C to +70°C) and industrial (-40°C to +85°C) temperature ranges. Package options include 24-pin single (0.300″) plastic or hermetic ceramic DIPs, and 24-pin plastic SOIC. The ADS7800 operates from a +5V supply and either a -12V or -15V supply.

| Model<br>Number | Package      | Temperature<br>Range | Linearity<br>Error Max<br>(T <sub>min</sub> to T <sub>max</sub> ) | SINAD*<br>(dB Min.) |

|-----------------|--------------|----------------------|-------------------------------------------------------------------|---------------------|

| ADS7800JP       | Plastic DIP  | 0°C to +70°C         | <u>±</u> 1                                                        | 67                  |

| ADS7800KP       | Plastic DIP  | 0°C to +70°C         | <u>+</u> ½                                                        | 69                  |

| ADS7800JU       | Plastic SOIC | 0°C to +70°C         | ±1                                                                | 67                  |

| ADS7800KU       | Plastic SOIC | 0°C to +70°C         | <u>+</u> 1/2                                                      | 69                  |

| ADS7800AH       | Ceramic DIP  | -40°C to +85°C       | ±1                                                                | 67                  |

| ADS7800BH       | Ceramic DIP  | -40°C to +85°C       | ± ½                                                               | 69                  |

\*Signal-to-(Noise + Distortion) Ratio.

May 1992 Copyright 1992 Micro Networks All rights reserved

# MICRO NETWORKS

### ADS7800 12-Bit SAMPLING A/D CONVERTER

#### **ABSOLUTE MAXIMUM RATINGS**

#### Operating Temperature Range: 0°C to +70°C J. K Grades A, B Grades -40°C to +85°C Storage Temperature Range: -65°C to +150°C +Vs to Digital Ground +7V -V<sub>S</sub> to Analog Ground -16.5V +VSA to +VSD ±0.3V ± 1V Analog Ground to Digital Ground Control Inputs to Digital Ground -0.3V to $V_S$ +0.3VAnalog Input to Voltage ±20V Junction Temperature +160°C Lead Temperature (Soldering, 10 sec) +300°C Power Dissipation 750mW Thermal Resistance O<sub>JA</sub>: Plastic DIP 100°C/W SOIC 100°C/W Ceramic DIP 50°C/W

#### ORDERING INFORMATION

| PART NUMBER -                  | - ADS7800 J P |

|--------------------------------|---------------|

| Select suffix J. K. A or B for | - 11          |

| desired performance and        |               |

| specific temperature range. —  |               |

| Select suffix P, U or H        |               |

| for desired package option     |               |

### DESIGN SPECIFICATIONS (T<sub>A</sub> =T<sub>MIN</sub> to T<sub>MAX</sub>, V<sub>S</sub> = +5V, V<sub>S</sub> = -15V, f<sub>S</sub> = 333kHz, unless otherwise indicated)

| ANALOG INPUTS                                                              | MIN.  | TYP.            | MAX.       | UNITS       |

|----------------------------------------------------------------------------|-------|-----------------|------------|-------------|

| Input Voltage Range                                                        |       | ±10 and ±5      | -          | Volts       |

| Input Impedance: ±10V                                                      | 4.4   | 6.3             | 8.1        | kΩ          |

| ±5V                                                                        | 2.9   | 4.2             | 5.4        | kΩ          |

| DIGITAL INPUTS CS, R/C, HBE                                                |       |                 |            |             |

| Logic Levels: Logic "1"                                                    | +2.4  |                 | +5.3       | Volts       |

| Logic "0"                                                                  | -0.3  |                 | +0.8       | Volts       |

| Loading: Logic "1"                                                         |       |                 | +5         | $\mu$ A     |

| Logic "0"                                                                  |       | <u> </u>        | -5         | μΑ          |

| DIGITAL OUTPUTS DB0 to DB11, BUSY                                          |       |                 |            |             |

| Output Format                                                              | 12-Bi | Parallel or 8-B | it/4-Bit   |             |

| Output Coding                                                              |       | Offset Binary   |            |             |

| Logic Levels: Logic "1" (Isource = 500µA)                                  | +2.4  |                 | +5.0       | Volts       |

| Logic ''0'' (I <sub>SINK</sub> = 1.6mA)<br>Leakage (High-Impedance State)  | 0     | .01             | +0.4<br>±5 | Volts       |

| INTERNAL REFERENCE                                                         |       | ±0.1            | ±5         | μΑ          |

|                                                                            |       |                 |            |             |

| Reference Output Voltage (Pin 3) Available Output Source Current           | 1.9   | 2.0             | 2.1        | Volts       |

| '                                                                          |       | 10              |            | μΑ          |

| POWER SUPPLY REQUIREMENTS                                                  |       |                 | ļ <u></u>  |             |

| Power Supply Range: -V <sub>S</sub> Supply                                 | -11.4 | -15             | 16.5       | Volts       |

| Power Supply Range: +V <sub>S</sub> Supply Current Drains: -I <sub>C</sub> | +4.75 | +5.0<br>3.5     | +5.25      | Volts<br>mA |

| +I <sub>S</sub> (Total)                                                    |       | 3.5             | 25         | mA          |

| Power Dissipation                                                          |       | 135             | 215        | mW          |

| DYNAMIC CHARACTERISTICS                                                    |       | 1.00            |            |             |

| Aperture Delay                                                             |       | 13              |            | nsec        |

| Aperture Uncertainty (Jitter)                                              |       | 150             |            | psec, rms   |

| Transient Response, Full-Scale Step (Note 1)                               |       | 130             | 1          | nsec        |

| Overvoltage Recovery, 2 X FS (Note 2)                                      |       | 150             |            | nsec        |

| CONVERSION TIME                                                            |       |                 |            |             |

| Conversion Only                                                            |       | 2.5             | 2.7        | μsec        |

| Conversion + Acquisition                                                   |       | 2.6             | 3.0        | μsec        |

| Throughput Rate                                                            | 333   | 380             |            | kHz         |

### **SPECIFICATION NOTES:**

- 1. For 12-bit accuracy in specified time.

- 2. To specified performance in specified time.

- 3. Adjustable to zero with external trimpot.

- Least Significant Bit. 1LSB=2.44mV for the ±5V range; 4.88mV for the ±10V range.

- Characterized over T<sub>MIN</sub> to T<sub>MAX</sub> at +FS, 0V, and -FS. 0.1LSB is typical rms noise with worst-case conditions: +FS at +125°C.

- 6. All dB figures refer to ±10V or ±5V full-scale input.

CAUTION: These Devices are sensitive to electrostatic discharge. Proper anit-ESD IC handling procedures should be followed.

PERFORMANCE SPECIFICATIONS (T<sub>A</sub> =T<sub>MIN</sub> to T<sub>MAX</sub>,  $+V_S = +5V$ ,  $-V_S = -15V$ ,  $t_S = 333kHz$ , unless otherwise indicated)

| MODEL                                                                                                                                                                                                                   | ADS             | \$7800JP/J                   | U/AH                    | ADS             | 7800KP/K                     | U/BH                     |                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------|-------------------------|-----------------|------------------------------|--------------------------|------------------------------------------------------|

| TRANSFER CHARACTERISTICS                                                                                                                                                                                                | MIN.            | TYP.                         | MAX.                    | MIN.            | TYP.                         | MAX.                     | UNITS                                                |

| RESOLUTION                                                                                                                                                                                                              |                 |                              | 12                      |                 |                              | 12                       | Bits                                                 |

| TRANSFER CHARACTERISTICS                                                                                                                                                                                                |                 |                              | <u> </u>                |                 |                              | · · · ·                  |                                                      |

| Full-Scale Error Full-Scale Error Drift Integral Nonlinearity Differential Nonlinearity Resolution for No Missing Codes Bipolar Zero Error (Note 3) Bipolar Zero Error Drift                                            | 12              | 6                            | ±0.50<br>±1<br>±1<br>±4 | 12              | 6                            | ±0.35<br>±½<br>±¾<br>±34 | ppm/°C<br>LSB(Note 4<br>LSB<br>Bits<br>LSB<br>ppm/°C |

| Transition Noise (Note 5)                                                                                                                                                                                               |                 | 0.1                          |                         |                 | 0.1                          |                          | LSB                                                  |

| AC ACCURACY (Note 6)                                                                                                                                                                                                    |                 |                              |                         |                 |                              | _                        |                                                      |

| Spurious-Free Dynamic Range Total Harmonic Distortion Signal-to-Noise Ratio Signal-to-(Noise+Distortion) Ratio (SINAD) Intermodulation Distortion (-6dB Signals) (f <sub>IN1</sub> =24.4kHz; f <sub>IN2</sub> =28.5kHz) | 74<br>68<br>67  | 77<br>-77<br>71<br>70<br>-77 | -74<br>-74              | 77<br>70<br>69  | 80<br>-80<br>73<br>72<br>-77 | -77<br>-74               | dB<br>dB<br>dB<br>dB<br>dB                           |

| POWER SUPPLY SENSITIVITY                                                                                                                                                                                                |                 |                              |                         |                 |                              |                          |                                                      |

| -V <sub>S</sub> = -13.5V to -16.5V<br>-V <sub>S</sub> = -11.4V to -12.6V<br>+V <sub>S</sub> = +4.75V to +5.25V                                                                                                          |                 |                              | ± ½<br>± ½<br>± ½       |                 |                              | ±1/2<br>±1/2<br>±1/2     | LSB<br>LSB<br>LSB                                    |

| TEMPERATURE RANGE                                                                                                                                                                                                       |                 |                              |                         |                 |                              | I 72                     | LOD                                                  |

| Specified: JP/JU/KP/KU Models<br>AH/BH/ Models<br>Storage                                                                                                                                                               | 0<br>-40<br>-65 |                              | +70<br>+85<br>+150      | 0<br>-40<br>-65 |                              | +70<br>+85<br>+150       | င့်<br>ငွင့်                                         |

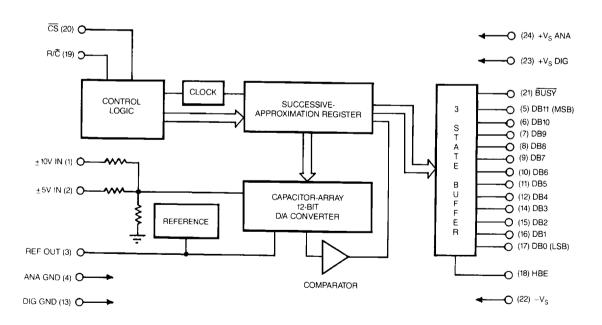

**ADS7800 BLOCK DIAGRAM**

#### PIN DESIGNATIONS

| · III DEC |    |

|-----------|----|

| 1         | 24 |

| 1'        |    |

| 1         | 1  |

| 1         |    |

| 1         |    |

|           |    |

|           |    |

|           |    |

|           |    |

|           |    |

|           | ì  |

|           |    |

| 12        | 13 |

|           |    |

- 1 ±10V Analog Input. Ground for ±5 range.

- 2 ±5V Analog Input. Ground for ±10V range.

- 3 +2V Reference Output

- 4 Analog Ground. Connect to Pin 13.

- 5 Data Bit 11 (MSB)

- 6 Data Bit 10

- 7 Data Bit 9

- 8 Data Bit 8

- 9 Data Bit 7 if HBE Low; "0" if HBE High.

- 10 Data Bit 6 if HBE Low; "0" if HBE High.

- 11 Data Bit 5 if HBE Low; "0" if HBE High.

- 12 Data Bit 4 if HBE Low; "0" if HBE High.

- 24 +5V Analog Power Supply. Connect to Pin 23.

- 23 +5V Digital Power Supply. Connect to Pin 24

- 22 -12V or -15V Negative Power Supply

- 21 BUSY

- 20 CS Chip Select

- 19 R/C Read/Convert

- 18 HBE High Byte Enable

- 17 Data Bit 0 (LSB) if HBE Low, Data Bit 8 if HBE High.

- 16 Data Bit 1 if HBE Low; Data Bit 9 if HBE High.

- 15 Data Bit 2 if HBE Low; Data Bit 10 if HBE High.

- 14 Data Bit 3 if HBE Low; Data Bit 11 if HBE High.

- 13 Digital Ground, Connect to Pin 4.

# **DESCRIPTION OF OPERATION**

The AD\$7800 is a complete 12-bit A/D converter. It uses the successive approximation conversion technique and incorporates all required function blocks — capacitor-array D/A converter, corr.parator, clock, reference, and control logic. The CMOS-based capacitor-array architecture provides an inherent sample/hold function. The device mates directly to most popular 8-, 16-, and 32-bit microprocessors and contains all the necessary address-decoding logic, control logic, and 3-state output buffering to operate completely under processor control. In most cases, the AD\$7800 will require only power supplies and bypass capacitors to provide the complete A/D conversion function. The completeness of the device makes it most convenient to think of the AD\$7800 as a function block with specific input/output transfer characteristics; it is thus quite unnecessary to be concerned with its inner workings.

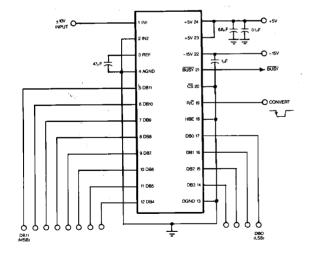

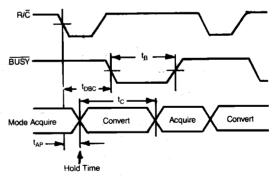

BASIC OPERATION — Figure 1 gives the basic connections for operating the ADS7800 with the ±10V input range in Convert mode. The Convert command R/C, applied to Pin 19, puts the ADS7800 in Hold mode and initiates the conversion. R/C must hold Pin 19 low for at least 40nsec. The BUSY signal on Pin 21 is held low during the conversion, and goes high after the conversion is completed and the data is transferred to the output latches. The rising edge of the signal on Pin 21 can thus serve to read the converted data.

Figure 1. Basic ±10V Connection Diagram

During the conversion, the BUSY signal imposes the high-impedance state on the output data lines and also inhibits input lines. The inhibition causes Pin 19 to ignore any pulses, so new conversions cannot be initiated while a conversion is taking place, whether the pulses result from spurious sources or an attempt to short-cycle the conversion.

In Read mode, Pin 19 is held low, and a high-going pulse serves to read data and initiate a conversion. In Read mode, the rising edge of the R/ $\overline{C}$  signal on Pin 19 enables the output data pins, thus validating the data from the previous conversion. The falling edge of R/ $\overline{C}$  then puts the ADS7800 in Hold mode and initiates a new conversion. The ADS7800 will begin acquiring a new signal upon the completion of the conversion, even before the  $\overline{BUSY}$  signal rises on Pin 21, and will track the input signal until the start of the next conversion, whether the ADS7800 is in Convert or Read mode.

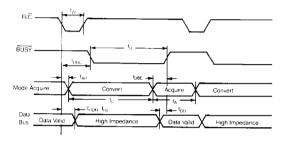

The signal HBE on Pin 18 allows the ADS7800 to be used with an 8-bit bus. At the end of a conversion, a low input on Pin 18 loads the eight LSBs of data into the latches of Pins 9 through 12 and 14 through 17. A high signal on Pin 18 then loads the four MSBs into the latches of Pins 14 through 17, and Pins 9 through 12 are forced low. Figure 2 and Table 1 give the timing parameters for the basic acquisition and conversion operations.

Figure 2. Conversion and Acquisition Timing

| Symbol           | Parameter           | Тур  | Max  | Units     |

|------------------|---------------------|------|------|-----------|

| tosc             | BUSY Delay from R/C | 80   | 150  | nsec      |

| t <sub>B</sub>   | BUSY Low            | 2.5  | 2.7  | μsec      |

| t <sub>AP</sub>  | Aperture Delay      | 13   |      | nsec      |

| Δt <sub>AP</sub> | Aperture Jitter     | 150  |      | psec, rms |

| t <sub>C</sub>   | Conversion Time     | 2.47 | 2.70 | μsec      |

Table 1. Acquisition and Conversion Timing

**CONTROL FUNCTIONS** — The ADS7800 offers easy interface to most digital systems, whether microprocessor-based or other. The ADS7800 can operate under complete microprocessor control, or in a stand- alone mode, in which it is controlled only by the R/ $\overline{\mathbb{C}}$  input on Pin 19. Microprocessor control entails initiating the conversion and reading the output data, either in one 12-bit parallel word or in two 8-bit bytes. All control inputs ( $\overline{\mathbb{CS}}$ , R/ $\overline{\mathbb{C}}$ , and HBE) are TTL- and CMOScompatible. Tables 2 and 3 detail the functions of the control inputs.

| Pin No. | Symbol    | Function                                                                                                                                                                                   |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | HBE       | High Byte Enable. When held Low, data output has 12-bit parallel format. When held High, 4 MSBs appear on Pins 14 to 17; zeros appear on Pins 9 to 12. Must be Low to initiate conversion. |

| 19      | R/C       | Read/Convert. Falling edge initiates conversion when CS is Low, HBE is Low, and BUSY is High.                                                                                              |

| 20      | <u>cs</u> | Chip Select. Outputs in High-Z state when CS is High. Must be Low to initiate conversion or read data.                                                                                     |

| 21      | BUSŸ      | Busy, Output Low during conversion.  Data valid on rising edge in Convert mode.                                                                                                            |

Table 2. Role of Control Functions

| cs | R/C  | HBE | BUST | Operation                                                                                                        |

|----|------|-----|------|------------------------------------------------------------------------------------------------------------------|

| 1  | Х    | Χ   | 1    | None — Outputs in High-Z State.                                                                                  |

| 0  | 1 →0 | 0   | 1    | Holds Signal and Starts Conversion.                                                                              |

| 0  | 1    | 0   | 1    | 3-State Output Buffers Enabled Upon End of Conversion.                                                           |

| 0  | 1    | 1   | 1    | Enable High Byte in 8-Bit Bus Mode.                                                                              |

| 0  | 1 →0 | 1   | 1    | Inhibits Start of Conversion.                                                                                    |

| X  | Х    | Х   | 0    | Conversion in Progress. Outputs in<br>High-Z State. New Conversion Inhibited<br>Until End of Present Conversion. |

X="Don't Care".

**Table 3. Control Functions**

In stand-alone mode, a single control line connected to R/C controls the ADS7800.  $\overline{CS}$  and HBE are grounded in this mode. The output data is in 12-bit parallel format. Stand-alone mode is useful in systems using dedicated input ports that do not require full bus-interface capability.

A high-to-low transition on  $R/\overline{C}$  initiates a <u>conversion</u>. The 3-state output latches are enabled when  $R/\overline{C}$  and  $\overline{BUSY}$  are high. Thus, two modes of operation are possible: Either positive or negative pulses can initiate a conversion. Either way, the  $R/\overline{C}$  pulse must remain low for at least 40nsec.

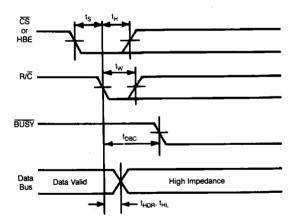

Figure 3 and Table 4 give timing details for a conversion initiated by a negative R/ $\overline{C}$  pulse. In this case (referred to as Convert mode), the 3-state outputs revert to the high-impedance state in response to the falling edge of R/ $\overline{C}$ , and become enabled for data access after the completion of the conversion.

Figure 3. Timing with Negative R/C Pulse

| Symbol             | Parameter                                                                  | Min. | Тур. | Max. | Units     |

|--------------------|----------------------------------------------------------------------------|------|------|------|-----------|

| tw                 | R/C Pulse Width                                                            | 40   | 10   |      | nsec      |

| t <sub>DBC</sub>   | BUSY Delay from R/C                                                        | 1    | 80   | 150  | nsec      |

| t <sub>8</sub>     | BUSY Low                                                                   |      | 2.5  | 2.7  | μsec      |

| t <sub>AP</sub>    | Aperture Delay                                                             |      | 13   |      | nsec      |

| ∆t <sub>AP</sub>   | Aperture Jitter                                                            |      | 150  |      | psec, rm: |

| t <sub>C</sub>     | Conversion Time                                                            |      | 2.47 | 2.7  | μsec      |

| t <sub>DBE</sub>   | BUSY from End of Conversion                                                |      | 100  |      | nsec      |

| t <sub>DB</sub>    | BUSŸ Delay after Data Valid                                                | 25   | 75   | 200  | nsec      |

| t <sub>A</sub>     | Acquisition Time                                                           |      | 130  | 300  | nsec      |

| A + t <sub>C</sub> | Total Throughput Time                                                      |      | 2.6  | 3.0  | μSec      |

| t <sub>HDR</sub>   | Valid Data Held after R/C Low                                              | 20   | 50   | 0.0  | nsec      |

| ts                 | CS or HBE Low before R/C 1→0 Transition                                    | 25   | 5    |      | nsec      |

| t <sub>H</sub>     | CS or HBE Low after R/C 1→0 Transition                                     | 25   | 0    |      | nsec      |

| t <sub>DD</sub>    | Data Valid from CS Low, R/C High, and HBE as Selected (100-pF Load)        | "    | 65   | 150  | nsec      |

| t <sub>HDR</sub>   | Valid Data Held after R/C Low                                              | 20   | 50   | 130  | nsec      |

| t <sub>HL</sub>    | Delay to High-Z State after R/C Falls or CS Rises (3kΩ Pullup or Pulldown) |      | 50   | 150  | nsec      |

Table 4. Timing Specifications Over  $T_{MIN}$  to  $T_{MAX}$ .

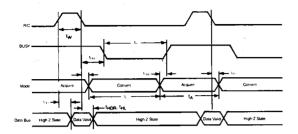

Figure 4 and Table 4 detail the timing considerations for a conversion initiated by a positive  $R/\overline{C}$  pulse. In this case (referred to as Read mode), output data from a previous conversion is enabled during the high portion of  $R/\overline{C}$ . The falling edge of  $R/\overline{C}$  initiates a new conversion, and the 3-state outputs revert to the high-impedance state until  $R/\overline{C}$  again attains a high state.

Figure 4. Timing with Positive R/C Pulse

TIMING — INITIATING CONVERSIONS — As seen in Table 1, only a negative-going transition on R/C—no other combination of states or transitions—can initiate a conversion in the ADS7800.  $\overline{CS}$  or HBE high, or  $\overline{BUSY}$  low, will inhibit conversion.  $\overline{CS}$  and HBE should be stable for at least 25 risec prior to the R/C transition. Figure 5 shows the timing details for initiation of a conversion.

Figure 5. Conversion Initiation Timing

The BUSY line, in a low state only during a conversion, shows the status of the converter. During the conversion, the 3-state output latches remain in a high-impedance state; therefore, data is inaccessible during a conversion. During the conversion, the digital inputs  $\overline{CS}$ ,  $\overline{R/C}$ , and HBE are immune to additional transitions, so conversions cannot be prematurely terminated or restarted.

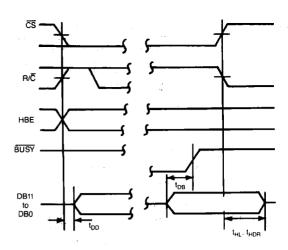

TIMING — READING DATA — After the start of a conversion, the 3-state output buffers remain in a high-impedance state until the following logic combination exists: P/C is high, BUSY is high, and CS is low. When this combination occurs, the 3-state data lines are enabled in accordance with the state of HBE. Figure 6 and Table 4 give details of the timing relationships and specifications for reading data.

Figure 6. Read Cycle Timing

INTERNAL CLOCK — A factory-trimmed internal clock in the ADS7800 yields a typical conversion time of 2.47µsec at 25°C, and a maximum conversion time of 2.7µsec over the entire operating temperature range. This conversion time, coupled with a guaranteed maximum acquisition time of 300nsec, ensures a 333kHz minimum throughput rate under all conditions.

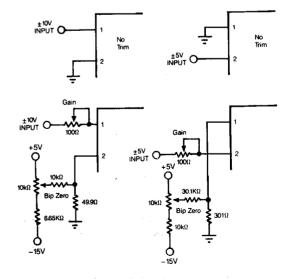

BIPOLAR OPERATION AND CALIBRATION — Analog input connections and calibration circuits for the ADS7800 are shown in Figure 7. If the ±5V input range is to be used, apply the analog input to Pin 2 and ground Pin 1. If the ±10V range is to be used, apply the analog input to Pin 1 and ground Pin 2. If either offset or gain adjustments are not to be used, the ADS7800 will perform to the limits in the specification table.

Bipolar offset (zero) error can be defined as the accuracy of the 0111 1111 1111 to 1000 0000 0000 transition voltage (-2.44mV for the  $\pm 10V$  range; -1.22mV for the  $\pm 5V$  range). With the ADS7800 converting continuously, adjust the  $10k\Omega$  trimpot "up" until the output code is 1000 0000 0000, then adjust "down" until all bits are "flickering" between "0" and "1".

Figure 7. Connections and Calibration

Bipolar gain error can be defined as the accuracy of the 1111 1111 1110 to 1111 1111 1111 digital output transition after the bipolar offset adjustment has been effected. Ideally, this transition should occur 11/zLSBs below the nominal positive full-scale value of the selected input range. This corresponds to +4.9963V and +99927V for the ±5V and ±10V ranges, respectively. Gain trimming is accomplished by applying either of these voltages and adjusting the gain trimpot "up" until the digital outputs are all ones, then adjusting "down" until the LSB "flickers" between "1" and "0".

**LAYOUT CONSIDERATIONS AND GROUNDING** — The ADS7800 has two +5V supply pins:  $V_{SA}$  (Pin 24) and  $V_{SD}$  (Pin 23). To achieve maximum accuracy in the ADS7800, these supplies are not connected internally. They should be connected together on the printed-circuit board, at a point as close as possible to the ADS7800. Both supply lines should be well isolated from digital supplies that are subject to large load variations. As a general rule, it is good practice to isolate the analog portions of a system from the effects of digital switching by running a separate +5V supply line from a supply regulator to the analog components.

To minimize noise, the tied-together  $V_S$  Pins 23 and 24 should be bypassed to ground with a 6.8 $\mu$ F tantalum capacitor in parallel with a 0.1 $\mu$ F multilayer ceramic capacitor. The  $-V_S$  Pin 22 should also be bypassed to ground with a 1 $\mu$ F tantalum capacitor. All bypass capacitors should be connected as close as possible to the ADS7800.

These bypassing measures are extremely important, as noise on the power-supply lines can degrade converter performance. It is necessary to pay special attention to filtering out noise and spikes when a switching power supply is used.

The analog (Pin 4) and digital (Pin 13) ground pins are also not connected internally, and should be connected together as close as possible to the ADS7800. The use of a ground plane on the printed-circuit board is highly recommended, as it optimizes high-frequency ground characteristics and reduces noise coupling light sensitive converter circuitry. It is especially important to reference the analog input to the analog ground on Pin 4, to eliminate from the input circuitry any voltage drops that might occur in the power-supply ground returns.

It is necessary to take the input impedance of the ADS7800 into account when designing the analog drive circuitry. The output impedance of the driver should be negligible with respect to the 6.34 $\Omega$  ( $\pm$ 10V range) or 4.2k $\Omega$  ( $\pm$ 5V range) input impedance of the ADS7800, or at least invariant with respect to signal level. Further, it is crucial to prevent any coupling between the analog input lines and digital signal lines. If these lines must cross, it is recommended that they do so at right angles, and with a minimum of crossover area. If they must run parallel-for any distance, it is good design practice to insert a ground pattern between them as a shield. Any external trimpots used for full-scale or offset ad-

justments should be mounted as close to the converter as possible,

It is necessary to bypass the reference output (Pin 3) with a  $22\mu F$  to  $47\mu F$ , 2V tantalum capacitor. The drive capability of this pin is limited ( $10\mu A$  typ), so it is necessary to provide buffering if this reference voltage is to be used in other parts of the system.

POWER-SUPPLY SEQUENCING PRECAUTIONS — If the two +5V supply inputs of the ADS7800 are powered-up sequentially instead of simultaneously, the converter may experience latch-up and draw excessive current. Connecting the two supply pins together on the printed-circuit board will normally prevent this problem. However, the phenomenon can occur if the ADS7800 is plugged into a live socket-for example, during incoming inspection or lab evaluation. In these cases, it is necessary to ensure that power is applied only after the ADS7800 has been plugged in.

AVOIDING TRANSIENT PHÉNOMENA — Various transients coupled into the AD\$7800 can cause errors that may difficult to diagnose. If errors persist despite careful grounding and bypassing measures, they might find their origins in one or mare not-so-obvious transient phenomena. A checklist of several transient-avoidance steps can be useful in designing a new system.

Transients that occur during critical periods in the conversion process can produce errors. For example, a clean, sharp Hold command ("1" to "0" transition on R/C) signal is crucial to error- free operation. This edge should be clean and sharp and free from significant ringing, especially in the 20nsec period after it occurs. Another not-so-obvious helpful design practice is to avoid any transitions on digital lines during the bit decisions in the conversion process. So it is prudent to avoid any changes in R/C at the time of any bit decisions. Keeping the R/C pulse short (< 100nsec) will avoid a transition at the time of the MSB decision, or keeping it long (> 2.7,sec) will avoid affecting the LSB decision.

High-speed bus transients can also couple into the ADS7800 via the data outputs, even when the output buffers are in the high-impedance state. If such transients exist, it is good practice to isolate them from the converter by providing additional buffering to the data outputs. The BUSY line can serve to enable these added buffers.

It goes without saying that transients on the analog inputs are to be avoided scrupulously, especially in the interval within  $\pm 20$ nsec of the "1"-to-"0" transition of R/C, when they may affect the charge transferred to the capacitor array. Careful layout and design of the analog drive circuitry are necessary to avoid these transients. Finally, in multiplexed systems, it is most prudent to switch channels in the multiplexer only after the conversion is complete. Otherwise, glitches or ringing in the switched signal may be coupled into the ADS7800 during the conversion process.

#### DIGITAL OUTPUT CODING

| ANALOG  | i INPUT (Volts) | DIGITAL | OUTPUT           |

|---------|-----------------|---------|------------------|

| ±5V     | ± 10V           | MSB     | LSE              |

| +5.0000 | +10.0000        | 1111 1  | 111 1111         |

| +4.9963 | +9.9927         | 1111 1  | 111 1119 *       |

| +0.0012 | +0.0024         | 1000 00 | 000 000          |

| -0.0012 | -0.0024         | 0000 0  | මුතුන් ඉතුමුල් - |

| -0.0037 | -0.0073         | 0111 1  | 111 1119         |

| -4.9988 | -9.9976         | 0000 0  | 000 000€*        |

| -5.0000 | -10.0000        | 0000 0  | 000 0000         |

#### **DIGITAL OUTPUT CODING NOTES:**

- 1. Output coding is offset binary.

- 2. For ±5V input range, 1LSB for 12 bits = 2.44mV. 1LSB for 11 bits = 4.88mV.

- For ±10V input range, 1LSB for 12 bits = 4.88mV. 1LSB for 11 bits = 9.77mV.

Voltages given are the theoretical values for the transitions indicated. Ideally, with the converter continuously converting, the output bits indicated as Ø will change from a logic "1" to a logic "0" or visa versa as the input voltage passes through the level indicated

EXAMPLE: For an ADS7800 operating on its  $\pm$ 10V input range, the transition from digital output 0000 0000 0001 (or vice versa) will ideally occur at an input voltage of -99976 volts. Subsequently, any input voltage more negative than -9.9976 volts will give a digital output of all "O's". The transition from digital output 1000 0000 0000 to 0111 1111 1111 will ideally occur at an input of -0.0024 volts, and the 1111 1111 1111 to 1111 1110 transition should occur at +9.9927 volts. An input more positive than +9.9927 volts will give all "1's".

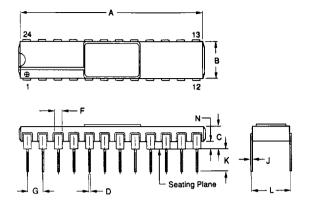

# **PACKAGE OUTLINES**

# PACKAGE H. CERAMIC HERMETIC DIP

|     | INCH   | IE\$  | MILLIN | IETERS |

|-----|--------|-------|--------|--------|

| DIM | MIN    | MAX   | MIN    | MAX    |

| Α   | 1.188  | 1.212 | 30.18  | 30.78  |

| В   | .300   | .320  | 7.62   | 8.13   |

| C   | _      | .160  | -      | 4.06   |

| D   | .016   | .020  | 0.41   | 0.51   |

| F   | .050 T | γP    | 1.27 T | ΥP     |

| G   | .095   | .105  | 2.41   | 2.67   |

| J   | .009   | .012  | 0.23   | 0.31   |

| K   | .170 B | ASIC  | 4.32 E | BASIC  |

| L   | .290   | .310  | 7.37   | 7.87   |

| N   | .040   | .060  | 1.02   | 1.52   |

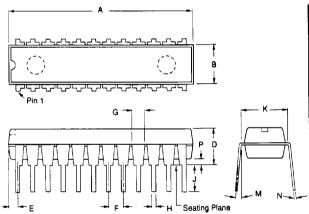

# PACKAGE P. PLASTIC DIP

|      | INCH       | IES   | MILLIN     | METERS |

|------|------------|-------|------------|--------|

| DIM  | MIN        | MAX   | MIN        | MAX    |

| Α    | 1.125      | 1.255 | 28.58      | 31.88  |

| В    | .250       | .290  | 6.35       | 7.37   |

| _ D_ | .150       | .170  | 3.81       | 4.32   |

| E    | .010       | .080  | .25        | 2.03   |

| F    | .100 BASIC |       | 2.54 BASIC |        |

| G    | .050       | .070  | 1.27       | 1.78   |

| Н    | .016       | .020  | 0.41       | 0.51   |

| J    | .125       |       | 3.18       |        |

| К    | .300 B     | ASIC  | 7.63 E     | BASIC  |

| М    | 0°         | 15°   | 0°         | 15°    |

| N    | .008       | 015   | 0.20       | 0.38   |

| Р    | .010       | .030  | .25        | .76    |

|      |            |       |            |        |

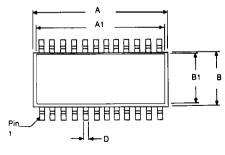

### PACKAGE U. PLASTIC SOIC

|     | INCHES     |      | MILLIMETERS |       |

|-----|------------|------|-------------|-------|

| DIM | MIN        | MAX  | MIN         | MAX   |

| A   | .602       | .618 | 15.29       | 15.70 |

| A1  | .595       | .618 | 15.11       | 15.70 |

| В   | .286       | 302  | 7.26        | 7.67  |

| B1  | .270       | .285 | 6.86        | 7.24  |

| С   | .093       | .108 | 2.36        | 2.74  |

| D   | .015       | .019 | 0.38        | 0.48  |

| G   | .050 BASIC |      | 1.27 BASIC  |       |

| н   | .026       | .034 | 0.66        | 0.86  |

| J   | .008       | .012 | 0.20        | 0.30  |

| L   | .390       | .422 | 9.91        | 10.72 |

| м   | 0°         | 10°  | O°          | 10°   |

| N   | .000       | .012 | 0.00        | 0.30  |