## Near Field Communications Controller with Integrated EEPROM for Battery-off Mode

#### GENERAL DESCRIPTION

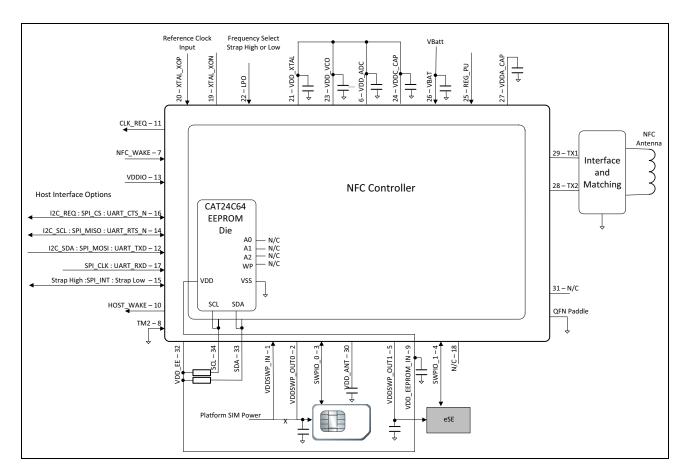

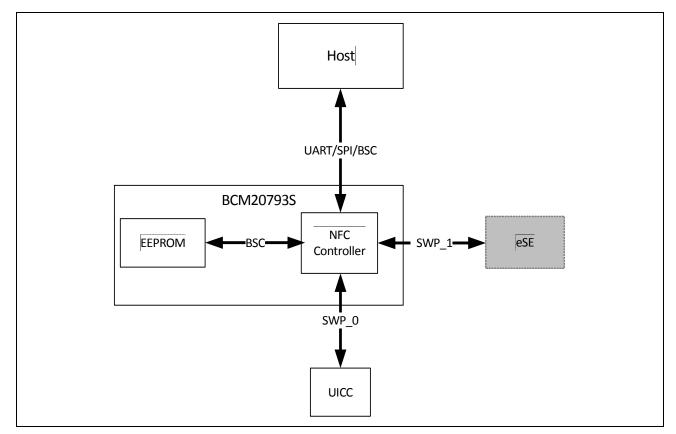

The Broadcom<sup>®</sup> BCM20793S is an NFC-compliant, highly integrated, low power, low cost, 40 nm NFC controller combined with an integrated EEPROM for battery-off operation in a single package. The BCM20793S is an update to the BCM20793, which features secure configuration and patch download for applications involving the management and operation of NFC secure elements. The BCM20793S sizeoptimized architecture is housed in a QFN-34L package that measures 4.0 mm × 4.5 mm × 0.9 mm (nominal), and requires minimal external components. This brings the traditional two-chip NFC controller and EEPROM for battery-off operation into a single package solution to minimize PCB footprint. Refer to the architecture block diagram in Figure 1 on page 2.

BROADCOM。SWP 走的是全双工信号(双向)

The BCM20793S is designed for low-power mobile applications. It is based on over 15 years of Radio Frequency Identification (RFID) and NFC experience. By building onto the BCM20792S, the BCM20793S is designed to be an integral part of all NFC standardscompliant systems. The BCM20793S has the same dual Single Wire Protocol (SWP) secure element interfaces as the BCM20792S, but brings the EEPROM option for battery-off operation to be internal to the package. The BCM20793S is package and pin-compatible with the

BCM20794S (which has integral secure element) using minimal external link component changes. The BCM20793S incorporates the PPSE and AID routing functionality for support of multiple applications across multiple secure elements and execution environments.

#### **APPLICATIONS**

- Contactless payment

- Mobile handsets

- Simplified connectivity between wireless devices

- Contactless ticketing

- Peer mode transactions

- Smartposter tag reading/writing

- Access control

#### FEATURES

#### NFC

- Support for the ISO/IEC 18092, ISO/IEC 21481, ISO/ IEC 14443 Types A, B and B', Japanese Industrial Standard (JIS) (X) 6319-4, and ISO/IEC 15693 standards

- No active components requirement for antenna or field-power conditioning 天线无需主动器件

- Individual byte framing 人线尤需主动

- Hardware-based collision detection and modulation controls

- Reader/Writer (R/W) mode

自带存储

- Active and Passive Peer (P2P) mode

- Tag/Card Emulation mode: 主动、被动、读写模式

Support for battery-enabled card emulation mode

- Support for battery-enabled card emulation mode

Support for two levels of "residual" batteryassisted card emulation mode

- Support for completely powered from the field (battery-off) card emulation mode

Co-packaged CAT24C64 EEPROM:

- Co-packaged CAT24C64 EEPROM:

64 Kb (8 KB) for battery-off personality, persistence, and PPSE/AID routing data storage

- Dual Single Wire Protocol (SWP) interfaces:

- SWP\_0 with platform PMU SIM power switching to UICC SIM card.

- SWP\_1 for embedded secure element or secondary UICC SIM cards

- Supports application tunnelling to secure elements over SWP

- Supports AID routing between host and secure element(s)

- Internal low-power oscillator for periodic wake-up and mode switch operation

- Low-power target detection mode for extremely low average current consumption 'sniff mode'

- NFC Forum NFC Controller Interface (NCI) for host interface

#### General

- Integral Low-Drop Out (LDO) regulator for direct connection to platform battery

- Clock sourced from platform reference frequency input for minimum BOM (or external XTAL option)

- ARM<sup>®</sup> Cortex<sup>®</sup>-M0 with 128 KB ROM and 19 KB RAM

- Supports UART, SPI, and BSC (I<sup>2</sup>C-compatible) for host interface

- Multiple low-power modes for flexible power management

- Low-power consumption in all modes and support for field-power mode

- Minimum hardware size and BOM

Figure 1: Functional Block Diagram

### **Revision History**

| Revision       | Date     | Change Description                                                                                                                                                                                                                                                                                                       |

|----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20793S-DS101-R | 06/05/12 | <ul> <li>Updated:</li> <li>Corrected errors related to the Single Wire Protocol (SWP) interface.</li> <li>Table 5: "Transitions Controlled by the Host," on page 25 and<br/>Table 6: "Transitions Controlled Through the VBAT Monitor," on<br/>page 27 — removed the footnote related to EEPROM requirements.</li> </ul> |

| 20793S-DS100-R | 05/21/12 | Initial release.                                                                                                                                                                                                                                                                                                         |

Broadcom Corporation 5300 California Avenue Irvine, CA 92617

© 2012 by Broadcom Corporation All rights reserved Printed in the U.S.A.

Broadcom<sup>®</sup>, the pulse logo, Connecting everything<sup>®</sup>, and the Connecting everything logo are among the registered trademarks of Broadcom Corporation and/or its subsidiaries in the United States, certain other countries, and/or the EU. Bluetooth<sup>®</sup> is a trademark of the Bluetooth SIG. Any other trademarks or trade names mentioned are the property of their respective owners.

Confidential and Proprietary Information: This document and the software are proprietary properties of Broadcom Corporation. This software package may only be used in accordance with the Broadcom Corporation license agreement.

This data sheet (including, without limitation, the Broadcom component(s) identified herein) is not designed, intended, or certified for use in any military, nuclear, medical, mass transportation, aviation, navigations, pollution control, hazardous substances management, or other high risk application. BROADCOM PROVIDES THIS DATA SHEET "AS-IS", WITHOUT WARRANTY OF ANY KIND. BROADCOM DISCLAIMS ALL WARRANTIES, EXPRESSED AND IMPLIED, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT.

# **Table of Contents**

| About This Document                                          | 9  |

|--------------------------------------------------------------|----|

| Purpose and Audience                                         | 9  |

| Acronyms and Abbreviations                                   | 9  |

| References                                                   | 9  |

| Technical Support                                            | 10 |

| Section 1: Introduction                                      |    |

| General Description                                          | 11 |

| Features                                                     |    |

| NFC Features                                                 | 12 |

| General Features                                             | 12 |

| Applications                                                 | 13 |

| Section 2: NFC Subsystem                                     |    |

| Operational Modes                                            | 14 |

| Peer Mode                                                    | 14 |

| Reader/Writer Mode                                           | 14 |

| Card Emulation Mode                                          | 14 |

| ISO Standards                                                | 15 |

| Radio Modes                                                  | 16 |

| Initiator Mode                                               | 16 |

| Mode Switch                                                  | 16 |

| Low Power Target Detection                                   |    |

| Multiple Technology Support and Automatic Standard Detection | 19 |

| Power Supply Topology                                        | 20 |

| NFC Power Management                                         | 20 |

| Card Emulation Power Modes                                   | 21 |

| CE Level 4 Power State                                       | 21 |

| CE Level 3 Power State                                       | 21 |

| CE Level 2 Power State                                       | 21 |

| CE Level 1 Power State                                       | 21 |

| CE Power Levels                                              | 23 |

| Full Power Mode (R/W, P2P, and CE)                           | 23 |

| Snooze Standby Mode                                          | 23 |

| CE Level 4 (CE Only)                                         | 23 |

| CE Level 3, Residual Battery Mode/Battery Assisted Mode (CE Only)     | 24 |

|-----------------------------------------------------------------------|----|

| CE Level 2, Residual Battery Mode/Partly Field-Powered Mode (CE Only) | 24 |

| CE Level 1, Battery Off/Field Power Harvesting Mode (CE Only)         | 24 |

| Secure Element Configuration Options                                  | 29 |

| Battery-off Source of Personality and Persistence Data                | 29 |

| Section 3: Interfaces                                                 |    |

| Host Interfaces                                                       |    |

| Host Interface Selection                                              |    |

| UART                                                                  | 31 |

| BSC (I <sup>2</sup> C-Compatible)                                     |    |

| SPI                                                                   | 36 |

| Secure Element Interfaces                                             | 40 |

| Single Wire Protocol                                                  |    |

| Nonvolatile Memory Interface                                          | 42 |

| Section 4: Microprocessor and Memory Unit                             | 43 |

| Section 5: Frequency References                                       | 45 |

| Reference Clock Input and XTAL Oscillator Option                      | 45 |

| Internal Low-Power Oscillator                                         | 45 |

| Reference Clock Input and XTAL Oscillator Specification               | 46 |

| Card Emulation and Field Power Harvesting Clock                       | 47 |

| Section 6: DC Characteristics                                         | 48 |

| Recommended Operating Conditions                                      | 48 |

| Absolute Maximum Ratings                                              | 49 |

| Internal Regulators                                                   | 50 |

| Power Supply                                                          | 50 |

| I/O Supply Voltages                                                   | 50 |

| V <sub>BATT</sub> Monitor                                             | 50 |

| Section 7: AC Characteristics                                         | 51 |

| I/O Digital Level Specifications                                      | 51 |

| Typical Current Consumption                                           | 52 |

| Section 8: Pin Information                                            | 54 |

| Pin List                                                              | 54 |

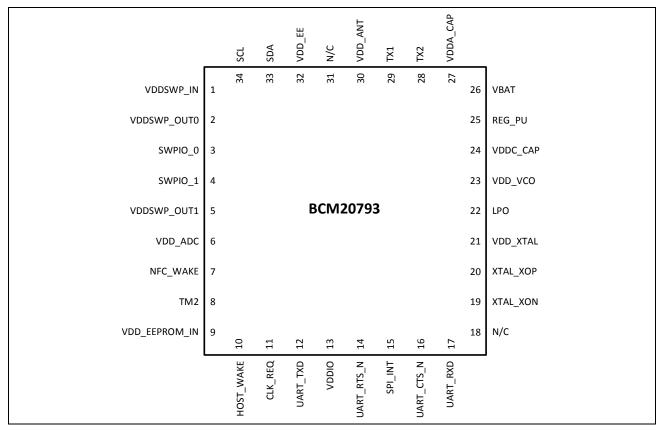

| QFN-34L Pin Diagram                                                   | 55 |

|                                                                       |    |

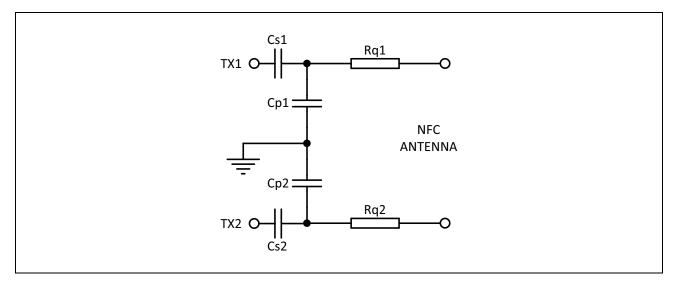

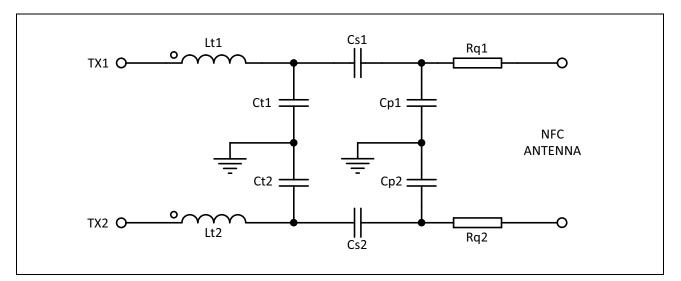

| Section 9: Antenna Interface          |    |

|---------------------------------------|----|

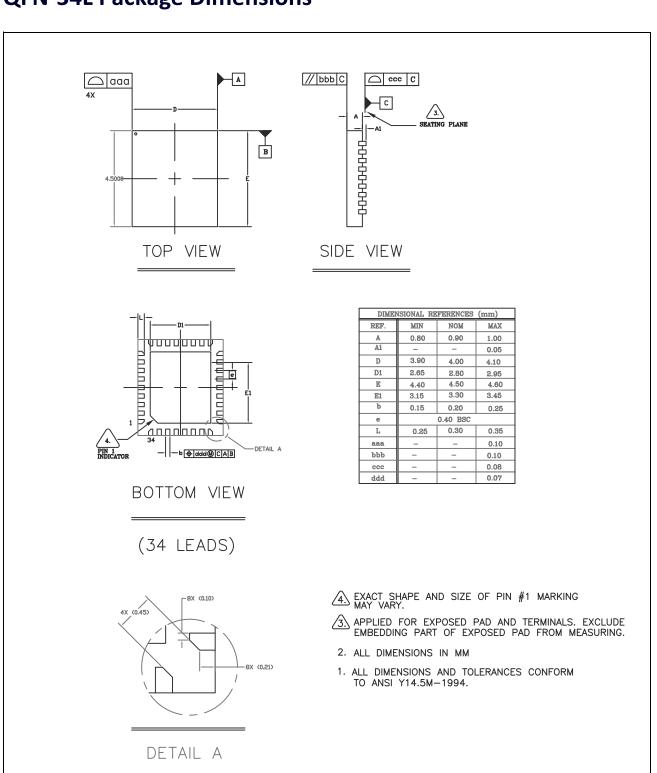

| Section 10: Mechanical Specifications |    |

| Package Thermal Characteristics       | 57 |

| Environmental Ratings                 | 57 |

| QFN-34L Package Dimensions            | 58 |

| Section 11: Ordering Information      |    |

| Appendix A: Acronyms                  |    |

# **List of Figures**

| Figure 1: Functional Block Diagram                                                       | 2  |

|------------------------------------------------------------------------------------------|----|

| Figure 2: NFC Forum Mode Switch Polling and Listening                                    | 17 |

| Figure 3: Forum Mode Switch Polling for NFC-A, NFC-B, and NFC-F                          | 17 |

| Figure 4: Representation of Averaged Duty-Cycle Current                                  | 18 |

| Figure 5: Principle of Low Power Target Detection (LPTD) Mode                            | 19 |

| Figure 6: Mapping CE Levels                                                              | 22 |

| Figure 7: CE Power Level Control                                                         | 23 |

| Figure 8: NFC Secure Element Configuration                                               | 29 |

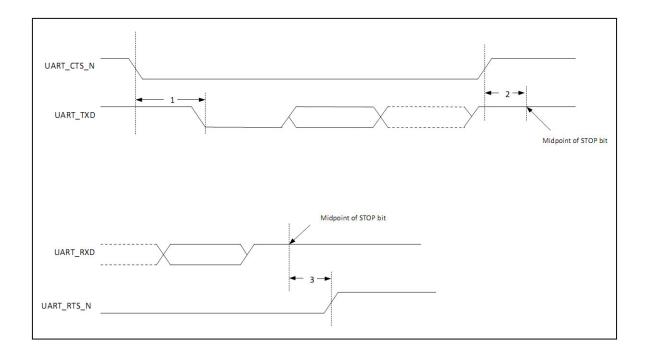

| Figure 9: UART Timing Waveform                                                           | 31 |

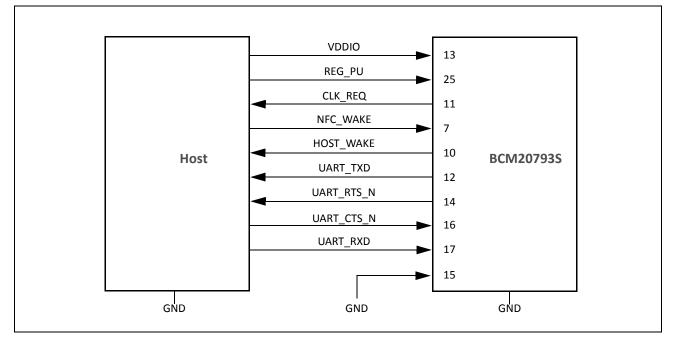

| Figure 10: UART Host Interface                                                           | 32 |

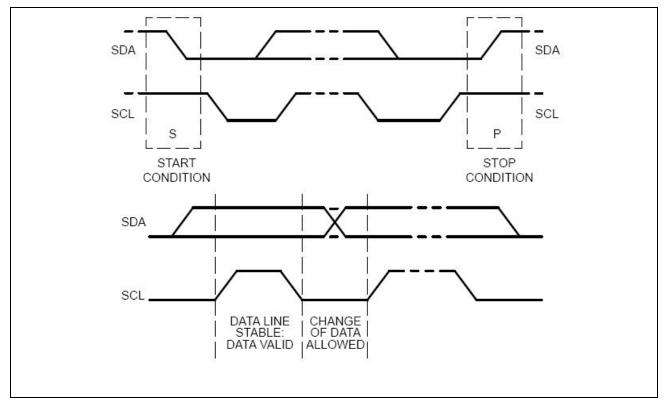

| Figure 11: BSC Timing Waveform                                                           | 33 |

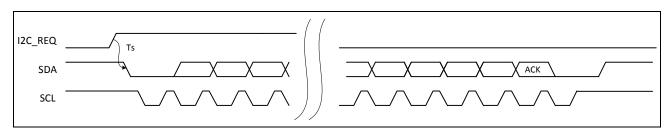

| Figure 12: I2C_REQ Timing Waveform                                                       | 34 |

| Figure 13: BSC Host Interface                                                            | 35 |

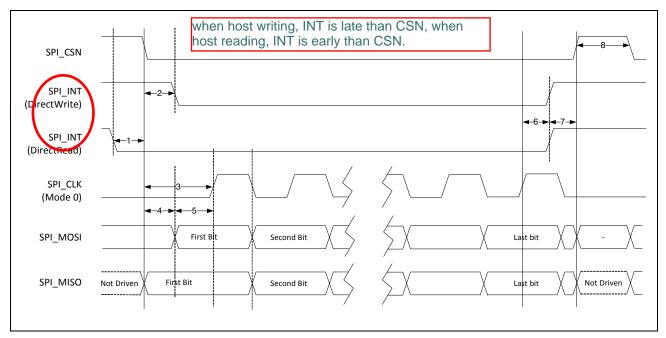

| Figure 14: SPI Timing Diagram                                                            | 36 |

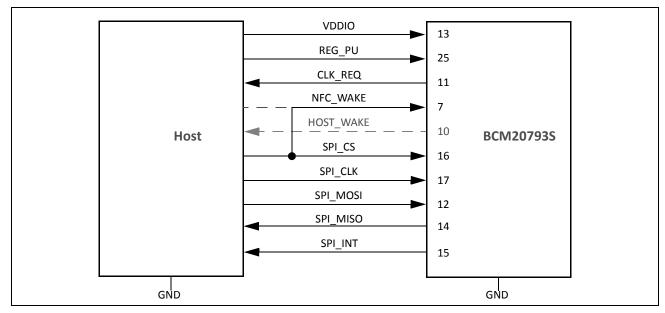

| Figure 15: SPI Host Interface                                                            | 38 |

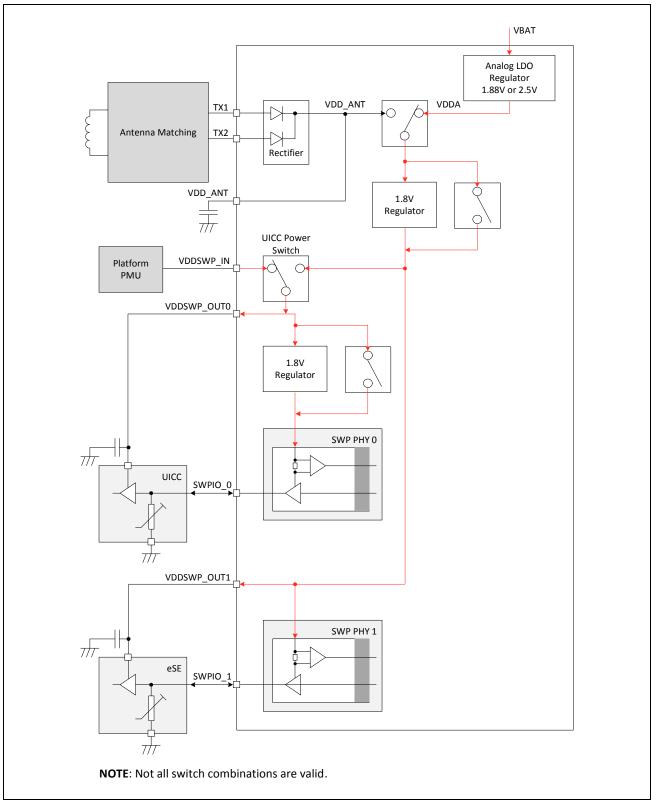

| Figure 16: Secure Element Power Switching Architecture                                   | 41 |

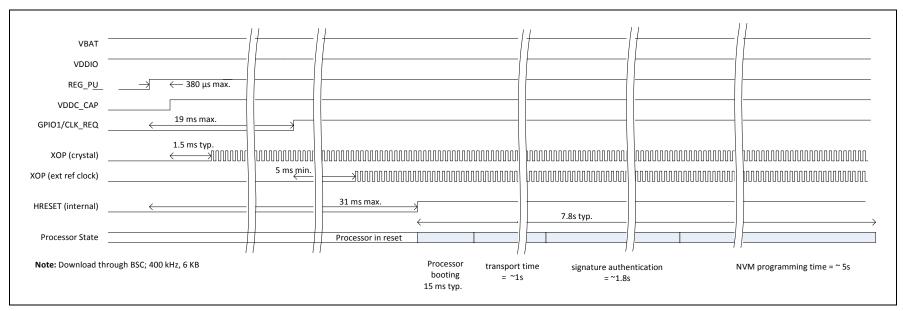

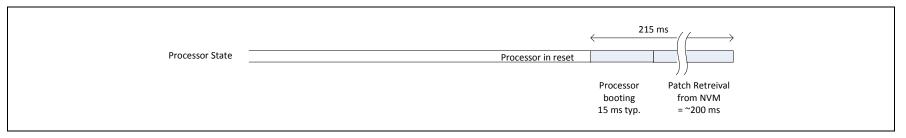

| Figure 17: Estimated Time for Downloading a Secured Patch and Configuration to NVM       | 44 |

| Figure 18: Estimated Time for Cold Bootup and Patch and Configuration Retrieval from NVM | 44 |

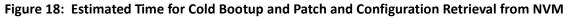

| Figure 19: Recommended Oscillator Configuration                                          | 46 |

| Figure 20: Pin Diagram                                                                   | 55 |

| Figure 21: Recommended Antenna Interface Circuit 1                                       | 56 |

| Figure 22: Recommended Antenna Interface Circuit 2                                       | 56 |

| Figure 23: QFN-34L Package Dimensions                                                    | 58 |

# **List of Tables**

| Table 1: ISO/IEC 14443 A and B, FeliCa, and NFC Forum Modes                    |

|--------------------------------------------------------------------------------|

| Table 2: ISO/IEC 15693 Supported Bit Rates       15                            |

| Table 3: Antenna Drive Range    16                                             |

| Table 4: Power Sources in CE Levels                                            |

| Table 5: Transitions Controlled by the Host    25                              |

| Table 6: Transitions Controlled Through the VBAT Monitor         27            |

| Table 7: Host Interface Transport Selection                                    |

| Table 8: UART Host Interface Pin Operation         32                          |

| Table 9: I2C_REQ Timing Parameters                                             |

| Table 10: BSC Host Interface Pin Operation         35                          |

| Table 11: SPI Timing Details                                                   |

| Table 12: SPI Host Interface Pin Operation         39                          |

| Table 13: Crystal Oscillator and External Clock – Requirements and Performance |

| Table 14: Recommended Operating Conditions         48                          |

| Table 15: LDO Current Limits                                                   |

| Table 16: Absolute Maximum Ratings49                                           |

| Table 17: Digital Input Voltage Level Specifications         51                |

| Table 18: Digital Output Voltage Level Specifications         51               |

| Table 19: Digital Output Rise and Fall Times       51                          |

| Table 20: Current Consumption Figures52                                        |

| Table 21: Pin List                                                             |

| Table 22: Package Thermal Characteristics Per JEDEC Standards                  |

| Table 23: Environmental Characteristics                                        |

| Table 24: Ordering Information         59                                      |

# About This Document

### **Purpose and Audience**

This document is for design engineers responsible for adding a BCM20793S NFC controller to mobile devices to enable contactless payment, contactless ticketing, easy pairing of wireless devices (Bluetooth and Wi-Fi), etc. Sections of this document include the NFC subsystem, interfaces, microprocessor and memory unit, and specifications of the BCM20793S.

## **Acronyms and Abbreviations**

In most cases, acronyms and abbreviations are defined on first use.

Acronyms and abbreviations in this document are also defined in Appendix A: "Acronyms," on page 60.

For a comprehensive list of acronyms and other terms used in Broadcom documents, go to: <a href="http://www.broadcom.com/press/glossary.php">http://www.broadcom.com/press/glossary.php</a>.

## References

The references in this section may be used in conjunction with this document.

**Note:** Broadcom provides customer access to technical documentation and software through its Customer Support Portal (CSP) and Downloads & Support site (see Technical Support).

For Broadcom documents, replace the "xx" in the document number with the largest number available in the repository to ensure that you have the most current version of the document.

| Doc | ument (or Item) Name                                                                                                                    | Number                                | Source       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|

| Bro | adcom Items                                                                                                                             |                                       |              |

| [1] | Current Consumption While Polling                                                                                                       | 20791-AN1xx-R                         | Broadcom CSP |

| Oth | er Items                                                                                                                                |                                       |              |

| [2] | Identification cards – Contactless integrated circuit cards –<br>Proximity cards– Part 2: Radio frequency power and signal<br>interface | ISO/IEC 14443-2:2010                  | www.iso.org/ |

| [3] | Identification cards – Contactless integrated circuit(s) cards<br>– Proximity cards – Part 3: Initialization and anticollision          | ISO/IEC 14443-3:2001                  | www.iso.org/ |

| [4] | Identification cards – Contactless integrated circuit cards–<br>Proximity cards Part 4: Transmission protocol                           | ISO/IEC 14443-4:2008<br>(2nd Edition) | www.iso.org/ |

| [5] | Identification cards – Contactless integrated circuit cards –<br>Vicinity cards – Part 2: Air interface and initialization              | ISO/IEC 15693-2:2006                  | www.iso.org/ |

| Doc | ument (or Item) Name (Cont.)                                                                                                                              | Number               | Source                           |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------|

| [6] | Identification cards – Contactless integrated circuit cards –<br>Vicinity cards – Part 3: Anticollision and transmission<br>protocol                      | ISO/IEC 15693-3:2009 | www.iso.org/                     |

| [7] | Information technology – Telecommunications and<br>information exchange between systems – Near Field<br>Communication – Interface and Protocol (NFCIP-1)  | ISO/IEC 18092:2004   | www.iso.org/                     |

| [8] | Information technology – Telecommunications and<br>information exchange between systems – Near Field<br>Communication Interface and Protocol -2 (NFCIP-2) | ISO/IEC 21481:2005   | www.iso.org/                     |

| [9] | Specification of implementation for integrated circuit(s)<br>cards – Part 4: High Speed proximity cards                                                   | JIS (X) 6319-4       | <u>http://</u><br>www.jisc.go.jp |

# **Technical Support**

Broadcom provides customer access to a wide range of information, including technical documentation, schematic diagrams, product bill of materials, PCB layout information, and software updates through its customer support portal (<u>https://support.broadcom.com</u>). For a CSP account, contact your Sales or Engineering support representative.

In addition, Broadcom provides other product support through its Downloads & Support site (<u>http://www.broadcom.com/support/</u>).

# Section 1: Introduction

# **General Description**

The BCM20793S is a fully NFC-compliant, highly integrated, low power, low cost, 40 nm NFC controller combined with an integrated EEPROM for battery-off operation in a single package. The BCM20793S is an update to the BCM20793 that features secure configuration and patch download for applications involving the management and operation of NFC secure elements. The BCM20793S size-optimized architecture is housed in a QFN-34L package that measures 4.0 mm × 4.5 mm × 0.9 mm (nominal), and requires minimal external components. This brings the traditional two-chip NFC controller and EEPROM for battery-off operation into a single package solution to minimize PCB footprint (see the architecture block diagram in Figure 1 on page 2).

The BCM20793S is designed for low-power mobile applications. It is based on over 15 years of Radio Frequency Identification (RFID) and NFC experience. The IP base that comprises the BCM20793S is the first in a family of products that targets the entire NFC ecosystem. Follow-on devices will include multiradio (Bluetooth, Wi-Fi, FM, GPS) combo chips, making the BCM20793S an ideal starting point for mobile customers looking for a clear path to cost and board space reduction.

The BCM20793S is designed to be an integral part of all NFC standards-compliant systems.

The BCM20793S has the same dual Single Wire Protocol (SWP) secure element interfaces as the BCM20792S, but brings the EEPROM option for battery-off operation to be internal to the package. The BCM20793S is package and pin-compatible with the BCM20794S (which has integral secure element) using minimal external link component changes. The BCM20793S incorporates the PPSE and AID routing functionality for support of multiple applications across multiple secure elements and execution environments, and also supports application tunneling to secure elements over SWP.

## **Features**

### **NFC Features**

- Support for the ISO/IEC 18092, ISO/IEC 21481, ISO/IEC 14443 Types A, B and B', Japanese Industrial Standard (JIS) (X) 6319-4, and ISO/IEC 15693 standards

- No active components requirement for antenna or field-power conditioning

- Individual byte framing

- Hardware-based collision detection and modulation controls

- Reader/Writer (R/W) mode

- Active and Passive Peer (P2P) mode

- Tag/Card Emulation mode:

- Support for battery-enabled card emulation mode

- Support for two levels of "residual" battery-assisted card emulation mode

- Support for completely powered from the field (battery-off) card emulation mode

- Dual Single Wire Protocol (SWP) interfaces:

- SWP\_0 with platform PMU power switching to UICC SIM card.

- SWP\_1 for embedded secure element or secondary UICC SIM cards

- Supports application tunnelling to secure elements over SWP

- Co-packaged CAT24C64 EEPROM:

- 64 Kb (8 KB) for battery-off personality, persistence and PPSE/AID routing data storage

- Supports AID routing between host and secure element(s)

- Internal low-power oscillator for periodic wake-up and mode switch operation

- Low-Power Target Detection mode for extremely low average current consumption "sniff mode"

- NFC Forum NFC Controller Interface (NCI) for host interface

## **General Features**

- Integral Low-Drop Out (LDO) regulator for direct connection to platform battery

- Clock sourced from platform reference frequency input for minimum BOM (or external XTAL option)

- ARM Cortex<sup>®</sup>-M0 with 128 KB ROM and 19 KB RAM

- Supports UART, SPI, and BSC (I<sup>2</sup>C-compatible) host interfaces

- Multiple low power modes for flexible power management

- Low-power consumption in all modes and support for field-power mode

- Minimum hardware size and BOM

# Applications

- Contactless payment

- Mobile handsets

- Simplified connectivity between wireless devices

- Contactless ticketing

- Peer mode transactions

- Smartposter tag reading/writing

- Access control

# Section 2: NFC Subsystem

# **Operational Modes**

The operational modes as defined by the NFC Forum and are supported by the BCM20793S. The following operational modes, as defined by the NFC Forum and NFC standards are supported by the BCM20793S.

### Peer Mode

The BCM20793S, along with its software stack, fully supports Peer mode. In Peer mode, the BCM20793S is capable of acting as both an initiator and a target.

This mode of operation allows for well-formed transmission of application data from one NFC device to another NFC device.

Peer mode utilizes the Link Layer Control Protocol (LLCP) defined by the NFC Forum. The physical layer and portions of the MAC layer standards are defined in NFCIP-1 standard ISO/IEC 18092 (ECMA 340). A Peer mode initiator is responsible for beginning communication with a Peer mode target. The initiator is also responsible for generating the RF field. The BCM20793S supports both Active and Passive Communications modes.

## **Reader/Writer Mode**

In the Reader/Writer mode, the BCM20793S acts as a reader or writer of low-cost NFC Forum-defined contactless tags. There are four tag types that are mandated by the NFC Forum. Broadcom<sup>®</sup> is the exclusive supplier of Tag Type 1 – which is ideal for simple pairing, business card, and all nonpayment applications. For further information on the BCM20203, the Broadcom Topaz Tag (NFC Forum Tag 1), contact your Broadcom representative.

The BCM20793S is capable of detecting, reading, and writing to any of the NFC Forum-supported tag types.

## **Card Emulation Mode**

In Card Emulation mode, the NFC system issues and responds to commands in the same way as a contactless smart card. The use cases for Card and Tag Emulation mode include payment and ticketing.

The BCM20793S supports full Tag and Card Emulation mode when paired with a suitable Secure Element or host device.

## **ISO Standards**

The BCM20793S supports several RF and ISO standards at various bit rates, up to and including 424 Kbps. A list of the ISO and JIS standards that are supported by the BCM20793S are listed in Table 1.

#### Table 1: ISO/IEC 14443 A and B, FeliCa, and NFC Forum Modes

| Standard                       | Re  | Reader/Initiator |              |     | Tag/Target   |              |  |

|--------------------------------|-----|------------------|--------------|-----|--------------|--------------|--|

| Data Rate (kbps)               | 106 | 212              | 424          | 106 | 212          | 424          |  |

| ISO/IEC 14443 A                | ✓   | ✓                | ✓            | ~   | ✓            | ✓            |  |

| ISO/IEC 14443 B                | ✓   | ✓                | ✓            | ~   | ✓            | ✓            |  |

| ISO/IEC 14443 B – Prime        |     |                  |              | ~   | ✓            | ✓            |  |

| ISO/IEC 18092/ECMA 340 Active  | ✓   | ✓                | ✓            | ~   | ✓            | ✓            |  |

| ISO/IEC 18092/ECMA 340 Passive | ✓   | ✓                | ✓            | ~   | ✓            | ✓            |  |

| JIS (X) 6319-4 FeliCa          |     | $\checkmark$     | $\checkmark$ |     | $\checkmark$ | $\checkmark$ |  |

The BCM20793S also supports reader and tag modes for ISO/IEC 15693<sup>1</sup>. A list of supported bit rates can be found in Table 2.

#### Table 2: ISO/IEC 15693 Supported Bit Rates

| Communications Mode | VICC to VCD |              |                | VCD to VICC  |      |              |

|---------------------|-------------|--------------|----------------|--------------|------|--------------|

| Subcarrier          | Single Dual |              | N/A            |              |      |              |

| Data Rate (kbps)    | 6.62        | 26.48        | 6.67           | 26.69        | 1.65 | 26.48        |

| Reader Support      | ✓           | ✓            | _ <sup>a</sup> | _a           | ✓    | ✓            |

| Tag Support         | ✓           | $\checkmark$ | ✓              | $\checkmark$ | ✓    | $\checkmark$ |

a. Reader version supports only Single Subcarrier mode.

<sup>1.</sup> The host can define Single or Multiple State Machine capabilities, which can alter ISO/IEC 15693 availability. See "Multiple Technology Support and Automatic Standard Detection" on page 19 for more information.

## Radio Modes

The BCM20793S supports several modes of operation to enable the NFC use cases.

### **Initiator Mode**

As the initiator in either R/W or Peer mode, the BCM20793S will generate the field used for communication. The size of the field is subject to the antenna used and the current drive of the BCM20793S. The <u>peak antenna</u> <u>drive current is</u> determined by the effective impedance of the antenna network and the voltage drive setting. The BCM20793S supports some variable drive levels to assist in power management. The antenna drive strength is <u>software configurable</u> with the range dependant on the internal voltage option chosen, as shown in Table 3.

| Table 3: Antenna Drive Range |          |           |       |  |  |

|------------------------------|----------|-----------|-------|--|--|

| Internal Power Setting       | Minimum  | Maximum   | Steps |  |  |

| Low Supply Reader Mode       | 35 mA pk | 110 mA pk | 3 dB  |  |  |

| High Supply Reader Mode      | 70 mA pk | 200 mA pk | 3 dB  |  |  |

High Supply mode uses an internal analog rail of nominally 2.5V and Low Supply mode uses 1.88V, which can be monitored on the VDDA\_CAP pin.

### Mode Switch 搜寻Tag时,自身通过开关产生变化磁场且等待Tag的响应;Tag的 Antenna coil检测有变化磁场时即可产生电给自身应用。

To discover the presence of a tag or a Peer mode target while operating in Initiator mode, the BCM20793S supports mode switch polling according to the NFC Forum "Activity" specification. <u>Once set to active polling, the BCM20793S generates a field for a certain sequence of protocols and looks for a response.</u>

For maximum flexibility and optimal power management, the duration that the BCM20793S generates a field at each interval is also firmware configurable. The Mode switch, as defined by the NFC Forum "Activity" specification, consists of a series of discovery periods and is configured according to the NFC Forum NFC Controller Interface (NCI) specification. Currently, NCI specifications highlight two parameters to define the discovery period used by the firmware.

- Listen Duration (acting as a target): May range from 0 ms to 65535 ms in 1 ms increments.

- Total Duration (total of acting as a target and acting as an initiator): May range from 0 ms to 65535 ms in 1 ms increments.

The time available for acting as an initiator is Total Duration – Listen Duration. If the initiator polls do not need all this allocated time, then the BCM20793S may enter a power saving mode.

By configuring these three parameters (technology, interval, and duration) the user can optimize the BCM20793S for their particular use case, and make the appropriate system-level response time- and power-consumption trade-offs. For further details on the power consumption used in polling, see Broadcom application note *Current Consumption While Polling* (see Reference [1] on page 9).

The BCM20793S implements the NFC Forum-defined mode switch, which the host can use to configure and set the FW in the BCM20793S to periodically wake up and poll for targets of the various technology types.

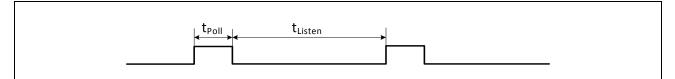

Figure 2: NFC Forum Mode Switch Polling and Listening

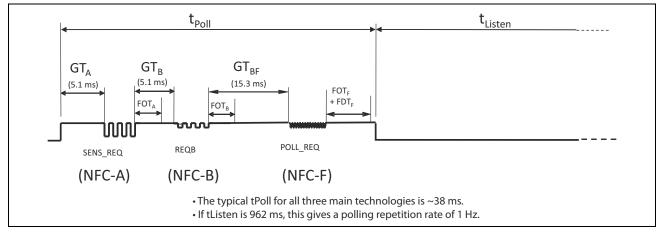

A typical poll cycle can be used to attempt to discover targets of NFC-A, NFC-B, and NFC-F. This involves generating the carrier field for approximately 38 ms and sending the REQA, REQB, and POLL\_F commands to activate and illicit a response from any tags or peer mode targets that are present.

Figure 3: Forum Mode Switch Polling for NFC-A, NFC-B, and NFC-F

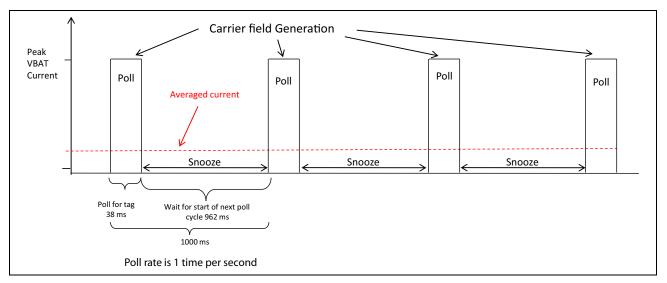

During the time of each poll event, the BCM20793S draws a peak current from the VBAT supply. The level of this peak current depends on the characteristics of the antenna design and the environment of the antenna, as well as internal drive level and gain settings within the BCM20793S configuration.

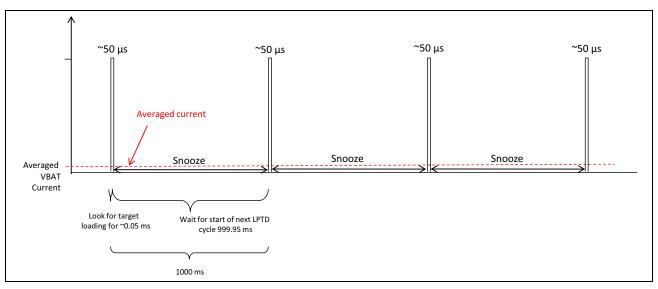

Figure 4: Representation of Averaged Duty-Cycle Current

### Low Power Target Detection

The BCM20793S has the ability to use a Low Power Target Detection (LPTD) mode, where a target can be an NFC tag, card, or an NFC device in Listener mode, to save current consumption (see Figure 5 on page 19). In this mode, the device periodically wakes and tries to sense the presence of a tag. It does so without initiating a full A, B, and F poll. If a tag load is detected, then normal A, B, and F polling is initiated. If a load or change in environment is not detected, then the device returns to its snooze state. Broadcom can demonstrate a significant saving using this feature. Contact your local Broadcom representative for additional details.

To fully optimize battery power usage, Broadcom has developed an efficient time/current algorithm for detecting the presence of a target by the BCM20793S.

Instead of the conventional mode switch poll sequence, the BCM20793S can "sniff" for very brief durations to detect the presence of a tuned circuit or disturbance of the environment in the proximity of the NFC antenna. This results in a very much reduced duration of field generation and peak current drain from 38 ms to ~50  $\mu$ s.

The "sniff" detects the presence of a target, but does not detect which technology type caused the trigger. The LPTD algorithm is always a precursor to a full poll event, which is used to qualify the trigger generated by the LPTD algorithm and discover the technology type just like a standard mode switch full poll event would.

A "false alarm rate" can occur when the LPTD can be triggered by metallic objects, but any trigger will be qualified by a full poll event and therefore can be discounted if it is not a real target.

The control algorithm includes a background calibration, so it auto-adjusts to a background baseline to account for drift and changing conditions.

Figure 5: Principle of Low Power Target Detection (LPTD) Mode

### Multiple Technology Support and Automatic Standard Detection

The BCM20793S has the ability to act as a Proximity Integrated Circuit Card (**PICC**) or Vicinity Integrated Circuit Card (**VICC**) for any of the technologies it supports (ISO/IEC 14443A, ISO/IEC 14443B, ISO/IEC 14443B-Prime, JIS (X) 6319-4, ISO/IEC 15693). The technology used is determined by both software configuration and the nature of the coupling device into the carrier field of which the BCM20793S is introduced.

The BCM20793S automatically detects and identifies, from the field generated by the initiator device, the technology that is requested. It then responds accordingly, assuming it has been configured by software to support a particular application on that given technology.

The BCM20793S has the capability of emulating targets of multiple technologies (A, B, F, ISO/IEC 15693, Calypso) at the same time. An NFC Forum initiator, following the activity specification, identifies all applications supported by targets in the field by polling using A, B, and F technologies. The initiator will then select one of the targets for subsequent communication.

The BCM20793S can emulate targets in two modes, and the mode can be changed over the NCI interface. In both modes, the BCM20793S supports emulation of multiple NFC-F targets.

In the default mode, the BCM20793S listen device maintains a single state machine and responds to the technology (A, B, F, ISO/IEC 15693, Calypso) of the first poll command that matches one of its emulated targets. After responding to this poll command, polls from other technologies are ignored until a carrier is dropped.

In the second mode, the BCM20793S listen device maintains multiple state machines and behaves virtually like multiple devices. This allows the host to have multiple applications listening at the same time, and announcing all of its applications to an NFC Forum initiator and not just the application of the first matching technology. For example, a BCM20793S-enabled device could announce both credit card emulation and LLCP. This is achieved by the BCM20793S responding to all polling commands (A, B, F, ISO/IEC 15693, Calypso) and only restrict itself to a specific technology once it has responded to the first non-polling command (A, B, F) or any ISO/IEC 15693 or Calypso command.

# **Power Supply Topology**

The BCM20793S integrates multiple LDO regulators and a Power Management Unit (PMU). All regulators are programmable via the PMU. These blocks simplify power supply design for NFC functionality in embedded designs. Main digital and analog regulator outputs are brought out to pins for decoupling.

A single <u>VBAT</u> (2.3V to 5.5V) and <u>VDDIO</u> (1.65V to 3.3V) can be used, with all additional voltages being provided by the regulators in the BCM20793S.

A control signal (**REG\_PU**, regulator power-up) is used to power-up the regulators and take the respective section out of reset. This signal provides a method for the host to override the operational control of the internal LDOs. REG\_PU operates on the VDDIO domain.

Applications that do not require control of the internal regulators can strap REG\_PU to VDDIO.

Even with REG\_UP deasserted, there is a low current always-on digital LDO that is used to keep-alive the state of important register settings within the front-end system. This uses residual power from the host battery to maintain the Card Emulation personality and persistence data.

### **NFC Power Management**

The BCM20793S has been designed with the stringent power consumption requirements of mobile devices in mind. All areas of the chip design are optimized to minimize power consumption. The PMU, in conjunction with the local MCU and firmware, enables and disables internal regulators and circuit blocks depending on the requirements of the operating modes selected. Clock speeds are dynamically changed (or gated altogether) for the current mode. Slower clock speeds are used wherever possible.

The BCM20793S main power states are described as follows:

- <u>Full power mode</u> All required regulators are enabled and the necessary circuit blocks are energized as

required for the NFC operation mode. The BCM20793S and the host device operate in all NFC operating

modes (i.e., Peer, Reader/Writer, and Card Emulation). There are various submodes within this level as

required to optimize the transient power operation of the BCM20793S host interfaces, the MCU, and NFC

subsystems.

- <u>Snooze standby mode</u> During operation of the NFC Forum Mode Switch, in between the polling events, the BCM20793S enters snooze standby mode, where the analog LDO is off and all main clocks (PLL and crystal oscillator) are shut down to reduce active power to the minimum. Only the LPO clock is running and available for the PMU sequencer. This is used to allow the PMU sequencer to wake up the chip and transition to full-power mode for the next poll event. In snooze mode, all firmware patches and configuration data is retained ready to restart the MCU and the primary power consumed is due to leakage current.

The carrier detector block is also running from the always-on LDO power domain to detect an external reader during the listen time in between polling events. When an external reader carrier field is detected, then the IC wakes up and enters Card Emulation and Peer Target modes.

## **Card Emulation Power Modes**

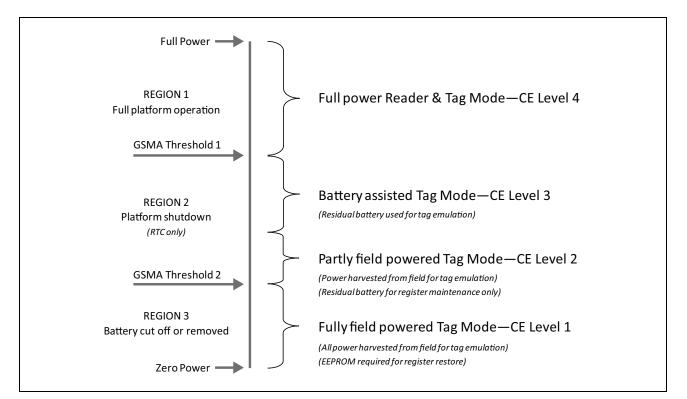

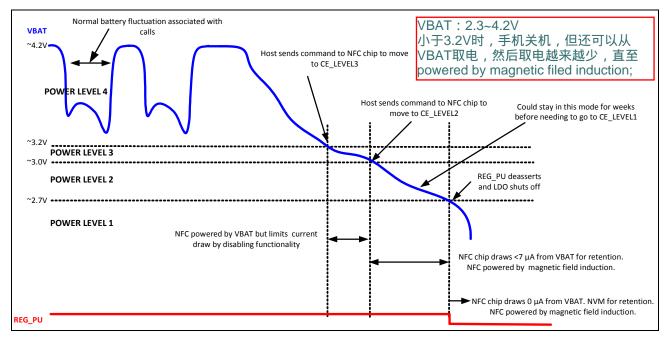

The BCM20793S has flexibility in its power modes to optimize NFC availability in card emulation (CE) mode to the user as the host battery capacity discharges and voltage level declines with time. As an option, this can extend to full Battery-off operation when the battery is deemed to be exhausted or even no longer present. The are two ways that the power levels can be controlled; either the BCM20793S can move between power modes under direct host control, or alternatively, the BCM20793S can be configured with a built-in  $V_{BATT}$  monitor circuit that can be pre-programmed by the host to have various pre-set voltage thresholds, such that when the battery voltage drops, the BCM20793S can automatically select and transition between the power level modes after the host is no longer available.

The BCM20793S can operate in CE mode with up to four sequential levels of battery power:

- CE Level 4 Power State

- CE Level 3 Power State

- CE Level 2 Power State

- CE Level 1 Power State

### **CE Level 4 Power State**

Level 4 is the full battery voltage mode when the device operates in card emulation mode only and where the BCM20793S can be put into a very low power standby state, but still have the ability to alert the host for any CE transactions. It is lower current than the snooze standby state because the SoC is powered down, but boot time is a little slower compared to the snooze standby state, so the hardware must handle the initial part of the CE transaction.

### **CE Level 3 Power State**

Level 3 is the residual power mode when the device operates in card emulation mode only. The operating power for the BCM20793S and Secure Element(s) is derived from the residual capacity of the battery supply. The preset tag personality and persistence data is retained in the NFC front-end registers, ready for immediate use.

### **CE Level 2 Power State**

Level 2 is the partially field-powered mode when the device only operates in card emulation modes. All power required for the BCM20793S (and the designated Secure Element) is derived from energy harvested from the illuminating field. Residual power from the battery is only used for a very low current drain necessary to keep register data ready for immediate use.

### **CE Level 1 Power State**

Level 1 is the fully field-powered mode where the device operates in card emulation mode only. This operating level will make use of the internal serial EEPROM. When the device is illuminated by a field and the BCM20793S harvests sufficient energy, the BCM20793S can retrieve the necessary personality and persistence data ready to respond to the reader/writer. The appropriate Secure Element is supplied with power from the BCM20793S, and the transaction can proceed to completion.

Devices without the battery-off personality storage medium may briefly enter Level 1, but the unsuccessful attempt to restore the personality and persistence data will abort communication.

Figure 6 shows how CE levels are mapped onto GSMA-recommended handset battery power regions.

Figure 6: Mapping CE Levels

### **CE Power Levels**

Figure 7 shows how CE power levels can be controlled automatically by the internal VBAT monitor.

Figure 7: CE Power Level Control

### Full Power Mode (R/W, P2P, and CE)

- System power is available and maintains NFC IP registers.

- The host devices and host interface transport are active.

- The Secure Element (UICC) is powered.

### **Snooze Standby Mode**

- System power is available and maintains NFC IP registers.

- The host has issued the SLEEP command.

- The low-power oscillator wakes up periodically for mode switch polling and LPTD.

- The carrier detector wakes up in CE mode when a reader is detected.

### CE Level 4 (CE Only)

- System power is available, but only used to maintain NFC registers.

- The host has issued the SLEEP command and the host interface transport is inactive.

- The carrier detector wakes up in CE mode when a reader is detected.

- The device must boot up the configuration and patch the download before operation. Transactions begin using hardware for time critical elements until the firmware is up.

### CE Level 3, Residual Battery Mode/Battery Assisted Mode (CE Only)

- The host device is inactive.

- System power is available at a reduced current for CE functionality.

- The Secure Element operates in low power mode, as defined in TS 102 613.

### CE Level 2, Residual Battery Mode/Partly Field-Powered Mode (CE Only)

- System power is used for register maintenance only.

- Power is harvested for actual card emulation and UICC SE operating in low power mode.

- Allows for very long life on residual battery.

### CE Level 1, Battery Off/Field Power Harvesting Mode (CE Only)

- No system power is available, registers are dead.

- Persistence data registers are restored from EEPROM.

- Power is harvested for everything.

| Table 4: | Power | Sources | in | CE Levels |

|----------|-------|---------|----|-----------|

|          |       |         |    | 02 201010 |

| Power Mode Level                             | Reader Subsystem | Persistence<br>Registers | Tag Subsystem | UICC or eSE   |

|----------------------------------------------|------------------|--------------------------|---------------|---------------|

| Full power initiator/<br>target (CE Level 4) | VBAT             | VBAT                     | VBAT          | VBAT          |

| Battery assisted<br>(CE Level 3)             | _                | VBAT                     | VBAT          | VBAT          |

| Partly field powered<br>(CE Level 2)         | _                | VBAT                     | Field powered | Field powered |

| Fully field powered (CE<br>Level 1)          | -                | -                        | Field powered | Field powered |

Power transitions controlled by the host are defined in Table 5.

| Power<br>State<br>Name | VDDIO<br>Present? | REG_PU<br>State | Entry           | Host Condition                                                                                                           | Host<br>Involvement  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NFC<br>Modes<br>Available | NFC<br>Power | SE<br>Power | 5    | EEPROM<br>Required |

|------------------------|-------------------|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|-------------|------|--------------------|

| Full<br>Power          | Yes               | REG_PU = 1      | Boot-up         | Handset Active<br>Note:<br>Depending on<br>requirements,<br>can also be in<br>Idle (screen<br>off) with LPTD<br>running. | Yes, by<br>HOST_WAKE | Full Power mode — All required regulators are enabled<br>and the necessary circuit blocks are energized as<br>required for the NFC operation mode. The<br>BCM20793S and the host device operate in all NFC<br>operating modes (that is, Peer, Reader/Writer, and<br>Card Emulation). There are various submodes within<br>this level as required to optimize the transient power<br>operation of the BCM20793S host interfaces, the<br>MCU, and NFC subsystems.                                                                                                                                                                                                                                                                 | R/W, P2P,<br>and CE       | VBAT         | VBAT        | VBAT | No                 |

| Snooze<br>Standby      | Yes               | REG_PU = 1      | Host<br>command | Handset Active<br>Note:<br>Depending on<br>requirements,<br>can also be in<br>Idle (screen<br>OFF) with<br>LPTD running. | Yes, by<br>HOST_WAKE | Snooze Standby mode — During operation of the NFC<br>Forum Mode Switch, in between the polling events,<br>the BCM20793S enters snooze standby mode, where<br>the analog LDO is off and all main clocks (PLL and<br>crystal oscillator) are shut down to reduce active<br>power to the minimum. Only the LPO clock is running<br>and available for the PMU sequencer. This is used to<br>allow the PMU sequencer to wake up the chip and<br>transition to Full-power mode for the next poll event.<br>In Snooze mode, all firmware patches and<br>configuration data is retained ready to restart the<br>MCU and the primary power consumed is due to<br>leakage current.<br>The carrier detector block is also running from the | R/W, P2P,<br>and CE       | VBAT         | VBAT        | VBAT | No                 |

|                        |                   |                 |                 |                                                                                                                          |                      | always-on LDO power domain to detect an external<br>reader during the listen time in between polling<br>events. When an external reader carrier field is<br>detected, then the IC wakes up and enters Card<br>Emulation and Peer Target modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                           |              |             |      |                    |

### Table 5: Transitions Controlled by the Host

| Power<br>State<br>Name | VDDIO<br>Present? | REG_PU<br>State  | Entry                 | Host Condition                                                                                      | Host<br>Involvement    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NFC<br>Modes<br>Available | NFC<br>Power | SE<br>Power |       | EEPROM<br>Required |

|------------------------|-------------------|------------------|-----------------------|-----------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|-------------|-------|--------------------|

| CE4                    | Yes               | REG_PU=1         | Host<br>command       | Handset Idle<br>(screen OFF)<br><b>Note:</b> Current<br>solution on<br>Android<br>(handbag<br>mode) | Yes<br>by<br>HOST_WAKE | Level 4 is the full battery voltage mode, in which the<br>device operates in card emulation mode only, and<br>where the BCM20793S can be put into a very low-<br>power standby state, but still have the ability to alert<br>the host for any CE transactions. Current is lower than<br>in the Snooze Standby state because the SoC is<br>powered down, but boot time is a little slower<br>compared to the Snooze Standby state, so the<br>hardware must handle the initial part of the CE<br>transaction.                                   | CE only                   | VBAT         | VBAT        | VBAT  | No                 |

| CE3                    | Yes               | REG_PU = 1       | Host<br>Command       | Not defined                                                                                         | No                     | Level 3 is the residual power mode, in which the<br>device operates in card emulation mode only. The<br>operating power for the BCM20793S and Secure<br>Element(s) is derived from the residual capacity of the<br>battery supply. The preset tag personality and<br>persistence data is retained in the NFC front-end<br>registers, ready for immediate use.                                                                                                                                                                                 | CE only                   | VBAT         | VBAT        | VBAT  | No                 |

| CE2                    | Yes               | REG_PU = 1       | Host<br>Command       | Not defined                                                                                         | No                     | Level 2 is the partially field-powered mode, in which<br>the device only operates in card emulation modes. All<br>power required for the BCM20793S (and the<br>designated Secure Element) is derived from energy<br>harvested from the illuminating field. Residual power<br>from the battery is only used for a very low current<br>drain necessary to keep register data ready for<br>immediate use.                                                                                                                                        | CE only                   | Field        | Field       | VBAT  | No                 |

| CE1                    | No                | Or<br>REG_PU = 0 | Or Battery<br>Removed | Handset OFF                                                                                         | No                     | Level 1 is the fully field-powered mode where the<br>device operates in card emulation mode only. This<br>operating level requires the option of a small-capacity<br>serial EEPROM IC. When the device is illuminated by a<br>field and the BCM20793S harvests sufficient energy,<br>the BCM20793S can retrieve the necessary personality<br>and persistence data ready to respond to the reader/<br>writer. The predesignated Secure Element is supplied<br>with power from the BCM20793S, and the transaction<br>can proceed to completion. | CE only                   | Field        | Field       | Field | Yes                |

Power transitions controlled through the VBAT Monitor are defined in Table 6. For VBAT Monitor-controlled transitions, the CE3-CE2 threshold can be configured in a range of 5.2–2V (the default is 3.2V), and the CE2-CE1 threshold can be configured in a range 3.2–2V (the default is 3.0V).

| Power<br>State<br>Name | VDDIO<br>present | REG_PU<br>state | Entry           | Host Condition                                                                                                                  | Host<br>Involvement  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NFC<br>Modes<br>Available | NFC<br>Power | SE<br>Power | -    | EEPROM<br>Required |

|------------------------|------------------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|-------------|------|--------------------|

| Full<br>Power          | Yes              | REG_PU = 1      | Boot-up         | Handset Active                                                                                                                  | Yes, by<br>HOST_WAKE | Full power mode — All required regulators are enabled<br>and the necessary circuit blocks are powered as<br>required for the NFC operation mode. The<br>BCM20793S and the host device operate in all NFC<br>operating modes (that is, Peer, Reader/Writer, and<br>Card Emulation). There are various submodes within<br>this level as required to optimize the transient power<br>operation of the BCM20793S host interfaces, the<br>MCU, and NFC subsystems.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W, P2P,<br>and CE       | VBAT         | VBAT        | VBAT | No                 |

| Snooze<br>Standby      | Yes              | REG_PU = 1      | Host<br>command | Handset Active<br><b>Note:</b><br>Depending on<br>requirements,<br>can also be in<br>Idle (screen<br>off) with LPTD<br>running. | Yes, by<br>HOST_WAKE | Snooze standby mode — During operation of the NFC<br>Forum Mode Switch, in between the polling events,<br>the BCM20793S enters Snooze Standby mode, where<br>the analog LDO is off and all main clocks (PLL and<br>crystal oscillator) are shut down to reduce active<br>power to the minimum. Only the LPO clock is running<br>and available for the PMU sequencer. This is used to<br>allow the PMU sequencer to wake up the chip and<br>transition to Full Power mode for the next poll event.<br>In Snooze Standby mode, all firmware patches and<br>configuration data are retained ready to restart the<br>MCU. The primary power consumed is due to leakage<br>current.<br>The carrier detector block is also running from the<br>always-on LDO power domain to detect an external<br>reader during the listen time in between polling<br>events. When an external reader carrier field is<br>detected, then the IC wakes up and enters Card<br>Emulation and Peer Target modes. | R/W, P2P,<br>and CE       | VBAT         | VBAT        | VBAT | No                 |

#### Table 6: Transitions Controlled Through the VBAT Monitor

| Table 6: | Transitions | Controlled | Through t | the VBAT | Monitor |

|----------|-------------|------------|-----------|----------|---------|

|----------|-------------|------------|-----------|----------|---------|

| Power<br>State<br>Name | VDDIO<br>present | REG_PU<br>state | Entry                                                   | Host Condition                                                                                      | Host<br>Involvement  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NFC<br>Modes<br>Available | NFC<br>Power | SE<br>Power |       | EEPROM<br>Required |

|------------------------|------------------|-----------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|-------------|-------|--------------------|

| CE4                    | Yes              | REG_PU = 1      | Host<br>command                                         | Handset Idle<br>(screen OFF)<br><b>Note:</b> Current<br>solution on<br>Android<br>(handbag<br>mode) | Yes, by<br>HOST_WAKE | Level 4 is the full battery voltage mode in which the<br>device operates in card emulation mode only, and<br>where the BCM20793S can be put into a very low-<br>power standby state, but still have the ability to alert<br>the host for any CE transactions. It is lower current<br>than the Snooze Standby state because the SoC is<br>powered down, but boot time is a little slower<br>compared to the Snooze Standby state, so the<br>hardware must handle the initial part of the CE<br>transaction.        | CE only                   | VBAT         | VBAT        | VBAT  | No                 |

| CE3                    | X                | REG_PU = 0      | Host<br>Command<br>and<br>REG_PU=0                      | Handset OFF                                                                                         | No                   | Level 3 is the residual power mode in which the device<br>operates in card emulation mode only. The operating<br>power for the BCM20793S and Secure Element(s) is<br>derived from the residual capacity of the battery<br>supply. The preset tag personality and persistence<br>data is retained in the NFC front-end registers, ready<br>for immediate use.                                                                                                                                                      | CE only                   | VBAT         | VBAT        | VBAT  | No                 |

| CE2                    | x                | REG_PU = 0      | Vbatt <<br>Threshold<br>CE3-C2                          | Handset OFF                                                                                         | No                   | Level 2 is the partially field-powered mode in which<br>the device only operates in the card emulation modes.<br>All power required for the BCM20793S (and the<br>designated Secure Element) is derived from energy<br>harvested from the illuminating field. Residual power<br>from the battery is only used for a very low current<br>drain necessary to keep register data ready for<br>immediate use.                                                                                                         | CE only                   | Field        | Field       | VBAT  | No                 |

| CE1                    | X                | REG_PU = 0      | VBAT <<br>Threshold<br>CE2-CE1<br>or Battery<br>Removed | Handset OFF                                                                                         | No                   | Level 1 is the fully field-powered mode where the device operates in card emulation mode only. This operating level requires the option of a small-capacity serial EEPROM IC. When the device is illuminated by a field and the BCM20793S harvests sufficient energy, the BCM20793S can retrieve the necessary personality and persistence data ready to respond to the reader/writer. The predesignated Secure Element is supplied with power from the BCM20793S, and the transaction can proceed to completion. | CE only                   | Field        | Field       | Field | Yes                |

# **Secure Element Configuration Options**

Figure 8 shows the NFC secure element configuration.

Figure 8: NFC Secure Element Configuration

## **Battery-off Source of Personality and Persistence Data**

For CE mode level 1 (field-powered operation), the BCM20793S requires a source of pre-configured storage for personality and persistence data. The BCM20793S uses the integral EEPROM to provide this.

# **Section 3: Interfaces**

## **Host Interfaces**

## Host Interface Selection

The BCM20793S supports UART, BSC (I<sup>2</sup>C-compatible), and SPI for the host interface transport physical layer.

The host interface type is selected on power up depending on the state of pin 15:

- Pin 15 strapped low UART

- Pin 15 strapped high BSC

- Pin 15 floating SPI

After boot, this becomes SPI\_INT output. During boot, the host must leave pin 15 floating (like a tri-state or input). The host must ignore interrupts from this line for 10 ms until after boot-up.

The interface signals are multiplexed onto common pins, as shown in Table 7.

| Pin | UART       | BSC        | SPI                                                 |

|-----|------------|------------|-----------------------------------------------------|

| 15  | Strap low  | Strap high | Floating at boot-up, then<br>becomes SPI_INT output |

| 12  | UART_TXD   | I2C_SDA    | SPI_MOSI                                            |

| 14  | UART_RTS_N | I2C_SCL    | SPI_MISO                                            |

| 16  | UART_CTS_N | I2C_REQ    | SPI_CS                                              |

| 17  | UART_RXD   | -          | SPI_CLK                                             |

#### Table 7: Host Interface Transport Selection

## UART

Following are the main features for the BCM20793S UART:

- UART 2-wire/4-wire: RXD, TXD, RTS, CTS

- Default baud rate is 115200 bps, host may change adjustable baud rates from 9600 bps to 3.0 Mbps

- RTS and CTS hardware flow control is supported

- Hardware auto baud circuit: Applications using this UART auto baud feature at other than the pre-defined frequencies (9.6, 13, 26, 19.2, 38.4, 52 MHz) should have the NFC\_WAKE pin pulled low on power-up.

- Optional in-band Xon/Xoff flow control

- 272-byte transmit FIFO and 272-byte receive FIFO

- Supports 8-bit characters with 1 or 2 stop bits and no parity

The UART timing waveform is shown in Figure 9.

Figure 9: UART Timing Waveform

The UART host interface is shown in Figure 10 and the pins are described in Table 8.

#### Figure 10: UART Host Interface

| Name       | Pin | 1/0 | Polarity                          | Description                                                                                                                                 |

|------------|-----|-----|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| VDDIO      | 13  | Р   | -                                 | I/O supply; externally regulated.                                                                                                           |

| REG_PU     | 25  | I   | Active high                       | Regulator power up.                                                                                                                         |

|            |     |     |                                   | Low: Shut down with all LDOs off (battery-off still functional).<br>High: LDOs are available.                                               |

| CLK_REQ    | 11  | 0   | Active high<br>(Not configurable) | Clock request. Signal to host requesting that it generate a reference clock input. Also a request to host PMU to power the UICC (SIM) card. |

| NFC_WAKE   | 7   | I   | Default is rising edge triggered. | NFC wake-up. If the BCM20793S is asleep, then the active edge will wake it up. The BCM20793S can subsequently re-                           |

| 高/低电平有效可   | 可由软 | 件设置 | (Configurable for falling edge.)  | enter sleep mode when it has no more activities to do.<br>Internal 50 kOhm pull-up; must be held low at device power-<br>up.                |

| HOST_WAKE  | 10  | 0   | Active high                       | Host wake-up. <u>A means for the chip to alert the host if the</u><br><u>BCM20793S wants to communicate with the host.</u>                  |

| UART_TXD   | 12  | 0   | -                                 | UART Transmit Data from BCM20793S to host.                                                                                                  |

| UART_RTS_N | 14  | 0   | Active low                        | UART request to send signal from BCM20793S to host that the BCM20793S is ready to accept receive data.                                      |

| UART CTS N | 16  | I   | Active low                        | UART clear to send signal from host to BCM20793S that the BCM20793S should send transmit data.                                              |

| UART_RXD   | 17  | I   | -                                 | UART Receive Data from host to BCM20793S.                                                                                                   |

#### Table 8: UART Host Interface Pin Operation

| Name | Pin | 1/0 | Polarity | Description                                                            |

|------|-----|-----|----------|------------------------------------------------------------------------|

| _    | 15  | I   | -        | Host interface mode control pin. Strapped to ground at boot up = UART. |

| Table 8: | UART Host Inter | face Pin | Operation | (Cont.) |

|----------|-----------------|----------|-----------|---------|

|----------|-----------------|----------|-----------|---------|

# BSC (I<sup>2</sup>C-Compatible)

If using IIC bus, NFC IIC bus is special and do not share with other module;

Following are the main features of the BCM20793S BSC host interface:

- Slave mode

- Low-speed mode (100 kbps), fast mode (400 kbps), and high-speed mode (3.4 Mbps) supported. Due to practical constraints imposed by parasitic capacitance and pull-up resistor values, especially in a multi-drop system, Broadcom engineers recommend that this be limited to 1.7 Mbps.

- 7-bit or 10-bit addressing mode; default boot-up of fixed 10-bit address (0x1FA), thereafter configurable to 7-bit or 10-bit addresses

- Dedicated TX and RX FIFOs, 272 bytes each.

- Digital deglitching filter implemented. Uses simple majority of 3 and will filter spikes up to 42 ns.

- High-speed reference not required for operation. (Certain accesses in sleep mode will initiate the wakeup function.)

The BSC timing waveform is shown in Figure 11.

#### Figure 11: BSC Timing Waveform

I2C\_REQ is an output signal from the BCM20793S to the host that it wishes to communicate. The timing diagram in Figure 12 shows I2C\_REQ as active high.

The I2C\_REQ signal stays high until after the first byte has been read by the host.

| Figure 12: | <b>I2C</b> | REO | Timing | Waveform  |

|------------|------------|-----|--------|-----------|

| Inguic IE. | 120        |     |        | waveloini |

#### Table 9: I2C\_REQ Timing Parameters

| Symbol | Description                               | Minimum | Maximum | Unit |

|--------|-------------------------------------------|---------|---------|------|

| Ts     | Rising edge of I2C_REQ to first SDA start | 0       | _       | ns   |

#### The BSC host interface is shown in Figure 13 and the pins are described in Table 10.

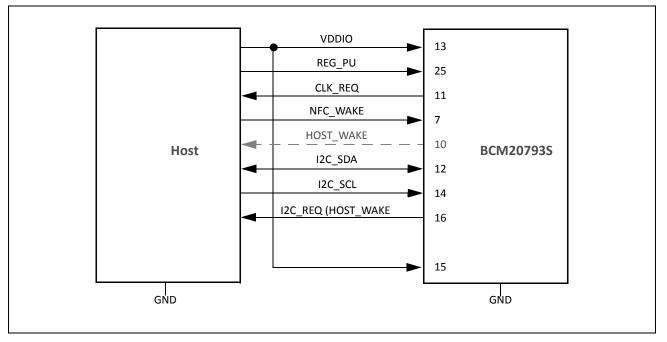

#### Figure 13: BSC Host Interface

| Name      | Pin | I/O | Polarity                                                                    | Description                                                                                                                                                                                                                                          |

|-----------|-----|-----|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDIO     | 13  | Р   | -                                                                           | I/O supply; externally regulated.                                                                                                                                                                                                                    |

| REG_PU    | 25  | I   | Active high                                                                 | Regulator power up.<br>Low: Shut down with all LDOs off (battery-off still functional).<br>High: LDOs are available.                                                                                                                                 |

| CLK_REQ   | 11  | 0   | Active high<br>(Not configurable)                                           | Clock request. Signal to host requesting that it generate a reference clock input. Also a request to host PMU to power the UICC (SIM) card.                                                                                                          |

| NFC_WAKE  | 7   | I   | Default is rising<br>edge triggered.<br>(Configurable for<br>falling edge.) | NFC wake-up. If the BCM20793S is asleep, then the active<br>edge will wake it up. The BCM20793S can subsequently re-<br>enter sleep mode when it has no more activities to do.<br>Internal 50 kOhm pull-up; must be held low at device power-<br>up. |