# WPCT301/NPCT501 Trusted Platform Module (TPM) Version 1.2 with I<sup>2</sup>C Interface

**Bus Interface**

I<sup>2</sup>C Bus Interface

– I<sup>2</sup>C Slave

Power Supply

Package

**Clocking and Supply**

On-Chip Clock Generator

— 3.3V supply operation

- Low standby power consumption

power supplies

- Up to 400 KHz clock operation (NPCT501)

- Separate pins for main  $(V_{DD})$  and standby  $(V_{SB})$

28-pin Thin Shrink Small Outline Package (TSSOP28)

#### **General Description**

NUVOTON

ounded by winhood

The Nuvoton WPCT301/NPCT501 family of single-chip Trusted Platform Modules (TPM) is a third-generation Nuvoton SafeKeeper<sup>™</sup> device that implements the TCG version 1.2 specification for PC-Client TPM with the addition of a serial data interface.

The WPCT301/NPCT501 is designed to reduce system power-up time and Trusted OS loading time. It provides a complete platform security solution for a wide range of computer systems.

#### Features

#### General

- Complete, single-chip TPM solution

- No external parts required

- Compatible with the Trusted Computing Group (TCG) TPM 1.2 Main

- Host Interface

- TPM 1.2 Interface (TIS) emulation

- Dedicated Interrupt signal

- Secure General-Purpose I/O (GPIO)

- Up to three GPIO pins

- I/O pins individually configured as input or output

- Configurable internal pull-up resistors

- TCG 1.2-defined interface

- Dedicated Physical Presence (PP) pin with configurable pull-up or pull-down resistor

- Tick Counter

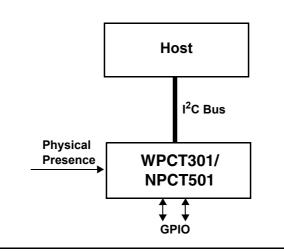

#### System Block Diagram

| <b>Revision Date</b> | Status        | Comments                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|----------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| February 2008        | Revision 0.9  | Preliminary Datasheet                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| March 2008           | Revision 1.0  | Preliminary Datasheet, second release                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| April 2008           | Revision 1.01 | Removed t <sub>WLB</sub> requirement<br>Fixed SPI_DO I/O definition in 1.3.1 Serial Interface<br>Fixed signal names in 3.4.3 I <sup>2</sup> C Timing and 3.4.4 SPI Timing diagrams<br>In 3.4.4 SPI Timing diagram, changed Max frequency of t <sub>SCK</sub> (SPI Timing) to<br>100 KHz                                                                                                                                   |  |  |  |

| June 2008            | Revision 1.02 | In 3.4.4 SPI Timing diagram, changed Max frequency of t <sub>SCK</sub> (SPI Timing) to 200 KHz<br>Replaced Figures 11 and 12 (page 20)                                                                                                                                                                                                                                                                                    |  |  |  |

| November 2009        | Revision 1.03 | Nuvoton revision. Changed logos and company name.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| January 2010         | Revision 1.04 | Order numbers changed (0WG to0WX)<br>Added description to SADD pin                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| August 2010          | Revision 1.05 | Changed power-well to V <sub>DD</sub> for all pins in <u>Section 1</u> (Signal/Pin Connection and Description).<br>Changed SADD description in <u>Section 1.3.3</u> .<br>Changed <u>Section 1.4</u> (Internal Pull-up and Pull-down Resistors).<br>Changed <u>Section 4.4.2</u> (Reset Timing).<br>Updated <u>Table 1</u> ("Buffer Types") and updated <u>Section 1.3</u> ("Signal/Pin Description") tables, accordingly. |  |  |  |

| December 2010        | Revision 1.10 | Removed references to the Nuvoton WPCT300 (SPI Interface).<br>Added the NPCT501 device.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| January 2011         | Revision 1.20 | Typo fixes.<br>Added TPM Host Interface description ( <u>Section 3</u> ).                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| March 2011           | Revision 1.30 | Changed $t_{SRST}$ max requirement from 2.5 s to none, in Power-Up Reset Timing table ( <u>Section 4.4.2</u> ).<br>Added $t_{RST.STA}$ to I <sup>2</sup> C Timing table ( <u>Section 4.4.3</u> ).                                                                                                                                                                                                                         |  |  |  |

| March 2011           | Revision 1.40 | Added NPCT501MA0WX order number to pinout diagram and back cover.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

# **Table of Contents**

| 1.0 | Sigr | nal/Pin Connection and Description                                                                 |    |

|-----|------|----------------------------------------------------------------------------------------------------|----|

|     | 1.1  | CONNECTION DIAGRAM                                                                                 | 4  |

|     | 1.2  | BUFFER TYPES AND SIGNAL/PIN DIRECTORY                                                              | 4  |

|     | 1.3  | SIGNAL/PIN DESCRIPTIONS                                                                            | 5  |

|     |      | 1.3.1 Serial Interface                                                                             | 5  |

|     |      | 1.3.2 Inputs and Outputs                                                                           | 5  |

|     |      | 1.3.3 Configuration Straps and Testing                                                             |    |

|     |      | 1.3.4 Power and Ground                                                                             |    |

|     |      | 1.3.5 Reserved                                                                                     |    |

|     | 1.4  | INTERNAL PULL-UP AND PULL-DOWN RESISTORS                                                           | 6  |

| 2.0 | Trus | sted Platform Module (TPM) Overview                                                                |    |

|     | 2.1  | SYSTEM CONNECTIONS                                                                                 | 7  |

|     | 2.2  | POWER MANAGEMENT (PM)                                                                              | 7  |

|     | 2.3  | HOST INTERFACE                                                                                     | 7  |

|     | 2.4  | RESET                                                                                              | 7  |

| 3.0 | TPN  | / Host Interface                                                                                   |    |

|     | 3.1  | SERIAL TPM INTERFACE PROTOCOL (TSIP)                                                               | 8  |

|     |      | 3.1.1 State Machine, Flow and Timeouts                                                             |    |

|     |      | 3.1.2 TIS Register Mapping                                                                         | 9  |

| 4.0 | Dev  | vice Specifications                                                                                |    |

|     | 4.1  | GENERAL DC ELECTRICAL CHARACTERISTICS                                                              |    |

|     |      | 4.1.1 Recommended Operating Conditions                                                             |    |

|     |      | 4.1.2 Absolute Maximum Ratings                                                                     |    |

|     |      | 4.1.3 Capacitance                                                                                  |    |

|     |      | 4.1.4 Power Consumption under Recommended Operating Conditions                                     |    |

|     | 4.2  | DC CHARACTERISTICS OF PINS BY I/O BUFFER TYPES                                                     |    |

|     |      | <ul><li>4.2.1 Input, TTL Compatible, with Schmitt Trigger</li><li>4.2.2 Input, Reset Pin</li></ul> |    |

|     |      | 4.2.2 Input, Reset Fill<br>4.2.3 Output, TTL/CMOS Compatible, Push-Pull Buffer                     |    |

|     |      | 4.2.4 Output, Open Drain Buffer                                                                    |    |

|     |      | 4.2.5 Notes and Exceptions                                                                         |    |

|     | 4.3  | INTERNAL RESISTORS                                                                                 | 14 |

|     |      | 4.3.1 Pull-Up Resistor                                                                             | 15 |

|     |      | 4.3.2 Pull-Down Resistor                                                                           | 15 |

|     | 4.4  | AC ELECTRICAL CHARACTERISTICS                                                                      |    |

|     |      | 4.4.1 AC Test Conditions                                                                           | 16 |

|     |      | 4.4.2 Reset Timing                                                                                 |    |

|     |      | Power-Up Reset                                                                                     |    |

|     |      | 4.4.3 I <sup>2</sup> C Timing                                                                      |    |

|     | 4.5  | PACKAGE THERMAL INFORMATION                                                                        | 20 |

$OD_n$ PWR

GND

Output, TTL/CMOS compatible, open-drain buffer capable of sinking n mA

and sinking n mA

Power pin

Ground pin

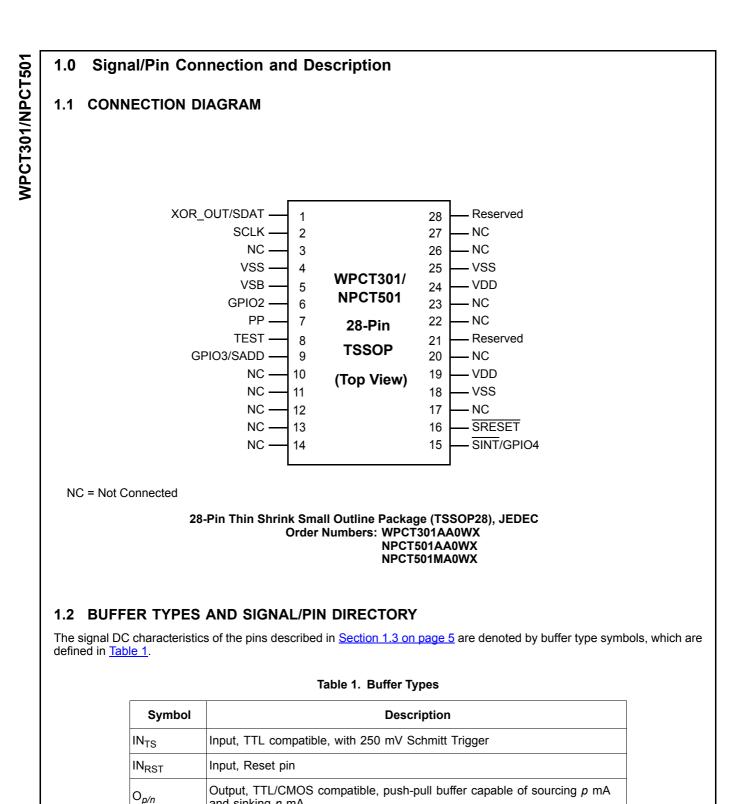

# 1.0 Signal/Pin Connection and Description (Continued)

#### **1.3 SIGNAL/PIN DESCRIPTIONS**

This section describes all signals of the WPCT301/NPCT501 device. The signals are organized by functional group.

#### 1.3.1 Serial Interface

| Signal | Pin(s) | I/O | Buffer Type                                             | Power Well      | Description                                                                                                        |  |  |

|--------|--------|-----|---------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| SDAT   | 1      | I/O | $IN_{TS}/OD_4$                                          | V <sub>DD</sub> | Serial Data In/Out. I <sup>2</sup> C data in/out.                                                                  |  |  |

| SCLK   | 2      | I/O | $IN_{TS}/OD_4$                                          | V <sub>DD</sub> | DD Serial Clock. I <sup>2</sup> C clock.                                                                           |  |  |

| SINT   | 15     | I/O | IN <sub>TS</sub> /OD <sub>8</sub> ,<br>O <sub>4/8</sub> | V <sub>DD</sub> | Serial Communication Command Completion Interrupt.<br>Active low as long as there is data on the output data FIFO. |  |  |

| SRESET | 16     | I   | IN <sub>RST</sub>                                       | V <sub>DD</sub> | Serial Reset. Host system reset used for the serial bus (Hardware reset).                                          |  |  |

#### 1.3.2 Inputs and Outputs

| Signal  | Pin(s)      | I/O | Buffer Type                                             | Power Well      | Description                                                                                                            |

|---------|-------------|-----|---------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------|

| PP      | 7           | Ι   | IN <sub>TS</sub>                                        | V <sub>DD</sub> | Physical Presence Input. Indicates owner's physical presence.                                                          |

| GPIO4-2 | 15, 9,<br>6 | I/O | IN <sub>TS</sub> /OD <sub>8</sub> ,<br>O <sub>4/8</sub> |                 | <b>General-Purpose I/O Port.</b> General-Purpose I/O pins compatible with the <i>PC Client TPM 1.2 Specification</i> . |

#### 1.3.3 Configuration Straps and Testing

| Signal  | Pin(s) | I/O | Buffer Type      | Power Well      | Description                                                                                                                                                                                                                                                                                      |

|---------|--------|-----|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST    | 8      | I   | IN <sub>TS</sub> | V <sub>DD</sub> | <b>Test Mode.</b> Sampled at $V_{DD}$ Power-Up reset to force the device pins into a XOR tree or TRI-STATE <sup>®</sup> configuration, as follows:<br>– No pull-up resistor (default) – Normal device operation<br>– 4.7 K $\Omega$ external pull-up resistor – Pins configured for Test mode.   |

| SADD    | 9      | I   | IN <sub>TS</sub> | V <sub>DD</sub> | <ul> <li>Serial Slave Address. Sampled at V<sub>DD</sub> Power-Up reset to select the slave address, as follows:</li> <li>No pull-down resistor - AEh (write) and AFh (read)</li> <li>10 KΩ external pull-down resistor - reserved for future implementation. Do not use this option.</li> </ul> |

|         |        |     |                  |                 | <b>Test Mode Selection.</b> Test mode (XOR tree or TRI-STATE) is selected by the sampled state of the SADD pin during VDD Power-Up reset. When SADD is sampled high, XOR Tree mode is selected. When SADD is sampled low, TRI-STATE mode is selected, floating all output pins.                  |

| XOR_OUT | 1      | 0   | O <sub>4/8</sub> | V <sub>DD</sub> | XOR Tree Output. This pin is the output of the XOR tree test logic.                                                                                                                                                                                                                              |

#### 1.3.4 Power and Ground

| Signal | Pin(s)       | I/O | Buffer Type | Power Well | Description                                                                                                             |  |

|--------|--------------|-----|-------------|------------|-------------------------------------------------------------------------------------------------------------------------|--|

| VSS    | 4, 18,<br>25 | I   | GND         |            | <b>Ground.</b> Ground connection for both core logic and I/O buffers, for the Main, Standby and Battery power supplies. |  |

| VDD    | 19, 24       | I   | PWR         |            | Main 3.3V Power Supply. Powers the I/O buffers of the GPIO ports and the serial interface.                              |  |

| VSB    | 5            | Ι   | PWR         |            | Standby 3.3V Power Supply. Powers the on-chip core.                                                                     |  |

# 1.0 Signal/Pin Connection and Description (Continued)

#### 1.3.5 Reserved

| Signal   | Pin(s)                         | Description                                                                                    |

|----------|--------------------------------|------------------------------------------------------------------------------------------------|

| NC       | 3, 10-14, 17, 20, 22-23, 26-27 | Not Connected. These pins must be left unconnected.                                            |

| Reserved | 21, 28                         | <b>Reserved.</b> These pins must be connected to an external 10 K $\Omega$ pull-down resistor. |

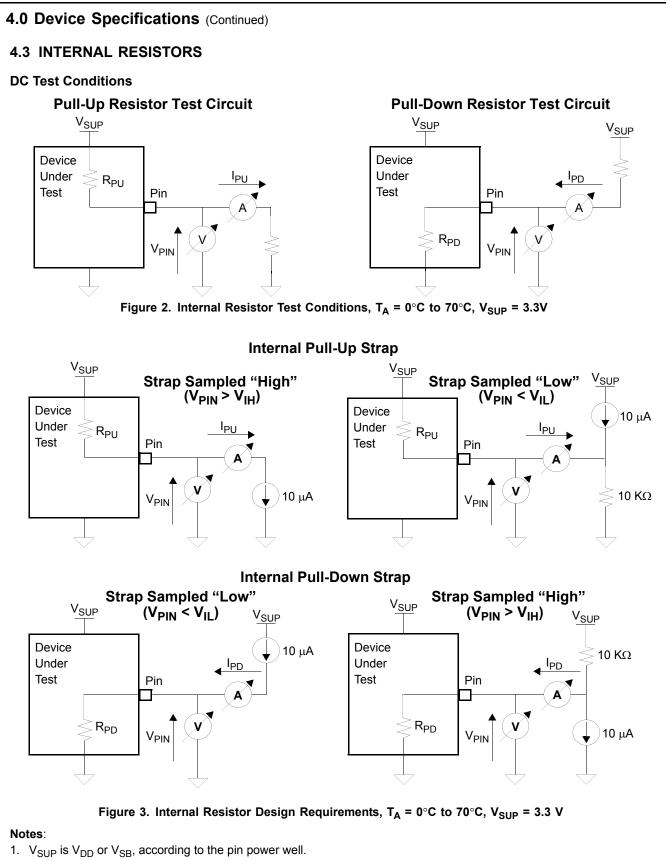

#### 1.4 INTERNAL PULL-UP AND PULL-DOWN RESISTORS

The signals listed in <u>Table 2</u> have internal pull-up (PU) and/or pull-down (PD) resistors. The internal resistors are optional for those signals indicated as "Programmable"

| Signal     | Pin(s) | Power Well      |                                    | vpe                                  | 0 - m m - m to                  |

|------------|--------|-----------------|------------------------------------|--------------------------------------|---------------------------------|

|            |        |                 | WPCT301                            | NPCT501                              | Comments                        |

| SINT/GPIO4 | 15     | V <sub>DD</sub> | PU <sub>66</sub>                   | PU <sub>110</sub>                    | GPIO4 Programmable <sup>1</sup> |

| GPIO3-2    | 9, 6   | V <sub>DD</sub> | PU <sub>66</sub>                   | PU <sub>110</sub>                    | Programmable                    |

| PP         | 7      | V <sub>DD</sub> | PU <sub>66</sub> /PD <sub>50</sub> | PU <sub>110</sub> /PD <sub>110</sub> | Programmable <sup>2</sup>       |

| TEST       | 8      | V <sub>DD</sub> | PD <sub>50</sub>                   | PD <sub>110</sub>                    | Strap                           |

| SADD       | 9      | V <sub>DD</sub> | PU <sub>66</sub>                   | PU <sub>110</sub>                    | Strap                           |

| SDAT       | 1      | V <sub>DD</sub> | PU <sub>66</sub>                   | PU <sub>110</sub>                    |                                 |

1. Controlled by TPM. Default at reset: GPIO4 disabled.

2. Controlled by TPM. Default at reset: pull-down enabled.

#### 2.0 Trusted Platform Module (TPM) Overview

The WPCT301/NPCT501 provides TPM functionality in TCG 1.2-compliant systems and is designed to best meet the requirements of embedded computer systems.

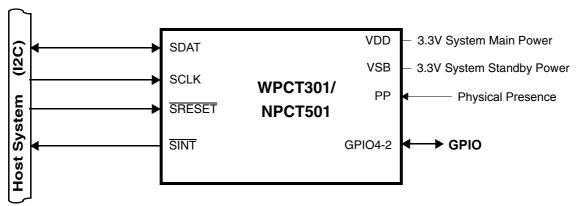

#### 2.1 SYSTEM CONNECTIONS

Figure 1 shows the system connections of the WPCT301/NPCT501 in a typical system.

Figure 1. WPCT301/NPCT501 System Connection Diagrams

TPM functions are all integrated on-chip. The major elements of the WPCT301/NPCT501 interface are:

- Host interface based on an I<sup>2</sup>C bus, with interrupt request.

- A physical presence input signal (PP) to indicate owner physical presence.

- GPIO signals (GPIO4-2), operated by TCG commands.

#### 2.2 POWER MANAGEMENT (PM)

The WPCT301/NPCT501 has an advanced power management scheme. The wake-up scheme enables the WPCT301/NPCT501 to respond to any kind of event that may require its attention. Power consumption is minimized by dynamically adjusting the internal power modes to the activity required by the host commands and other operations.

The security functions (core and associated peripherals) are supplied by  $V_{SB}$  power, which should be connected to the system standby power source (if standby power exists). If the system does not have a standby power source, use the system main power source instead (i.e., connect the system main power source to the VSB pin).

#### 2.3 HOST INTERFACE

The Host Bus Interface is based on a serial interface. This interface fully emulates the TIS registers (as defined in the *TCG PC Client-Specific Specification*.

#### 2.4 RESET

Serial reset performs the following actions:

- Resets host interface state machine.

- Resets the TPM interface host-controlled registers.

7

#### 3.0 TPM Host Interface

This chapter describes the TPM 1.2-compliant host interface.

#### 3.1 SERIAL TPM INTERFACE PROTOCOL (TSIP)

The WPCT301/NPCT501 TSIP implements the TIS register set accessible through the serial bus ( $l^2C$ ). The protocol state machine and register layout are implemented as defined in the *TIS Specification*. This section describes the state machine, sending commands to the TPM, reading results from the TPM, error handling, register mapping and communication sequences on the bus.

#### 3.1.1 State Machine, Flow and Timeouts

The state machine follows the definition in Section 11.3.11 ("Status Register") in the TIS Specification.

Use the sequence defined in *TCG PC Client Specific, Device Driver Design Principles, for TCG Version 1.2*, to send or receive command input/output parameters.

The TPM triggers SINT interrupt on the transition to Command Completion state. The SINT is an active-low signal, i.e., it goes low whenever **TPM\_STS.dataAvail** is set (and **TPM\_STS.valid** is set), and goes back high when **TPM\_STS.dataAvail** is cleared.

There are two methods for the host device driver to wait for the command execution to finish:

- Interrupt (recommended) SINT signal assertion (i.e., transition from high to low) triggers an interrupt in the host interrupt controller, followed by the host issuing the interrupt handler code.

- Polling Host device driver performs status polling by reading **TPM\_STS** register to check if **dataAvail** bit is set by TPM. In this method, it is recommended to add a delay between the consecutive reads of **TPM\_STS** register. <u>Table 3</u> shows the recommended values for delays:

#### Table 3. Delay Between Consecutive TPM\_STS Register Reads During Command Execution State

| Duration Since<br>TPM_STS.tpmGo Set | Recommended Delay between<br>Consecutive TPM_STS Reads |

|-------------------------------------|--------------------------------------------------------|

| 0 - 10 msec                         | 2 msec                                                 |

| more than 10 msec                   | 10 msec                                                |

When an error occurs (i.e., a timeout is reached) while in Command Reception or Execution states, abort the command at any point by setting **TPM\_STS.commandReady**. After which the command can be resent.

When an error occurs (timeout is reached) while in Command Completion state, set **TPM\_STS.ResponseRetry**, This causes the Nuvoton TPM to restart sending command output parameters.

The effects of setting TPM\_STS.commandReady in the different TPM communication states are as follows:

- In Ready state: Ignored stay in Ready state

- In Idle State: Enter Ready state, within **TIMEOUT** B

- In Command Reception state: This is an Abort.

- The TPM Write FIFO is cleared

- TPM enters Idle state

- Command can be resent

- In Command Completion state: This is an Abort

- The TPM Read and Write FIFO are cleared

- Enter Idle state

- In Command Execution state: This is an Abort

- TPM aborts current command execution

- The TPM Read and Write FIFO are cleared

- Enter Idle state

# WPCT301/NPCT501

# 3.0 TPM Host Interface (Continued)

#### 3.1.2 TIS Register Mapping

Table 4 shows the TIS register offset mapping in the TSIP space:

#### Table 4. TIS Register Offset Mapping in TSIP Space

| Offset | : Register Name <sup>1</sup> | R/W              | Page<br>Size<br>(bytes) | Description                                                                              |

|--------|------------------------------|------------------|-------------------------|------------------------------------------------------------------------------------------|

| 00h    | TPM_STS                      | R/W <sup>2</sup> | 2                       | Status Register. Provides TIS status.                                                    |

| 20h    | TPM_WR_FIFO                  | WO               | 32                      | Write this register to send input command parameters during Command Reception state.     |

| 40h    | TPM_RD_FIFO                  | RO               | 32                      | Read this register to receive output command parameters during Command Completion state. |

| 60h    | TPM_DID_VID_RID              | RO               | 4                       | Vendor, device and revision ID:<br>- WPCT301: 00FE1050h<br>- NPCT501: 47FE1050h          |

1. For a detailed description of these registers, see the *TIS Specification*.

2. Offset 0 is R/W while offset 1 (burstCount) is RO.

Any TIS register writing or reading data is processed and **TPM\_STS** register updated (including **burstCount** field) on an I<sup>2</sup>C STOP condition.

Any part of a command's input parameter write operation to **TPM\_WR\_FIFO** should start at offset 20h.

Any part of a command's output parameter read operation to **TPM\_RD\_FIFO** should start at offset 40h.

# 4.0 Device Specifications

# 4.1 GENERAL DC ELECTRICAL CHARACTERISTICS

#### 4.1.1 Recommended Operating Conditions

| Symbol          | Parameter                 | Min | Тур | Мах | Unit |

|-----------------|---------------------------|-----|-----|-----|------|

| V <sub>DD</sub> | Main 3V Supply Voltage    | 3.0 | 3.3 | 3.6 | V    |

| V <sub>SB</sub> | Standby 3V Supply Voltage | 3.0 | 3.3 | 3.6 | V    |

| T <sub>A</sub>  | Operating Temperature     | 0   |     | +70 | °C   |

#### 4.1.2 Absolute Maximum Ratings

Absolute maximum ratings are values beyond which damage to the device may occur. Unless otherwise specified, all voltages are relative to ground (V<sub>SS</sub>).

| Symbol           | Parameter                         | Conditions                                         | Min  | Мах                   | Unit |

|------------------|-----------------------------------|----------------------------------------------------|------|-----------------------|------|

| V <sub>SUP</sub> | Supply Voltage <sup>1</sup>       |                                                    | -0.3 | +4.1                  | V    |

| VI               | Input Voltage                     |                                                    | -0.3 | V <sub>DD</sub> + 0.5 | V    |

| V <sub>O</sub>   | Output Voltage                    |                                                    | -0.3 | V <sub>DD</sub> + 0.5 | V    |

| T <sub>STG</sub> | Storage Temperature               |                                                    | -65  | +165                  | °C   |

| PD               | Power Dissipation                 |                                                    |      | 1                     | W    |

| ΤL               | Lead Temperature Soldering (10 s) |                                                    |      | +260                  | °C   |

|                  | ESD Tolerance                     | $C_{ZAP}$ = 100 pF<br>$R_{ZAP}$ = 1.5 K $\Omega^2$ | 2000 |                       | V    |

1.  $V_{SUP}$  is  $V_{DD}$ ,  $V_{SB}$ . 2. Value based on test complying with RAI-5-048-RA human body model ESD testing.

#### 4.1.3 Capacitance

| Symbol          | Parameter              | Conditions | Min | Typ <sup>1</sup> | Max | Unit |

|-----------------|------------------------|------------|-----|------------------|-----|------|

| C <sub>IN</sub> | Input Pin Capacitance  |            |     | 4                | 5   | pF   |

| C <sub>IO</sub> | I/O Pin Capacitance    |            |     | 8                | 10  | pF   |

| C <sub>O</sub>  | Output Pin Capacitance |            |     | 6                | 8   | pF   |

1. T<sub>A</sub> = 25°C; f = 1 MHz.

| Symbol            | Parameter                                                 | Conditions <sup>1</sup>                             | Тур | Мах | Unit |

|-------------------|-----------------------------------------------------------|-----------------------------------------------------|-----|-----|------|

| I <sub>DD</sub>   | V <sub>DD</sub> Average Supply Current                    | $V_{IL}$ = 0.5V, $V_{IH}$ = 2.4V, No Load           | 5   | 10  | mA   |

| I <sub>SB</sub>   | V <sub>SB</sub> Average Supply Current                    | $V_{IL}$ = 0.5V, $V_{IH}$ = 2.4V, No Load           | 20  | 50  | mA   |

| I <sub>SBLP</sub> | $V_{SB}$ Quiescent Supply Current in Idle $\mbox{Mode}^2$ | $V_{IL}$ = $V_{SS}$ , $V_{IH}$ = $V_{SB}$ , No Load | 300 | 700 | μA   |

#### 4.1.4 Power Consumption under Recommended Operating Conditions

1. All parameters specified for  $0^{\circ}C \le T_A \le 70^{\circ}C$ ;  $V_{DD}$  and  $V_{SB}$  = 3.3V ±10% unless otherwise specified. 2. Device is not performing any operation; no Serial bus activity.

#### 4.2 DC CHARACTERISTICS OF PINS BY I/O BUFFER TYPES

The tables in this section summarize the DC characteristics of all device pins described in <u>Chapter 1.2 on page 4</u>. The characteristics describe the general I/O buffer types defined in <u>Table 1 on page 4</u>.

#### 4.2.1 Input, TTL Compatible, with Schmitt Trigger

#### Symbol: $IN_{TS}$

| Symbol              | Parameter             | Conditions                                                       | Min  | Мах                                | Unit |

|---------------------|-----------------------|------------------------------------------------------------------|------|------------------------------------|------|

| $V_{\text{IH}}$     | Input High Voltage    |                                                                  | 2    | V <sub>SUP</sub> <sup>1</sup> +0.5 | V    |

| $V_{IL}$            | Input Low Voltage     |                                                                  | -0.3 | 0.8                                | V    |

| $V_{H}$             | Input Hysteresis      |                                                                  | 300  |                                    | mV   |

| . 2                 | Innut Lookono Current | $V_{\rm SUP}$ = 3.0V - 3.6V and 0 < $V_{\rm IN}$ < $V_{\rm SUP}$ |      | ±10                                | μA   |

| ا <sub>الـK</sub> 2 | Input Leakage Current | $V_{\rm SUP}$ = 3.0V - 3.6V and $V_{\rm SUP}$ < $V_{\rm IN}$     |      | ±10                                | μA   |

1.  $V_{SUP}$  is  $V_{DD}$  or  $V_{SB}$  according to the power well of the input.

2. Input leakage current includes the output leakage of the bidirectional buffers with TRI-STATE outputs. For additional conditions, see Section 4.2.5 on page 13.

#### 4.2.2 Input, Reset Pin

#### Symbol: IN<sub>RST</sub>

| Symbol          | Parameter             | Conditions                                                                    | Min                 | Мах                  | Unit |

|-----------------|-----------------------|-------------------------------------------------------------------------------|---------------------|----------------------|------|

| V <sub>IH</sub> | Input High Voltage    |                                                                               | 0.5 V <sub>DD</sub> | V <sub>DD</sub> +0.5 | V    |

| V <sub>IL</sub> | Input Low Voltage     |                                                                               | -0.3                | 0.3 V <sub>DD</sub>  | V    |

| . 1             | Innut Lookono Cumont  | $V_{\text{DD}}$ = 3.0V - 3.6V and 0 < $V_{\text{IN}}$ < $V_{\text{DD}}$       |                     | ±10                  | μA   |

| IILK            | Input Leakage Current | $V_{\rm DD}$ = 3.0V-3.6V and $V_{\rm DD}{<}V_{\rm IN}{<}$ $V_{\rm DD}{+}0.5V$ |                     | ±10                  | μA   |

1. Input leakage current includes the output leakage of the bidirectional buffers with TRI-STATE outputs. For additional conditions, see Section 4.2.5 on page 13.

#### 4.2.3 Output, TTL/CMOS Compatible, Push-Pull Buffer

#### Symbol: Op/n

Output, TTL/CMOS Compatible, rail-to-rail push-pull buffer that is capable of sourcing *p* mA and sinking *n* mA.

| Symbol                        | Parameter              | Conditions                                                                         | Min                 | Max | Unit |

|-------------------------------|------------------------|------------------------------------------------------------------------------------|---------------------|-----|------|

| N                             | Output High Voltage    | I <sub>OH</sub> = - <i>ρ</i> mA                                                    | 2.4                 |     | V    |

| V <sub>OH</sub>               |                        | I <sub>OH</sub> = -50 μA                                                           | $V_{SUP}^{1} - 0.2$ |     | V    |

| N/                            |                        | $I_{OL} = n mA$                                                                    |                     | 0.4 | V    |

| V <sub>OL</sub>               | Output Low Voltage     | I <sub>OL</sub> = 50 μA                                                            |                     | 0.2 | V    |

| 1 2                           | Output Lookago Current | $V_{SUP}$ = 3.0V - 3.6V and 0 < $V_{IN}$ < $V_{SUP}$                               |                     | ±10 | μA   |

| I <sub>OLK</sub> <sup>2</sup> | Output Leakage Current | $\rm V_{SUP}$ = 3.0V - 3.6V and $\rm V_{SUP}$ < $\rm V_{IN}$ < $\rm V_{SUP}$ +0.5V |                     | ±10 | μA   |

1.  $V_{SUP}$  is  $V_{DD}$  or  $V_{SB}$  according to the power well of the input.

2. Output leakage current includes the input leakage of the bidirectional buffers with TRI-STATE outputs. For additional conditions, see <u>Section 4.2.5 on page 13</u>.

# WPCT301/NPCT501

# 4.0 Device Specifications (Continued)

# 4.2.4 Output, Open Drain Buffer

#### Symbol: OD<sub>n</sub>

Output, Open Drain capable of sinking *n* mA.

| Symbol             | Parameter              | Conditions                                                                         | Min | Мах | Unit |

|--------------------|------------------------|------------------------------------------------------------------------------------|-----|-----|------|

| N/                 |                        | $I_{OL} = n mA$                                                                    |     | 0.4 | V    |

| V <sub>OL</sub>    | Output Low Voltage     | I <sub>OL</sub> = 50 μA                                                            |     | 0.2 | V    |

| . 1                | Output Lookage Current | $\rm V_{SUP}$ = 3.0V - 3.6V and 0 < $\rm V_{IN}$ < $\rm V_{SUP}$                   |     | 10  | μA   |

| I <sub>OLK</sub> ' | Output Leakage Current | $\rm V_{SUP}$ = 3.0V - 3.6V and $\rm V_{SUP}$ < $\rm V_{IN}$ < $\rm V_{SUP}$ +0.5V |     | 10  | μA   |

1. Output leakage current includes the input leakage of the bidirectional buffers with TRI-STATE outputs. For additional conditions, see <u>Section 4.2.5 on page 13</u>.

#### 4.2.5 Notes and Exceptions

- 1.  $I_{ILK}$  and  $I_{OLK}$  are measured in the following cases (where applicable):

- Internal pull-up or pull-down resistor is disabled

- Push-pull output buffer is disabled (TRI-STATE mode)

- Open-drain output buffer is at high level

- Some pins have an internal static pull-up resistor (when enabled) and therefore may have leakage current from V<sub>SUP</sub> (when V<sub>IN</sub> = 0). See <u>Section 1.4 on page 6</u> for a list of the relevant pins.

- Some pins have an internal static pull-down resistor (when enabled) and therefore may have leakage current to GND (when V<sub>IN</sub> = V<sub>SUP</sub>). See <u>Section 1.4 on page 6</u> for a list of the relevant pins.

- The following strap pins have an internal static pu<u>ll-up</u> resistor enabled during Power-Up reset and therefore may have leakage current from V<sub>SB</sub> (when V<sub>IN</sub> = 0): SADD, TEST.

- 5.  $I_{OH}$  is valid for a GPIO pin only when it is not configured as open-drain.

- In XOR Tree mode, the buffer type of the input pins included in the XOR tree is IN<sub>T</sub> (Input, TTL compatible), regardless

of the buffer type of these pins in normal device operation mode.

- 2. The equivalent resistance of the pull-up resistor is calculated by  $R_{PU} = (V_{SUP} V_{PIN}) / I_{PU}$ .

- 3. The equivalent resistance of the pull-down resistor is calculated by  $R_{PD}$  =  $V_{PIN}$  /  $I_{PD}$ .

#### 4.3.1 Pull-Up Resistor

#### Symbol: PUnn

| Symbol          | Parameter                     | Conditions <sup>1</sup> | Min <sup>2</sup> | Typical | Max <sup>2</sup> | Unit |

|-----------------|-------------------------------|-------------------------|------------------|---------|------------------|------|

| R <sub>PU</sub> | Pull-up equivalent resistance | V <sub>PIN</sub> = 0V   | <i>nn</i> – 50%  | nn      | nn + 66%         | KΩ   |

1. TA = 0°C to 70°C,  $V_{SUP}$  = 3.3V. 2. Not tested; guaranteed by characterization.

#### 4.3.2 Pull-Down Resistor

#### Symbol: PD<sub>nn</sub>

| Symbol          | Parameter                       | Conditions <sup>1</sup> | Min <sup>2</sup> | Typical | Max <sup>2</sup> | Unit |

|-----------------|---------------------------------|-------------------------|------------------|---------|------------------|------|

| R <sub>PD</sub> | Pull-down equivalent resistance | $V_{PIN} = V_{SUP}$     | nn – 50%         | nn      | nn + 120%        | KΩ   |

1. TA = 0°C to 70°C,  $V_{SUP}$  = 3.3V. 2. Not tested; guaranteed by characterization.

#### 4.4 AC ELECTRICAL CHARACTERISTICS

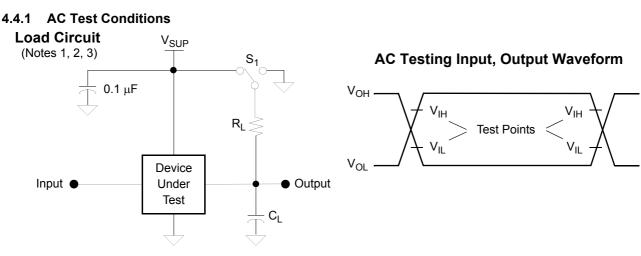

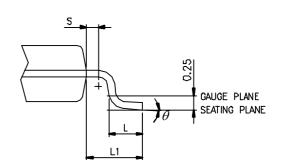

Figure 4. AC Test Conditions,  $T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V_{SUP} = 3.0V - 3.6V$

#### Notes:

- 1. V<sub>SUP</sub> is V<sub>DD</sub> or V<sub>SB</sub> according to the power well of the pin.

- 2.  $C_{I}$  = 50 pF for all output pins except the following pin groups (values include both jig and oscilloscope capacitance):

- $S_1 = Open for push-pull output pins.$   $S_1 = V_{SUP} for high impedance to active low and active low to high-impedance transition measurements.$  $<math>S_1 = GND for high impedance to active high and active high to high-impedance transition measurements.$

$R_{I} = 1.0 \text{ K}\Omega - \text{for all pins.}$

3. The following abbreviations are used in <u>Section 4.4</u>: RE = Rising Edge; FE = Falling Edge

#### Definitions

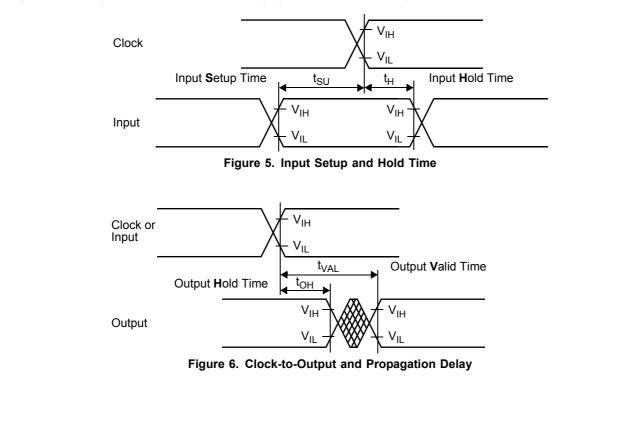

The timing specifications in this section are relative to V<sub>IL</sub> or V<sub>IL</sub> (according to the specific buffer type) on the rising or falling edges of all the signals, as shown in the following figures (unless specifically stated otherwise).

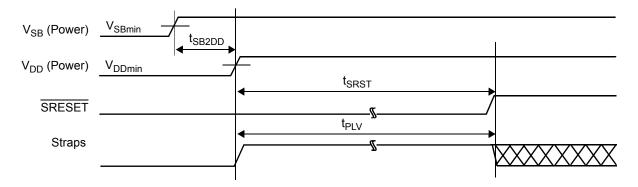

#### 4.4.2 Reset Timing

#### **Power-Up Reset**

| Symbol             | Description                                   | Reference Conditions                            | Min <sup>1</sup> | Max <sup>2</sup> |

|--------------------|-----------------------------------------------|-------------------------------------------------|------------------|------------------|

| t <sub>SB2DD</sub> | Time between standby and main supply voltage  | Before end of reset                             | 0 ms             |                  |

| t <sub>SRST</sub>  | SRESET active time                            | $V_{DD}$ power-up to end of $\overline{SRESET}$ | 10 ms            |                  |

| t <sub>PLV</sub>   | Strap valid time                              | Before end of reset                             | 10 ms            |                  |

| t <sub>EPLV</sub>  | External strap pull-down resistor, valid time | Before end of reset                             | 10 ms            |                  |

Not Tested; Guaranteed by design.

Not Tested; Guaranteed by design.

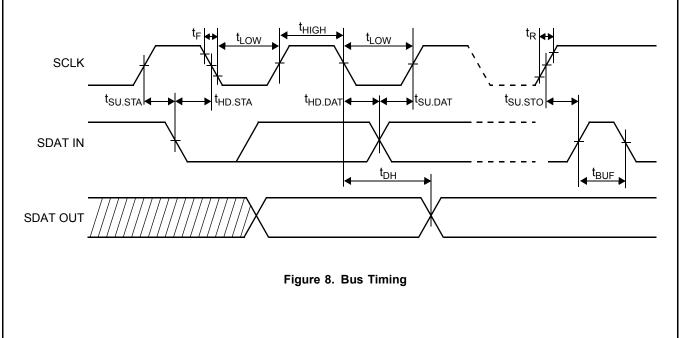

# 4.4.3 I<sup>2</sup>C Timing

|                       |                                                                            | Min         |             | Мах              |                  |       |

|-----------------------|----------------------------------------------------------------------------|-------------|-------------|------------------|------------------|-------|

| Symbol                | Description                                                                | WPCT<br>301 | NPCT<br>501 | WPCT<br>301      | NPCT<br>501      | Units |

| f <sub>SCL</sub>      | Clock frequency, SCL                                                       | 50          | 50          | 100 <sup>1</sup> | 400 <sup>2</sup> | KHz   |

| t <sub>LOW</sub>      | Clock pulse width, low                                                     | 4.7         | 1.1         |                  |                  | μS    |

| t <sub>HIGH</sub>     | Clock pulse width, high                                                    | 4.0         | 1.0         |                  |                  | μS    |

| t <sub>BUF</sub>      | Time that the bus must be available before the start of a new transmission | 4.7         | 1.1         |                  |                  | μS    |

| t <sub>HD.STA</sub>   | Start hold time                                                            | 4.0         | 1.0         |                  |                  | μS    |

| t <sub>SU.STA</sub>   | Start setup time                                                           | 4.7         | 1.1         |                  |                  | μS    |

| t <sub>HD.DAT</sub>   | Data in hold time                                                          | 0           | 0           |                  |                  | μS    |

| t <sub>SU.DAT</sub>   | Data in setup time                                                         | 200         | 200         |                  |                  | ns    |

| t <sub>R</sub>        | Input rise time                                                            |             |             | 1000             | 250              | ns    |

| t <sub>F</sub>        | Input fall time                                                            |             |             | 300              | 250              | ns    |

| t <sub>SU.STO</sub>   | Stop setup time                                                            | 4.7         | 1.1         |                  |                  | μS    |

| t <sub>DH</sub>       | Data out hold time                                                         | 300         | 300         |                  |                  | ns    |

| t <sub>WR</sub>       | Write/read cycle time                                                      |             |             | 20               | 20               | μS    |

| t <sub>INIT.STA</sub> | Start condition after V <sub>SB</sub> power-up                             | 100         | 100         |                  |                  | ms    |

| t <sub>RST.STA</sub>  | Start condition after SRESET deassertion                                   | 30          | 30          |                  |                  | ms    |

1. Test conditions:  $R_L = 1 \text{ K}\Omega$  to  $V_{DD}=3.3\text{V}$ ,  $C_L = 400 \text{ pF}$  to GND 2. Test conditions for 100 KHz:  $R_L = 1 \text{ K}\Omega$  to  $V_{DD}=3.3\text{V}$ ,  $C_L = 400 \text{ pF}$  to GND; Test conditions for 400 KHz:  $R_L = 1 \text{ K}\Omega$  to  $V_{DD}=3.3\text{V}$ ,  $C_L = 100 \text{ pF}$  to GND

Note: Write/read cycle time (t<sub>WR</sub>) = the time from a valid write/read sequence stop condition until the end of an internal operation.

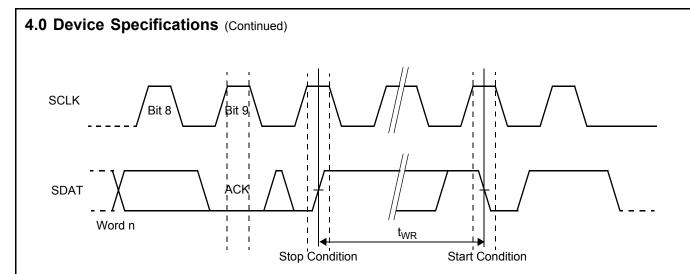

Figure 9. Cycle, Start, Stop and Acknowledge Timing

WPCT301/NPCT501

#### 4.5 PACKAGE THERMAL INFORMATION

Thermal resistance (degrees C/W) Theta<sub>JC</sub> and Theta<sub>JA</sub> values for the WPCT301/NPCT501 packages are as follows:

| Package Type | Theta <sub>JA</sub> @0 lfpm | Theta <sub>JA</sub> @150 lfpm | Theta <sub>JA</sub> @250 lfpm | Theta <sub>JA</sub> @500 lfpm | Theta <sub>JC</sub> |

|--------------|-----------------------------|-------------------------------|-------------------------------|-------------------------------|---------------------|

| TSSOP28      | 29                          | 27                            | 25                            | 23                            | 10                  |

Table 5. Theta ( $\Theta$ ) J Values

Note: Airflow for Theta $_{JA}$  values is measured in linear feet per minute (Ifpm).

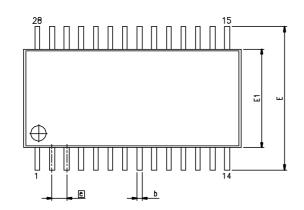

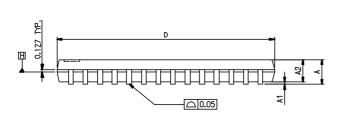

#### **Physical Dimensions**

#### VARIATIONS (ALL DIMENSIONS SHOWN IN MM)

| SYMBOLS  | MIN.     | NOM. | MAX. |

|----------|----------|------|------|

| А        | _        | -    | 1.20 |

| A1       | 0.00     | -    | 0.15 |

| A2       | 0.80     | 1.DO | 1.05 |

| Ь        | 0.19     | -    | 0.30 |

| D        | 9.60     | 9.70 | 9.80 |

| E1       | 4.30     | 4,40 | 4.50 |

| E        | 6.40 BSC |      |      |

| e        | 0.65 BSC |      |      |

| L1       | 1.00 REF |      |      |

| L        | 0.45     | 0.60 | 0.75 |

| 5        | 0.20     | -    | _    |

| $\theta$ | Ċ        | _    | 8.   |

|          |          |      |      |

#### 28-Pin Thin Shrink Small Outline Package (TSSOP28), JEDEC Order Numbers: WPCT301AA0WX NPCT501AA0WX NPCT501MA0WX

#### Important Notice

Nuvoton products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Furthermore, Nuvoton products are not intended for applications wherein failure of Nuvoton products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.

Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper use or sales.

Headquarters No. 4, Creation Rd. 3, Science-Based Industrial Park, Hsinchu, Taiwan, R.O.C TEL: 886-3-5770066 FAX: 886-3-5665577 http://www.nuvoton.com.tw (Chinese) http://www.nuvoton.com (English)

Taipei Office

9F, No.480, Rueiguang Rd.,

Neihu District, Taipei, 114,

Taiwan, R.O.C.

TEL: 886-2-2658-8066

FAX: 886-2-8751-3579

Nuvoton Technology Corporation America 2727 North First Street, San Jose, CA 95134, U.S.A. TEL: 1-408-544-1718 FAX: 1-408-544-1787

Winbond Electronics Corporation Japan NO. 2 Ueno-Bldg., 7-18, 3-chome Shinyokohama Kohoku-ku, Yokohama, 222-0033 TEL: 81-45-4781881 FAX: 81-45-4781880 Nuvoton Technology (Shanghai) Ltd. 27F, 2299 Yan An W. Rd. Shanghai, 200336 China TEL: 86-21-62365999 FAX: 86-21-62365998

Nuvoton Technology (H.K.) Ltd. Unit 9-15, 22F, Millennium City 2, 378 Kwun Tong Rd., Kowloon, Hong Kong TEL: 852-27513100 FAX: 852-27552064

For Advanced PC Product Line information contact: APC.Support@nuvoton.com

Please note that all data and specifications are subject to change without notice. All trademarks of products and companies mentioned in this document belong to their respective owners.

www.nuvoton.com