## **Acapella Optical Modem IC**

## **ACS405CS Main Features**

- \* Full duplex serial transmission through a single fiber-optic cable without the need for expensive WDM devices.

- E2 data-rates of 8.448Mbps or 4\*E1 at 2.048Mbps.

T2 data rates of 6.312Mbps or 4\*T1 at 1.544Mbps.

- \* Link lengths up to 25km (50km at reduced bandwidth).

- \* Single wavelength of light to transmit and receive data.

- Low power, zero cross talk between Rx and Tx channels.

- Incorporates maintenance channel at 64kbps.

- Bit Error Rate (BER) of < 10<sup>-10</sup>

- Typical latency of 0.75ms.

- Ping Pong system supporting bi-directional Laser Duplex Devices or PPLEDs.

### **General Description**

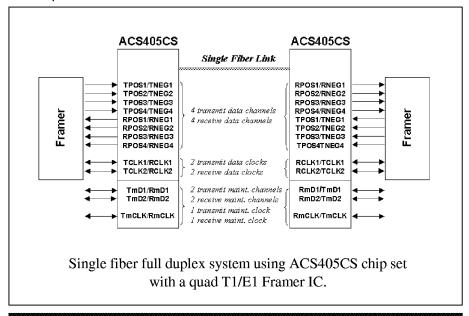

The ACS405CS is a complete controller, driver and receiver chip-set, supporting full-duplex synchronous transmission up to 8.448/6.312Mbps over a single-optical fiber. The designer can share the available bandwidth over 1 to 8 main channels by selecting the appropriate combination on the DR input pins. In addition to the main channels, the ACS405CS provides up to two auxilliary maintenance channel of 64kbps.

The internal machine cycle provides for link lengths up to 25/50km. On the electrical side HDB3/AMI/NRZ/B8ZS interfaces are selectable. Communicating modems automatically maintain synchronisation with each other, such that the receive phase of one modem is lined-up with the transmit phase of the other, compensating for the propagation delay presented by the link. Link lengths from zero to maximum distance are catered for automatically.

## **Acapella Optical Modem IC**

ACS405CS

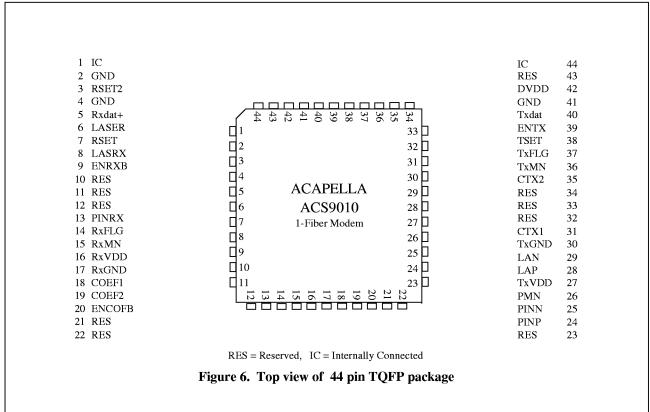

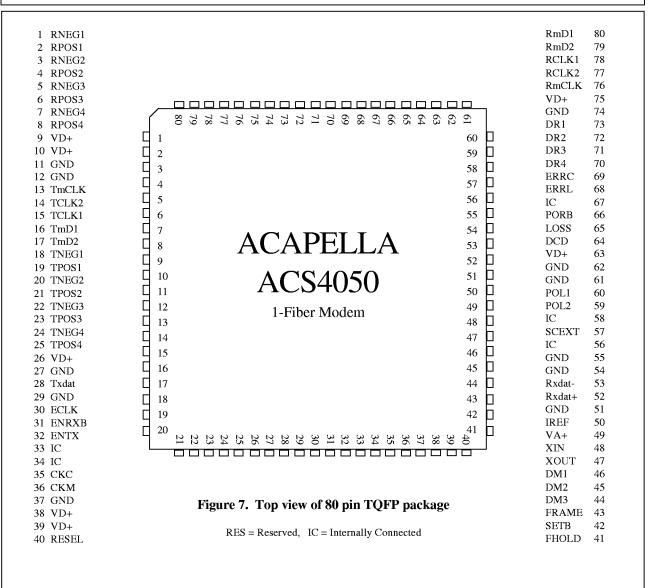

The ACS405CS comprises a chip-set of two highly integrated devices, the ACS9010 and ACS4050. The ACS9010 is an analogue device and the ACS4050 is predominately a digital device.

The ACS9010 contains the Laser/LED driver as well as the PIN receiver circuitry. Since the device does not transmit and receive concurrently (ping-pong), there is no risk of noise generated by the transmitter interfering with the sensitive receive circuitry.

The ACS4050 comprises the logic necessary to time compress and decompress the data, plus all the logic associated with window synchronisation and locking.

For the purpose of this specification the chip-set will be referred to as the ACS405CS and the individual devices as the ACS9010 or ACS4050.

#### **Inter-Modem Coding**

The inter-IC coding between communication modems is 8B10B. Whilst transparent to the user, 8B10B encoding ensures that there is no DC component in the signal, and provides frequent data transitions, factors which ease the task of data recovery and clock extraction.

The coding rules are continuously checked to ensure the integrity of the link, and errors are indicated on the ERRL and ERRC pins ( see section headed ERRC and ERRL - Error Detection ).

#### The Transmit and Receiver Functions

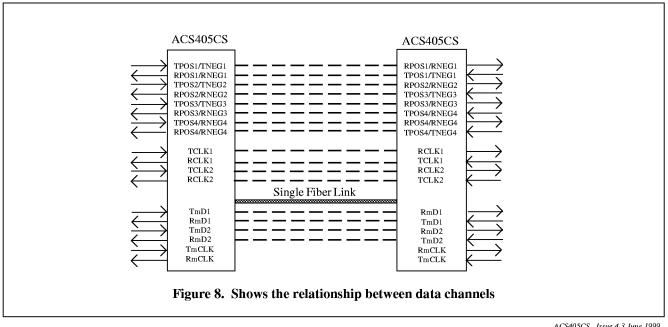

Data presented at the near-end TPOS/TNEG is time-compressed, encoded in the 8B10B format and transmitted over the link in a high frequency burst. The optical interface is then configured as a receiver ready to accept data from the far-end. The received data is decoded, time decompressed and de-jittered and then presented to the RPOS/RNEG data output pins.

#### **PORB**

The Power-On Reset (PORB) pin resets the device if forced low for 2ms or more. In normal operation PORB should be held High. It is recommended that PORB is connected to VD+ via a  $100 \mathrm{K}\Omega$  resistor and to GND via a  $100 \mathrm{nF}$  capacitor.

PORB has a special function when used in conjunction with memory lock (see section headed *Diagnostic Modes*).

#### **System Clock**

The system clock on the ACS405CS may be derived

from an external source or generated locally using the on-chip crystal oscillator. The oscillator (XTO/I) requires the use of a fundamental parallel resonance crystal with appropriate padding capacitors. The input pin, SCEXT should be connected to GND. The crystal specification should be:

Calibration tolerance: +/- 20ppm @ 25°C

Temp. tolerance: +/- 20ppm @ -40 to +85°C

Temperature range: -40 to +85°C

Load condition: parallel load 15pF

Padding capacitor: 18-22pF (tune for desired tolerance)

If it is required to drive the device with an externally generated system clock source, then the clock source should be connected to input pin ECLK with SCEXT connected to VD+. It is often more convenient to drive boards containing multi ACS405CS chip-sets from a single system clock source.

The system clock frequency is determined by the choice of data rates and is tabulated in section headed, *Data Rate Selection*. For example, for E2 operation, the appropriate frequency is 33.792MHz and for T2 operation, 31.560MHz.

The system clock defines the burst frequency at which data is transmitted over the optical link via the optical interface. The receive circuitry within the ACS4050 recovers the clock from the received data at the Rxdat inputs and produces a clock that is synchronised to the incoming data stream. The system clock must have a maximum tolerance of +/-50ppm over the desired temperature range.

#### **Optical Operational Modes**

The ACS405CS has four optical operational modes controlled by the pins LASER, LASRX and PINRX on the ACS9010 device. All of the duplex modes in Table 1 may be converted to dual fiber operation simply by interfacing to separate transmitting and receiving devices.

| Mode | Optical Device                  |

|------|---------------------------------|

| 1    | Laser Duplex using 4-pin Laser. |

| 2    | Laser Duplex using 3-pin Laser. |

| 3    | LED Duplex.                     |

| 4    | LED (ping-pong).                |

|      | Table 1                         |

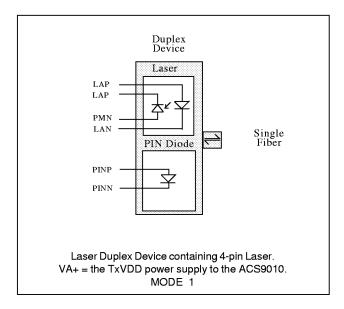

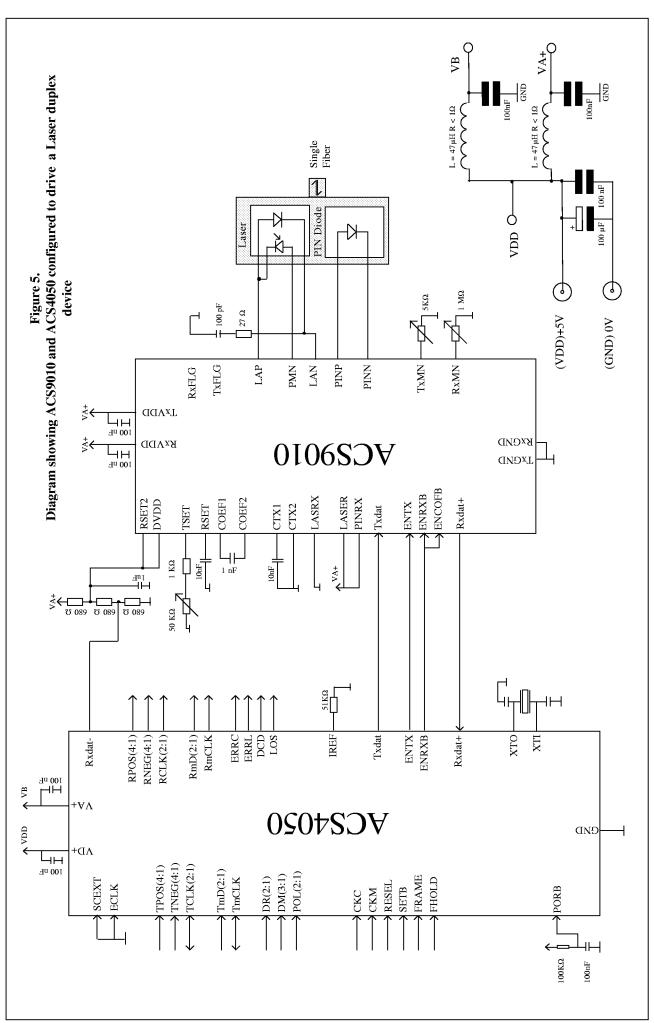

#### Mode 1 - Laser Duplex using 4-pin Laser

In mode 1, the device is configured for use with a Laser duplex device containing a 4-pin laser. The diagram below shows the connections to the ACS9010 device. The operational control pins found on the ACS9010 are configured as follows:

LASER = VA+ LASRX = GND PINRX = VA+

For the Bookham BKM-2101-A-02 transceiver module, the following connections should be made:

Monitor pd p side - pin2 = PMN Monitor pd n side - pin3 = LAP

Laser diode n side - pin5 = LAN Laser diode p side - pin6 = LAP Receive pd p side - pin9 = PINP

Receive pd n side - pin 10 = PINN pin 1, 4, 7, 8, 11, 14 should be tied to GND

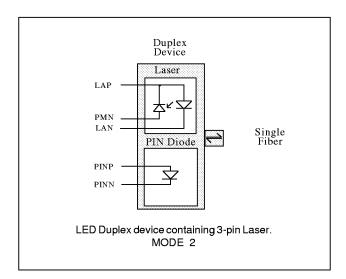

#### Mode 2 - Laser Duplex using 3-pin Laser

In mode 2, the device is configured for use with a Laser duplex device containing a 3-pin laser. The diagram below shows the connections to the ACS9010 device. The operational control pins found on the ACS9010 are configured as follows:

LASER = VA+LASRX = GNDPINRX = VA+

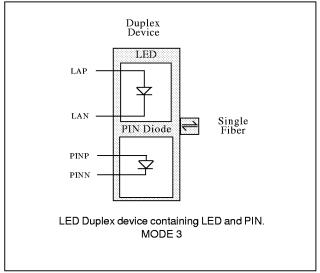

#### Mode 3 - LED Duplex Device

In mode 3, the device is configured for use with an LED duplex device. The diagram below shows the connections to the ACS9010 device. The operational control pins found on the ACS9010 are configured as follows:

LASER = GND LASRX = GND PINRX = VA+

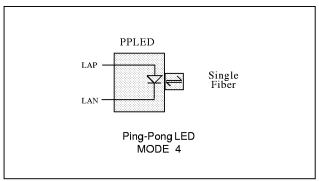

#### Mode 4 - LED Ping Pong

In mode 4, the modem is configured for use with a ping-pong LED device (PPLED). The diagram below shows the connections to the ACS9010 device.

Ping-Pong LEDs are standard LEDs which exhibit good photo-detection (high responsivity, low capacitance) characteristics when reverse biased. Ping-Pong LEDs are available from several manufacturers as well as from Acapella.

LASER = GND LASRX = VA+ PINRX = GND

#### Control of LED current

During the transmit cycle, the LED drive current is directly proportional to the programmed reference current. To minimise switching delay, a permanent bias current is maintained through the LED. The data modulation produces bursts of high light and low light to represent logic high and low levels respectively. The low light level is set by a current equal to 10% of the drive current generated for the high light level. Since LEDs have a linear relationship between current and optical output power, this results in a optical high power of 10 times the optical low power.

The optical power is controlled by a variable resistor (Rtset) connected between TSET and Ground (GND). The lower the value of Rtset the greater the current, for this reason the lower limit for Rtset should be  $1 \text{K}\Omega,$  which equates to a nominal peak transmit current of 100 mA. A practical maximum for Rtset is  $50 \text{K}\Omega.$  Acapella, therefore recommends that Rtset should comprise a fixed resistor of  $1 \text{K}\Omega$  in series with a logarithmic potentiometer of  $50 \text{K}\Omega,$  thus affording overload protection for the LED together with precise control of current.

$$\Gamma_{LED (High)} = 100 / Rtset$$

$$\Gamma_{LED (Low)} = 10 / Rtset$$

\* where Rtset > 1K $\Omega$ , tolerance = +/- 20%. I = Amps

#### Control of Laser Current

During the transmit cycle, the Laser drive current is controlled so as to maintain a constant optical output power from the Laser. The monitor-pin resident in the Laser converts the incident light power (from the Laser itself) to a monitor-current, which is directly compared to a preset programmed current (the current flowing through TSET). The Laser drive current is automatically adjusted to maintain the original preset light level over the recommended temperature and voltage range. The designer should be aware that whilst the control loop maintains the current generated by the monitor-pin within a tolerance of 2%, there is additional uncertainty attributed to the monitor-pin's temperature coefficient of responsivity. Data relating to the Laser characteristics should be acquired from the Laser supplier. The monitor-pin current is set by a variable resistor (Rtset), connected between TSET and Ground (GND). Acapella recommends that Rtset should comprise a logarithmic potentiometer of value 50K $\Omega$ . It is important to ensure that the Rtset resistor is inserted and adjusted to its maximum resistance value of  $50K\Omega$  prior to applying power to the ACS9010 for the first time and prior to following the procedure detailed in section headed, Laser Adjustment Procedure.

#### TxMN and TxFLG

TxMN is used to monitor the current delivered to the LED or Laser. TxMN is a current source that proportionally mirrors the current flow through the LED or Laser. By placing an appropriate resistor (Rtxmn) between TxMN and GND, the voltage developed (referenced to GND), will be proportional to the transmit current. During the Laser setup procedure TxMN should be monitored to ensure that the Laser manufacturer's maximum current specification is not exceeded (see section headed Laser Adjustment Procedure).

TxMN may also be employed during normal operation to continuously check the Laser current. The voltage developed across Rtxmn is compared within an internally generated reference voltage of 1.25V. In the event that the reference voltage is exceeded, the TxFLG is set high, otherwise it is set low.

The relationship between the transmit current and the TxMN current is:

IF Rtxmn =  $1K\Omega$ , then TxFLG = 1 when the Laser current exceeds 125mA.

#### Laser Adjustment Procedure

The output power from the Laser should be measured with a optical power meter during the setup procedure.

Select one of the Laser drive modes in accordance with section headed, *Operational Modes*. Start with the highest resistance for Rtset (at least  $50 \text{K}\Omega$  is recommended). This defines the monitor-pin reference current. Select the Laser setup mode on the ACS4050 by asserting SETB low, this forces the Laser into a continuous transmit mode and applies dc-balanced data (equal number of ones and zeros) to the Txdat input of the ACS9010 device.

As Rtset is reduced in value, the current to the Laser will increase. The current to the Laser should be monitored at the TxMN in accordance with section headed, *TxMN and TxFLAG*. The Laser current will be stable when the Laser starts to lase, and produces enough optical power for the PIN feedback current to equal the current flowing through Rtset. The Rtset impedance should be decreased until the desired Laser output high-power is achieved. Once the setup procedure has been completed, the SETB pin should then be set high to

return the device to the operation mode. The preset Laser power will then be maintained over the recommended temperature and voltage range.

#### **Receive Monitor**

The ACS9010 incorporates a power meter which generates a current source which is proportional to the received optical current.

$$\mathbf{I}_{B\times MN}^* = 6 * \mathbf{I}_{(PIN)}$$

\* Tolerance = +/- 20%.

I = Amps

$I_{RXMN}$  flows through a resistor, internal to the ACS9010, connected between RxMN and GND. The internal resistor has a value of 260K $\Omega$  +/- 20 %.

RxMN is compared with 1.25V. If RxMN exceeds 1.25V, then output RxFLG is set = 1, otherwise RxFLG is set = 0. With the internal resistor of  $260 \mathrm{K}\Omega$ , the default threshold for the RxFLG is a input current of 800nA +/- 25%. By adding an external parallel resistor between RxMN and GND, this threshold may be increased.

The voltage on RxMN will modulate with receive data bursts. It will settle to its correct value within 4us following the start of a receive burst, and will collapse to 0V after a burst ends.

#### Transmission Clock TCLK

There are two independent transmit clocks on the ACS405CS, TCLK1 and TCLK2. For the purpose of this specification, these signals will be referred to collectively as TCLK.

The ACS405CS gives a choice between internally and externally generated transmit clocks. When the CKC pin is held Low, TCLK is configured as an output producing a clock at the frequency defined by DR(4:1).

When the CKC pin is held High, TCLK is configured as an input, and will accept an externally produced transmission clock with a tolerance of up to 250ppm with respect to the transmission rate determined by DR(4:1).

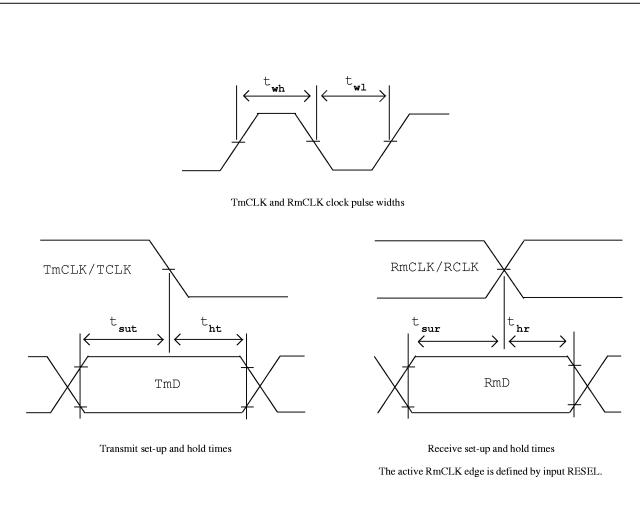

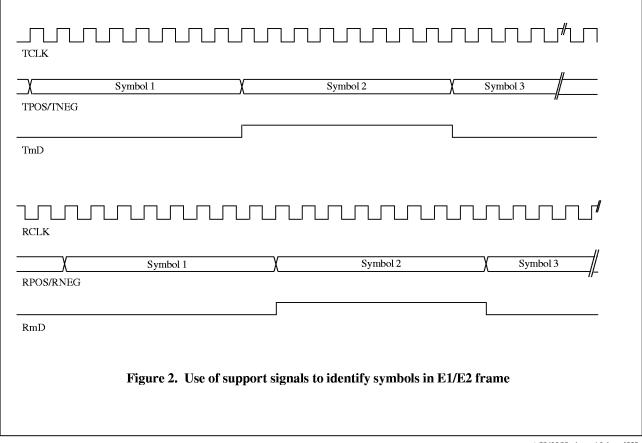

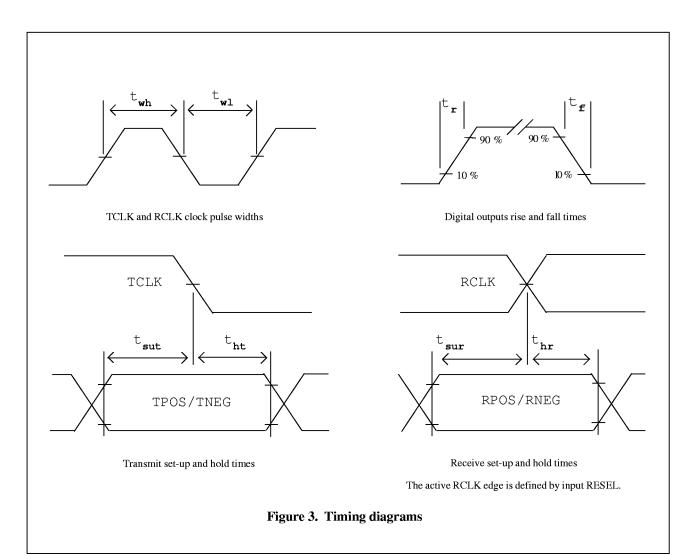

Input data appearing on the TPOS/TNEG inputs is latched into the device on the falling edge of TCLK for both internally and externally generated transmission clocks.

#### **Receive Clock RCLK**

There are two independent receive clocks on the ACS405CS, RCLK1 and RCLK2. For the purpose of this specification, these signals will be referred to collectively as RCLK.

The data appearing on RPOS/RNEG is valid on the rising or falling edge of the RCLK clock dependent on the setting of RESEL (see Figure 1. Timing diagrams). To ensure that the average receive frequency is the same as the transmitted frequency, RCLK is generated from a Digital Phase-Lock Loop (DPLL) system (except where master mode has been selected). The DPLL makes periodic corrections to the output RCLK clock by subtracting or adding a single crystal clock bit-period, so that the average frequency of the RCLK clock tracks the average frequency of the transmit clock of the far-end modem (or system master clock). This decompression/de-jittering function is covered in more detail in section headed, Jitter Characteristics.

#### **Data Coding**

The main synchronous channels may use any of the following coding methods; NRZ, AMI, HDB3, B8ZS. The desired mode is selected by POL1 and POL2 input pins, as shown in Table 2.

| Data Coding | POL2 | POL1 |         |

|-------------|------|------|---------|

| AMI         | 0    | 0    |         |

| HDB3        | 0    | 1    |         |

| B8ZS        | 1    | 0    |         |

| NRZ         | 1    | 1    |         |

|             |      |      | Table 2 |

For Non-Return-to-Zero (NRZ) coding, data is applied directly to TPOS inputs, and output data appears only on the RPOS output pins (except for 8-channel mode, see section headed, *Multi-Channel Operation*). When using NRZ code, unconnected TNEG input pins will automatically pull-up to VD+. In addition, the ACS405CS will assert a continuous Low on redundant RNEG output pins.

AMI, B8ZS and HDB3 coding is normally bipolar. However, it is possible to interface with the ACS405CS using two inputs and outputs rather than a single bipolar interface. Data equivalent to positive excursions of the bipolar AMI/B8ZS/HDB3 signal are applied as a logic High to TPOS, while data equivalent to negative excursions are applied as a logic High to TNEG. Similarly, AMI/B8ZS/HDB3 positive excursions will appear as a logic High on RPOS and negative excursions will appear as a logic High on RNEG.

It is anticipated that most users of the ACS405CS will interface directly with a E1/T1 framers. All the popular framers provide POS/NEG bipolar interfaces which will directly connect to the ACS4050.

If required, a detailed description of the AMI/HDB3 coding rules are available from Acapella.

#### **Data Rate Selection**

For the purpose of this specification TPN1 represents the set of signals TPOS1 and TNEG1, and RPN1 represents the set of signals RPOS1 and RNEG1. See section headed, *Data Coding* for a description of the coding types.

The maximum recommended crystal (XTAL) is 33.792MHz, this gives a maximum bandwidth of 8.448MHz (E2). This bandwidth can be utilised in various ways, it may be divided up over 1,2,4,8 channels. It may be required to support 2 independent clocks, in which case the available bandwidth is reduced to 4.224MHz. Single clock operation is known as mode TX1 and dual clock as TX2. There is a third mode of operation known as HT mode (High Tolerance), which is more fully described later. For the purpose of this specification these transmission modes are known collectively as the Tmodes.

The data rate selection pins DR(4:1) determine the frequency of the TCLK clock, the number of channels and the transmission mode (TMode) in accordance with the Table 3.

| DR Pins<br>4 3 2 1 | TCLK<br>freq | Nos. of channels | Tmode   |

|--------------------|--------------|------------------|---------|

| 1 1 1 1            | XTAL/4       | 1                | Tx1     |

| 1 1 1 0            | XTAL/5       | 1                | Tx1     |

| 1 1 0 1            | XTAL/16      | 2                | Tx2     |

| 1 1 0 0            | XTAL/20      | 2                | Tx2     |

| 1 0 1 1            | XTAL/16      | 1                | нт      |

| ' ' ' '            |              | 1                |         |

| 1                  | XTAL/20      | •                | HT<br>  |

| 1 0 0 1            | XTAL/16      | 4                | Tx1     |

| 1 0 0 0            | XTAL/20      | 4                | Tx1     |

|                    |              |                  |         |

| 0 1 1 1            | XTAL/32      | 4                | Tx2     |

| 0 1 1 0            | XTAL/64      | 4                | Tx2     |

| 0 1 0 1            | XTAL/32      | 8                | Tx1     |

| 0 1 0 0            | XTAL/64      | 8                | Tx2     |

|                    |              |                  |         |

| 0 0 1 1            | XTAL/128     | 8                | Tx2     |

| 0 0 1 0            | XTAL/256     | 8                | Tx2     |

| 0 0 0 1            | XTAL/250     | 1                | Tx1*    |

| 0 0 0 0            | XTAL/10      | 1                | Tx1*    |

|                    | XIAL/10      | ı                | 1.4.1   |

| * 50 km modes      |              |                  |         |

|                    |              |                  | Table 3 |

#### **Asymmetrical Data Rates**

It is possible to configure the DR pins setting on each side of the link differently (with input Fhold) as long as identical crystal values are observed on the communicating devices. For example, the near-end ACS405CS may be configured to transmit 8 channels at 1Mbps and the far-end modem may be configured

to transmit 1 channel at 8Mbps. For asymmetrical communication, set fhold = 0, this will lead to the receive circuitry reading the DR pins settings from the far-end ACS405CS rather than locally. It is important that the receive circuitry is aware of the configuration and formatting of the data so that it can correctly interpret it. Prior to lock (when DCD = 0), the receive circuitry will default to the local DR pin settings.

For symmetrical communication (with input Fhold = 1), DR pins setting sent over the link are ignored and the receive circuitry will always read the locally set DR pin values.

It is expected that for the vast majority of applications symmetrical communication will be employed. When asymmetrical mode is selected (Fhold = 0), the only valid DM settings are the Full Duplex modes. The other modes of Remote-Loop-back, Local-Loop-back, master and slave (as described in the section headed *Diagnostic modes*) are not available.

#### **Multi-Channel Operation**

There are four choices for multi-channel operation on the ACS405CS, selected by the DR(4:1) pins, namely, 1, 2, 4 or 8 channel operation.

#### **1-Channel Operation**

In 1-channel operation TPOS1/TNEG1 and RPOS1/RNEG1 is the only active channel. Data appearing on other TPN inputs is ignored. All other RPN outputs are forced low.

#### 2-Channel Operation

In 2-channel operation channel mappings can be seen in Table 4.

| Channel Nos. | Input       | Output      |

|--------------|-------------|-------------|

| 1            | TPOS1/TNEG1 | RPOS1/RNEG1 |

| 2            | TPOS2/TNEG2 | RPOS2/RNEG2 |

|              |             | Table 4     |

Data appearing on all other TPN inputs is ignored. All other RPN outputs are forced low.

#### 4-Channel Operation

In 4-channel operation the mappings can be seen in Table 5.

| Channel Nos. | Input       | Output      |

|--------------|-------------|-------------|

| 1            | TPOS1/TNEG1 | RPOS1/RNEG1 |

| 2            | TPOS2/TNEG2 | RPOS2/RNEG2 |

| 3            | TPOS3/TNEG3 | RPOS3/RNEG3 |

| 4            | TPOS4/TNEG4 | RPOS4/RNEG4 |

|              |             | Table 5     |

#### **8-Channel Operation**

If one of the 8-channel modes is selected by the DR(4:1) inputs, then the ACS405CS must be configured to expect Non-Return-to-Zero (NRZ) transmission data using the POL1/2 settings. The otherwise redundant TNEG and RNEG pins are then available to carry 4 additional data channels. The mapping of transmission pins for 8-channel NRZ operation can be seen in Table 6.

| Channel Nos. | Input | Output |

|--------------|-------|--------|

| 1            | TPOS1 | RPOS1  |

| 2            | TNEG1 | RNEG1  |

| 3            | TPOS2 | RPOS2  |

| 4            | TNEG2 | RNEG2  |

| 5            | TPOS3 | RPOS3  |

| 6            | TNEG3 | RNEG3  |

| 7            | TPOS4 | RPOS4  |

| 8            | TNEG4 | RNEG4  |

|              | Т     | able 6 |

#### Transmission Modes (TMode)

There are three transmission modes available on the ACS405CS selected by the DR(4:1) pins, these are TX1, TX2 and HT modes.

#### TX1 mode

In TX1 mode all of the data channels (TPN/RPN) are related to the clocks TCLK1/RCLK1.

#### TX2 mode

In TX2 mode there are two system clocks, half the signals are aligned to the clock TCLK1/RCLK1 and the remaining half are aligned to the clock TCLK2/RCLK2.

For dual channel operation, channel 1 is aligned to clock TCLK1/RCLK1 and channel 2 is aligned to clock TCLK2/RCLK2.

For four channel operation, channels 1-2 are aligned to clock TCLK1/RCLK1 and channels 3-4 are aligned to clock TCLK2/RCLK2.

For eight channel operation, channels 1-4 are aligned to clock TCLK1/RCLK1 and channels 5-8 are aligned to clock TCLK2/RCLK2.

#### HT mode

Acapella recognises that a large number of designers using the ACS405CS modem will be employing the device for single channel T1 or single channel E1 operation. In such cases, the available bandwidth far exceeds the bandwidth required. To

exploit this otherwise redundant bandwidth, the ACS405CS incorporates a High Tolerant (HT) transmission mode. In HT mode, by virtue of onchip error-correction, the device is extremely tolerant to data errors.

All modes in the ACS405CS generate regular unique Synchronisation Words (SWs) in order to re-enforce 8B10B word boundary synchronisation. This prevents single bit-errors causing an avalanche of errors due to word boundary slippage, often referred to as "error extension". In HT mode, SWs are interleaved with the data-words such that alternate words are SWs, ensuring that the effect of 8B10B word boundary errors will not propagate beyond one received data word.

In HT mode the single data channel is aligned to the TCLK1/RCLK1 clock.

#### 50km long haul mode

Some customers will require a modem capable of supporting a longer distance than the standard 25km. To support this Acapella have implemented a 50km mode for a single E1 or T1 channel. This is achieved with an XTAL of value half of that used for the standard E1 or T1 for 25km modes in combination with the appropriate configuration of the DR(4:1) pins.

NOTE: The designer should be aware that the use of lower value crystal will proportionally increase the end-to-end data delay through the system in accordance with the formula found in section headed, *Data Delay (Latency)*. Therefore, for the 50km mode the latency will double compared to the standard 25km modes.

#### **Example Data Rate Selection**

A set of example configurations follow:

#### E2 Selection

In order to select one E2 operation then set DR4 = DR3 = DR2 = DR1 = 1, together with a crystal of 33.792MHz as shown in the Table 7.

| DR4                  | DR3 | DR2 | DR1 | XTAL<br>Divide | TCLK<br>(MHz) |

|----------------------|-----|-----|-----|----------------|---------------|

| 1                    | 1   | 1   | 1   | 4              | 8.448         |

| crystal = 33.792 MHz |     |     |     |                | Table 7       |

#### **T2** Selection

In order to select one T2 channel then set DR4 = DR3 = DR2 = 1; DR1 = 0, together with a crystal of 31.560MHz as shown in the Table 8.

| DR4                  | DR3 | DR2 | DR1 | XTAL<br>Divide | TCLK<br>(MHz) |

|----------------------|-----|-----|-----|----------------|---------------|

| 1                    | 1   | 1   | 0   | 5              | 6.312         |

| crystal = 31.560 MHz |     |     |     |                | Table 8       |

# DR4 DR3 DR2 DR1 XTAL Divide TCLK (MHz) 0 0 0 1 8 2.048 crystal = 16.384 MHz Table 12

#### 2 \* E1 Channel Selection

In order to select two independent E1 channels in TX2 mode then set DR4 = DR3 = DR1 = 1; DR2 = 0, together with a crystal of 32.768MHz as shown in the Table 9.

| DR4  | DR3      | DR2     | DR1 | XTAL<br>Divide | TCLK<br>(MHz) |

|------|----------|---------|-----|----------------|---------------|

| 1    | 1        | 0       | 1   | 16             | 2.048         |

| crys | tal = 32 | .768 MF |     | Table 9        |               |

#### 2 \* T1 Channel Selection

In order to select two independent E1 channels in TX2 mode then set DR4 = DR3 = 1; DR1 = DR2 = 0, together with a crystal of 30.88MHz as shown in the Table 10.

| DR | 4 DR3     | DR2     | DR1 | XTAL<br>Divide | TCLK<br>(MHz) |

|----|-----------|---------|-----|----------------|---------------|

| 1  | 1         | 0       | 0   | 20             | 1.544         |

| СІ | ystal = 3 | 0.88 MH |     | Table 10       |               |

#### 1 \* E1 Channel Selection HT mode

In order to select one E1 channel operating in High Tolerance (HT) mode then set DR4 = DR2 = DR1 = 1; DR3 = 0, together with a crystal of 32.768MHz as shown in the Table 11.

| DR4                  | DR3 | DR2 | DR1 | XTAL<br>Divide | TCLK<br>(MHz) |

|----------------------|-----|-----|-----|----------------|---------------|

| 1                    | 0   | 1   | 1   | 16             | 2.048         |

| crystal = 32.768 MHz |     |     |     |                | Table 11      |

#### 1 \* E1 Channel Selection at 50km

In order to double the available transmission distance from 25km to 50km, the value of the crystal must be reduced by half. For a single E1 channel set DR4 = DR3 = DR2 = 0; DR1 = 1, together with a crystal of 16.384MHz as shown in Table 12.

#### 1 \* T1 Channel Selection in HT mode

In order to set the device for one T1 channels operating in High Tolerance Mode (HT) then DR4 = DR2 = 1; DR3 = DR = 0, together with a crystal of 30.88MHz as shown in the Table 13.

| DR4                 | DR3 | DR2 | DR1 | XTAL<br>Divide | TCLK<br>(MHz) |

|---------------------|-----|-----|-----|----------------|---------------|

| 1                   | 0   | 1   | 0   | 20             | 1.544         |

| crystal = 30.88 MHz |     |     |     | T              | able 13       |

#### 1 \* T1 Channel Selection at 50km

In order to double the available transmission distance from 25km to 50km, the value of the crystal must be reduced by half. For a single T1 channel set DR4 = DR3 = DR2 = DR1 = 0, together with a crystal of 15.44MHz as shown in Table 14.

| DR4  | DR3       | DR2     | DR1 | XTAL<br>Divide | TCLK<br>(MHz) |

|------|-----------|---------|-----|----------------|---------------|

| 0    | 0         | 0       | 0   | 10             | 1.544         |

| crys | stal = 15 | .44 MHz | Ta  | ible 14        |               |

#### 4 \* E1 Channel Selection

In order to set the device for four E1 channels then DR4 = DR1 = 1; DR3 = DR2 = 0, together with a crystal of 32.768MHz as shown in the Table 15.

| DR4 | DR3       | DR2      | DR1 | XTAL<br>Divide | TCLK<br>(MHz) |

|-----|-----------|----------|-----|----------------|---------------|

| 1   | 0         | 0        | 1   | 16             | 2.048         |

| cry | stal = 32 | 2.768 MI | Та  | ible 15        |               |

#### 4 \* T1 Channel Selection

In order to set the device for four T1 channels then DR3 = DR2 = DR1 = 0; DR4 = 1, together with a crystal of 30.88MHz a shown in the Table 16.

| DR4  | DR3      | DR2     | DR1 | XTAL<br>Divide | TCLK<br>(MHz) |

|------|----------|---------|-----|----------------|---------------|

| 1    | 0        | 0       | 0   | 20             | 1.544         |

| crys | tal = 30 | .88 MHz | Та  | ble 16         |               |

#### **Other Transmission Data Rates**

Other standard frequencies may be obtained by setting the appropriate DR(4:1) combination with a 32.768MHz crystal as shown in the Table 17.

| DR4   | DR3       | DR2    | DR1 | Nos. of<br>Chann. | XTAL<br>Divide | TCLK<br>(KHz) |

|-------|-----------|--------|-----|-------------------|----------------|---------------|

| 0     | 1         | 1      | 1   | 4                 | 32             | 1024          |

| 0     | 1         | 1      | 0   | 4                 | 64             | 512           |

| 0     | 1         | 0      | 1   | 8                 | 32             | 1024          |

| 0     | 1         | 0      | 0   | 8                 | 64             | 512           |

| 0     | 0         | 1      | 1   | 8                 | 128            | 256           |

| 0     | 0         | 1      | 0   | 8                 | 256            | 128           |

| cryst | ial = 32. | 768 MH | lz  |                   | Table          | 17            |

#### **Asynchronous Communication**

In order to propagate asynchronous data through the ACS405CS, the device should be configured with CKC = 0 so that the device produces a TCLK output clock. The TCLK clock asynchronously oversamples the data applied to TPOS at the rate defined by DR(4:1). The choice of TCLK frequency defines the sample rate of the input data and therefore the sampling-jitter appearing at RPOS of the far-end modem.

#### **Example:**

| 8 - asynchronous 115kbps channels. |   |                                   |

|------------------------------------|---|-----------------------------------|

| XTAL                               | _ | 32.768MHz                         |

| DR4/3/2/1                          | = | 0/1/0/1                           |

| CKC                                | = | 0                                 |

| TCLK clock                         | = | 1.024MHz                          |

| TPOS/TNEG data rate                | = | 115kbps                           |

| Over-sample factor                 | = | 8.9                               |

| Sampling Jitter (approx.')         | = | 11%.                              |

| Ot 11 1 11 11 11                   |   | The second of the first second of |

Similar considerations apply to the maintenance channel, which may also be used to convey asynchronous data.

#### **Support channels**

There are up to two support channels on the ACS405CS:

TmD1/RmD1 and TmD2/RmD2. For the purpose of this specification these will be referred to collectively as TmD and RmD.

The support channels can be used in one of two ways selected by the input Frame.

#### Maintenance channel mode with Frame = 0

When Frame = 0 then maintenance mode is selected. This provides one maintenance channel TmD1/RmD1. TmD2/RmD2 is not available for data transmission.

TmD1/RmD1 may be considered as an independent maintenance channel that supports data rates of 64kbps or 32kbps depending on the setting of the DR(4:1) pins. See Table 18.

Input data appearing on the TmD1 input is latched into the device on the falling edge of TmCLK and appears at the RmD1 output of the far-end modem on the rising edge of RmCLK.

The ACS405CS gives a choice between internally and externally generated TmCLK clocks. When the CKM pin is held Low, TmCLK is configured as an output producing a clock at 64kHz or 32kHz. When the CKM pin is held High, TmCLK is configured as an input, and will accept an externally produced transmission clock at 64kHz or 32kHz with a tolerance of 500ppm.

The TmD1/RmD1 is an independent channel and consequently there is not a fixed phase relationship between the maintenance channel and the main TPOS/TNEG data transmission channels.

| DR4 | DR3 | DR2 | DR1 | XTAL   | XTAL    | TmCLK    |

|-----|-----|-----|-----|--------|---------|----------|

|     |     |     |     | (MHz)  | DC      | (KHz)    |

|     |     |     |     |        |         |          |

| 1   | 1   | 1   | 1   | 33.792 | 528     | 64       |

| 1   | 1   | 1   | 0   | 31.560 | 493.125 | 64       |

| 1   | 1   | 0   | 1   | 32.768 | 512     | 64       |

| 1   | 1   | 0   | 0   | 30.88  | 482.5   | 64       |

| 1   | 0   | 1   | 1   | 32.768 | 512     | 64       |

| 1   | 0   | 1   | 0   | 30.88  | 482.5   | 64       |

| 1   | 0   | 0   | 1   | 32.768 | 512     | 64       |

| 1   | 0   | 0   | 0   | 30.88  | 482.5   | 64       |

|     |     |     |     |        |         |          |

| 0   | 1   | 1   | 1   | 32.768 | 512     | 64       |

| 0   | 1   | 1   | 0   | 32.768 | 512     | 64       |

| 0   | 1   | 0   | 1   | 32.768 | 512     | 64       |

| 0   | 1   | 0   | 0   | 32.768 | 512     | 64       |

| 0   | 0   | 1   | 1   | 32.768 | 512     | 64       |

| 0   | 0   | 1   | 0   | 32.768 | 512     | 64       |

| 0   | 0   | 0   | 1   | 16.384 | 512     | 32       |

| 0   | 0   | 0   | 0   | 15.440 | 482.5   | 32       |

|     |     |     |     |        |         |          |

|     |     |     |     |        |         | Table 18 |

Each DR(4:1) mode is designed to achieve a particular communication frequency by the combination of the XTAL value and DC value. Table 18 shows the recommended XTAL and the Divide Constant (DC) for each DR(4:1) selection. If the recommended XTALs are not employed, then the frequency of the TmCLK clock can be calculated from the Divide Constant.

#### Frame channel mode with Frame = 1

When Frame = 1 the channels TmD/RmD become support channels to the main TPOS/TNEG data channels and are associated with the TCLK and RCLK clock rather than the TmCLK and RmCLK clocks employed in maintenance mode.

Frame mode is only available for a subset of the possible DR(4:1) settings; these are shown in Table 19. Where Table 19 denotes the number of Frame channels available as zero, then the status of the Frame input pin will be ignored and the support channels will function in maintenance mode.

| R | D<br>R<br>3 | R | R | XTAL<br>(MHz) |       | Nos. of Frame<br>Mode channels<br>available |

|---|-------------|---|---|---------------|-------|---------------------------------------------|

| 1 | 1           | 1 | 1 | 33.792        | 2/512 | 1                                           |

| 1 | 1           | 1 | 0 | 31.560        | 2/512 | 1                                           |

| 1 | 1           | 0 | 1 | 32.768        | 2/128 | 2                                           |

| 1 | 1           | 0 | 0 | 30.88         | 2/128 | 2                                           |

| 1 | 0           | 1 | 1 | 32.768        | 2/128 | 1                                           |

| 1 | 0           | 1 | 0 | 30.88         | 2/128 | 1                                           |

| 1 | 0           | 0 | 1 | 32.768        | 0     | 0                                           |

| 1 | 0           | 0 | 0 | 30.88         | 0     | 0                                           |

| 0 | 1           | 1 | 1 | 32.768        | 0     | 0                                           |

| 0 | 1           | 1 | 0 | 32.768        | 0     | 0                                           |

| 0 | 1           | 0 | 1 | 32.768        | 0     | 0                                           |

| 0 | 1           | 0 | 0 | 32.768        | 0     | 0                                           |

| 0 | 0           | 1 | 1 | 32.768        | 0     | 0                                           |

| 0 | 0           | 1 | 0 | 32.768        | 0     | 0                                           |

| 0 | 0           | 0 | 1 | 16.384        | 2/512 | 1                                           |

| 0 | 0           | 0 | 0 | 15.440        | 2/512 | 1                                           |

|   |             |   |   |               |       | Table 19                                    |

Data appearing on inputs TmD1/2 are latched into the device on the falling edge of TCLK for both internally and externally generated transmission clocks. Output data appearing on RmD1/2 is valid on the rising or falling edge of the RCLK clock depending on the setting of RESEL (see Figure 1. Timing diagrams).

For 1-channel operation in either TX1 or HT mode then TmD1/RmD1 will be available for transmission but data appearing on TmD2 will be ignored.

For 2-channel operation in TX2 mode then both TmD1/RmD1 and TmD2/RmD2 are available for transmission. TmD1 is associated with channel 1 and is clocked by TCLK1/RCLK1. TmD2 is associated with channel 2 and is clocked by TCLK2/RCLK2.

For all other data formats, frame mode is currently unavailable.

Although, the data applied to the TmD1/2 is clocked by TCLK with the same resolution as TCLK the number of transitions allowed on these inputs is restricted according to the following rules:

#### TX1 mode

A maximum of 2 transitions are permitted on TmD1 for each 512 TCLK1 clock period. If two transitions occur sequentially (on two successive TCLK cycles) then this may be counted as one transition.

#### TX2 mode

A maximum of 2 transitions may occur on both TmD1/2 for each 128 TCLK1/2 clock period. If two transitions occur sequentially (on two successive TCLK1/2 cycles) then this may be counted as one transition.

#### HT mode

A maximum of 2 transitions may occur on TmD1 for each 128 TCLK1 clock period. If two transitions occur sequentially (on two successive TCLK1 cycles) then this may be counted as one transition.

In frame mode, TPOS/TNEG and the associated TmD data are transmitted over the link in phase and will appear in phase at the RPOS/RNEG and RmD outputs at the far-end ACS405CS.

A typical application of frame mode follows:

In an E1 frame, only 30 of the available 32 symbols are available for data transmission, the remaining two symbols are deployed for frame synchronisation and signalling. In a proprietary system, it would be possible to use the TmD1/2 support channels to mark the first bit or first word of each frame, thus freeing up extra bandwidth in the main data channels.

#### Diagnostic Modes

The ACS405CS has eight diagnostic modes controlled by DM(3:1) as shown in Table 20. The diagnostic modes apply equally to the TPN/RPN and TmD/RmD channels.

| Diagnostic Mode               | Lock            | DM3 | DM2 | DM1    |

|-------------------------------|-----------------|-----|-----|--------|

| Full-duplex<br>Full-duplex    | Drift<br>Memory | 0   | 0   | 0      |

| Remote loopback               | Random          | 0   | 1   | Ó      |

| Full-duplex<br>Local loopback | Random<br>Drift | 0   | 1   | 1<br>0 |

| Full-duplex slave             | Active          | 1   | 0   | 1      |

| Full-duplex master            | Drift           | 1   | 1   | 0      |

| Full-duplex                   | Active          | 1   | 1   | 1      |

|                               |                 |     | Tab | le 20  |

#### Full-Duplex

In the full-duplex configuration, the RCLK clock of both devices track the average frequency of the corresponding TCLK clock of the opposite end of the link. The receiving Digital-Phase-Lock Loop (DPLL) system makes periodic adjustments to the RCLK clock to ensure that the average frequency is exactly the same as the far-end TCLK clock. In summary, each TCLK is an independent master clock and each RCLK a slave of the far-end TCLK clock.

The relationship between TmCLK and RmCLK are treated similarly.

#### **Full-Duplex Slave**

In slave mode, the TCLK and RCLK clock is derived from the TCLK clock of the far-end modem, such that their average frequencies are identical. Clearly, it is essential that only one modem within a communicating pair is configured in slave mode. The CKC pin should be forced to GND, so that TCLK is always configured as an output. Since only one device in the modem pair may be configured in slave mode, the mode also selects active lock. See section headed, *Locking Modes*.

The relationship between TmCLK and RmCLK are treated similarly. The CKM pin should be forced to GND, so that TmCLK is always configured as an output.

#### **Full-Duplex Master**

In master mode, the local RCLK clock is internally generated from the local TCLK clock. The local TCLK clock may be internally or externally generated. Master mode is only valid if the far-end device is configured in slave mode or if the far-end TCLK clock is derived from the far-end RCLK clock. Only one modem within a communicating pair may be configured as a master.

The relationship between TmCLK and RmCLK are treated similarly.

#### Local Loopback

In local loopback mode, TPN and TmD data is looped back inside the near-end modem and is output at its own RPN and RmD outputs.

Data received from the far-end device is ignored, except to maintain lock. If concurrent requests occur for local and remote loopback, local loopback is selected.

The local loopback diagnostic mode is used to test data flow up to, and back from, the local ACS405CS and does not test the integrity of the link itself. Therefore, local loopback operates independently of synchronisation with a second modem (i.e. DCD may be High or Low).

#### Remote Loopback

In remote loopback mode, the near-end modem sends a request to the far-end modem to loopback its received data, thus returning the data so that it appears at the RPN and RmD of the initiating modem.

Both modems are exercised completely, as well as the Lasers/LEDs and the fiber optic link. The remote loopback test is normally used to check the integrity of the entire link from the near-end (initiating modem).

Whilst a device is responding to a request for remote loopback from the far-end, requests from the near-end to initiate remote loopback will be ignored.

#### Drift Lock

Communicating modems attain a stable state when the "transmit window" of one modem coincides with the "receive window" of the other, allowing for delay through the optical link. Adjustments to machine cycles are made automatically during operation, to compensate for differences in XTAL frequencies which would otherwise cause loss of synchronisation.

When both modems are configured in drift lock, synchronisation described above depends on a difference in the XTAL or system clock frequencies at each end of the link, and the greater the difference the faster the locking. Therefore, if the difference between XTAL frequencies is very small (a few ppm), automatic locking may take tens of seconds or even minutes. For this reason, normally only one modem in the communication pair will be configured in drift lock mode.

Drift lock will not succeed if the two modems are driven by an external XTAL clock derived from a single source (i.e. tolerance of 0 ppm).

#### **Active Lock Mode**

Active lock mode may be used to accelerate synchronisation of a pair of communicating modems so that they achieve lock in less than 1 second. Active lock reduces the machine cycle of the device by 0.5% ensuring that the receive window moves swiftly through the transmit window of the opposing modem. To effect active lock, one modem should be permanently configured in drift lock and the other in active lock. If this is not possible because the system mandates that all modems are peers ( configured identically ), then the same effect may be realised by temporarily invoking lock for a short time after power-up. This is achieved as follows: connect pins DM1, DM2 and DM3 together attaching the node to an RC arrangement, with the capacitor to VDD and the resistor to GND, to create a 5 V to 0 V ramp on power-up. The RC time-constant should be Ca. 5 seconds.

Active lock will succeed even when communicating devices are driven from clocks derived from a single source (0 ppm).

#### Random Lock

This mode achieves moderate locking times (typically 2 seconds, worst case 3 seconds) with the advantage that the ACS405CS's are configured as peers. Communicating modems may be permanently configured in this mode (i.e. with hard-wired pins).

Random lock will succeed even when communicating devices are driven from clocks derived from a single source (0 ppm). Random lock mode is compatible with drift lock and active lock.

#### Memory Lock

Following the assertion of a reset (PORB = 0) communicating devices will initiate an arbitration process where within 2 seconds (typically) the communicating modems will achieve synchronisation, one establishing itself as an active-lock modem and the other establishing itself as a drift-lock modem. On subsequent attempts to lock, synchronisation will be achieved within 1 second. It is only necessary to apply PORB to one device in the communicating pair to initiate an arbitration process.

Since memory lock status (Active or Drift) uses onchip storage, loss of power to the IC will require a new reset (PORB = 0). Furthermore, should there be a need to synchronise with a third modem, a new reset will be required.

#### **Mixing Lock Modes**

It is possible to mix all combinations of locking modes once the modems are locked, however, prior to synchronisation two modems configured in active lock will not operate. The effect of mixing locking modes on locking speed can be seen in Table 21.

| Device A<br>Mode | Device B<br>Mode | Locking Speed |

|------------------|------------------|---------------|

|                  |                  |               |

| Drift            | Drift            | Drift         |

| Drift            | Active           | Active        |

| Drift            | Random           | Random        |

| Drift            | Memory           | Random        |

| Active           | Active           | Not allowed   |

| Active           | Random           | Random        |

| Active           | Memory           | Random        |

| Random           | Random           | Random        |

| Random           | Memory           | Random        |

| Memory           | Memory           | Active*       |

\* Memory lock has random lock speed for the first synchronisation (arbitration).

Table 21

#### **ERRC and ERRL - Error Detection**

These signals can be used to give an indication of the quality of the optical link. Even when a DC signal is applied to the data, maintenance and TCLK inputs, the ACS405CS modem transmits approximately 11Mbps over the link in each direction. This control data is used to maintain the timing and the relative positioning of transmit and receive windows.

The transmit and control data is constantly monitored to make sure it is compatible with the 8B10B format. If a coding error is detected ERRL will go High and will remain High until reset. ERRL may be reset by asserting PORB, or by removing the fiber optic cable from one side of the link thereby forcing the device temporarily out of lock.

ERRC produces a pulse on detection of each coding error. These pulses may be accumulated by means of an external electronic counter.

Please note that ERRL and ERRC detect coding errors and not data errors, nevertheless because of the complexity of the coding rules employed on the ACS405CS, the absence of detected errors on these pins will give a good indication of a high quality link.

#### Laser/LED Considerations

Since LEDs or Lasers from different suppliers may emit different wavelengths, it is recommended that the Lasers/LEDs in a communicating pair of modems are obtained from the same supplier. Acapella can supply details.

#### **Power Supply Decoupling**

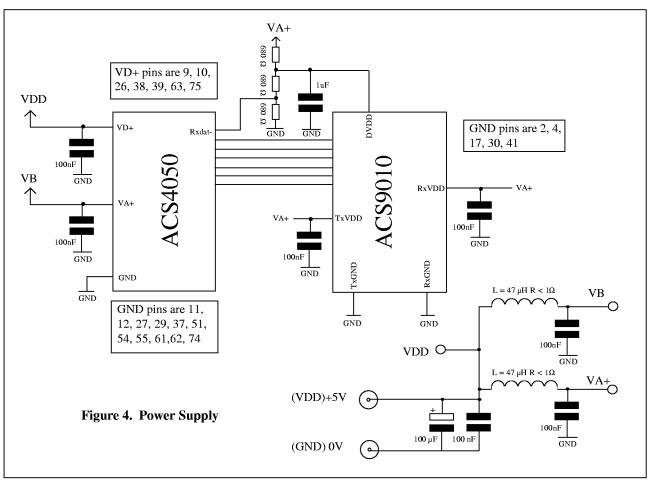

The ACS9010 contains a highly sensitive amplifier, capable of responding to extremely low current levels. To exploit this sensitivity it is important to reduce external noise to a low level compared to the input signal from the Laser/LED. The modem should have an independent power trace to the point where power enters the board.

Figure 4, shows the recommended power supply decoupling. The Laser/LED should be sited very close to the PMN, PINP, PINN, LAN and LAP pins. A generous ground plane should be provided, especially surrounding the sensitive PINP and PINN tracks from the ACS9010 pins to the optical component. The modem should be protected from EMI/RFI sources in the standard ways.

#### Link Budgets

The link budget is the difference between the power coupled to the fiber via the transmit Laser/LED and the power required to realise the minimum inputamplifier current via the receive PIN/LED. The link budget is normally specified in dB, and represents the maximum attenuation allowed between communicating Lasers/LEDs. The budget is utilised in terms of the cable length, cable connectors and splices. It usually includes an operating margin to allow for degradation in LASER/LED performance.

The power coupled to the cable is a function of the efficiency of the Laser/LED, the current applied to the Laser/LED and the type of the fiber optic cable employed.

#### **Digital Mode**

The ACS4050 may be used without the ACS9010 device with custom external circuitry for non-fiber applications. Please check with Acapella for details.

#### LOSS (Loss Of Synchronisation)

There are two conditions that will make LOSS go to logic 1:

- i) Loss of synchronisation ping-pong windows incorrectly aligned i.e DCD = 0.

- ii) 64 received symbols break the 8B10B encoding rules in a sequence of 256 symbols.

In order to return LOSS to the logic state 0 the following criteria must be met.

- i) The devices must be synchronised ping-pong windows correctly aligned i.e DCD = 1.

- ii) There are no received symbols in a sequence of 256 symbols which break the 8B10B coding rules.

#### Data Delay (Latency)

Although the ACS405CS is a full-duplex modem, at the fiber level the device operates in a half-duplex manner. Typically, half-duplex systems allow bidirectional transmission by alternating the direction of data flow. This means that data must be stored until the link is configured in the appropriate direction. Storage inevitably leads to delay or latency. Acapella has designed the ACS405CS to minimise latency by very rapidly switching direction at the fiber level, minimising the need to store data.

The latency through the system applies to the main data TPOS/TNEG channels and the support channels TmD/RmD and is a function of the XTAL frequency. For a given implementation, the latency has three components:

- 1) A Constant Delay (CD) set by the machine cycle and system clock at a frequency of 32.768MHz then CD = 0.7ms.

- 2) A Transmission Rate Delay (TRD) which is equal to 125 bit periods worst case (de-jittering buffer and internal registers)

- 3) Fiber length Dependent Delay (FDD) which is equal to 2 \* (fiber delay)

The Latency formula is:

$(0.7 * 10^{-3} * 32.768 * 10^{-6}/XTAL) + (125 * transmit bit period) + (2 * fiber delay), Where the fiber delay is typically 5us per km.$

#### **Example Latency calculation**

Latency calculation:

```

Fiber length = 10km (~50us)

XTAL = 33.792MHz

```

DR mode = 4 \* 2.048Mbps (transmit bit period = 488ns)

Latency =  $((0.7 * 10^{-3} * 32.768 * 10^{-6}/33.792 * 10^{-6}) + (125 * 488 * 10^{-9}) + (2* 50 * 10^{-6})) = 0.84 ms$

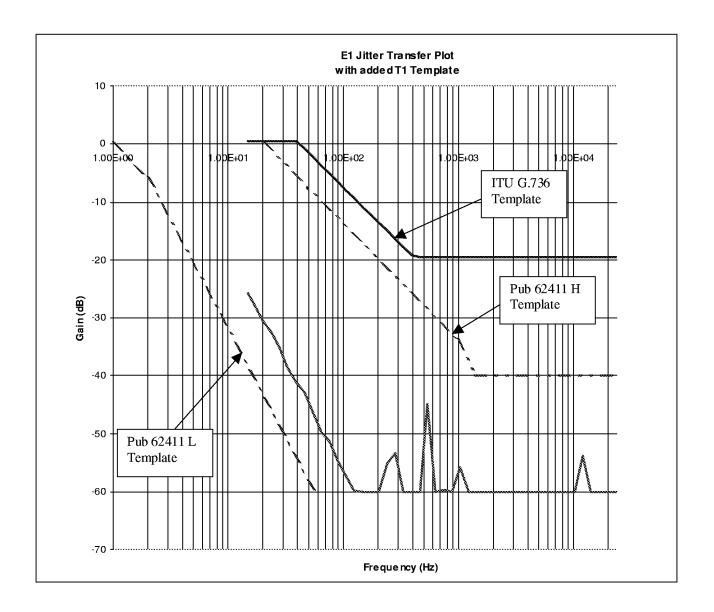

#### **Jitter Characteristics**

The transmit path contains a Transmit FIFO, which acts to attenuate high frequency input jitter components of the order 1kHz or greater.

The receive path contains a Digital Phase Locked Loop (D\_PLL), which controls the output frequency of the receive clock in order to track the transmit clock frequency at the far end modem. The D\_PLL also acts to:-

- 1) maintain the fill level in the receive FIFO, to ensure that the data latency stays within the specified limits.

- 2) ensure that Jitter Tolerance and Jitter Attenuation is within ITU G.823 and AT&T 62411 specifications.

- 3) accommodate any clock drift that may be present.

The performance boundary of the D\_PLL is ±500 ppm. The ±500 ppm performance limit includes jitter attenuation and drift accommodation.

The oscillator controlled by the Digital Phase Locked Loop operates in steps of 8ppm, and therefore has a resolution down to +/- 4ppm. Due to the discrete nature of the frequency changes, the period of the receive clock can change by +/- one system clock cycle. In the absence of input jitter, output jitter generation for E1 remote loopback configuration is measured at 0.40Ulpp over frequency range 20Hz to 100kHz, and 0.08Ulpp over frequency range 18kHz to 100kHz.

The E1 Jitter Transfer plot is shown below, measured worst case, Remote Loopback.

Figure 1. Timing diagrams

Pin Description ACS4050 part 1

| Pin                                             | ription ACS<br>Sym               | Ю | Name                    | Description                                                                                                                                                                                                                             |

|-------------------------------------------------|----------------------------------|---|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9,10<br>26,38<br>39,63<br>75                    | VD+                              | - | +ve power supply        | Power supply, 4.75 - 5.25<br>Volts.                                                                                                                                                                                                     |

| 49                                              | VA+                              | 1 | +ve power supply        | Power supply for Clock<br>Recovery PLL, 4.75 - 5.25<br>Volts.                                                                                                                                                                           |

| 11,12<br>27,29<br>37,51<br>54,55<br>61,62<br>74 | GND                              | ı | Ground                  | Power Supply                                                                                                                                                                                                                            |

| 19<br>21<br>23<br>25                            | TPOS1<br>TPOS2<br>TPOS3<br>TPOS4 | I | Transmit Data<br>Pos    | Transmit channel 1, corresponds to +ve in bipolar signal. Transmit channel 2, corresponds to +ve in bipolar signal. Transmit channel 3, corresponds to +ve in bipolar signal. Transmit channel 4, corresponds to +ve in bipolar signal. |

| 18<br>20<br>22<br>24                            | TNEG1<br>TNEG2<br>TNEG3<br>TNEG4 | I | Transmit Data<br>Neg    | Transmit channel 1, corresponds to -ve in bipolar signal. Transmit channel 2, corresponds to -ve in bipolar signal. Transmit channel 3, corresponds to -ve in bipolar signal. Transmit channel 4, corresponds to -ve in bipolar signal. |

| 2<br>4<br>6<br>8                                | RPOS1<br>RPOS2<br>RPOS3<br>RPOS4 | 0 | Receive Data<br>Pos     | Receive channel 1, corresponds to +ve in bipolar signal. Receive channel 2, corresponds to +ve in bipolar signal. Receive channel 3, corresponds to +ve in bipolar signal. Receive channel 4, corresponds to +ve in bipolar signal.     |

| 1<br>3<br>5<br>7                                | RNEG1<br>RNEG2<br>RNEG3<br>RNEG4 | 0 | Receive Data<br>Neg     | Receive channel 1, corresponds to -ve in bipolar signal. Receive channel 2, corresponds to -ve in bipolar signal. Receive channel 3, corresponds to -ve in bipolar signal. Receive channel 4, corresponds to -ve in bipolar signal.     |

| 40                                              | RESEL                            | I | Receive Edge<br>Select  | When RESEL = 1,<br>RPOS/RNEG and RmD data is<br>valid on the rising edge of<br>RCLK/RmCLK. When RESEL<br>= 0, the data is valid on the<br>falling edge of RCLK/RmCLK.                                                                   |

| 48<br>47                                        | XTI/<br>XTO                      | - | System Clock<br>Crystal | Connect fundamental parallel resonance crystal with appropriate padding capacitor to GND.                                                                                                                                               |

| 64                                              | DCD                              | 0 | Data Carrier<br>Detect  | When DCD = 1, then the communicating modems have synchronized, and are communicating.                                                                                                                                                   |

| 66                                              | PORB                             | I | Power On<br>Reset       | Will initialise the device when PORB= 0. PORB is normally connected to an RC circuit so that a POR is automatically invoked on power-up. PORB= 1 for normal operation.                                                                  |

Pin Description ACS4050 part 2

| Pin      | Sym            | Ю   | Name                                  | Description                                                                                                                                                                              |

|----------|----------------|-----|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13       | TmCLK          | I/O | Transmit<br>maintenance<br>CLK        | Transmit maintenance clock. Samples TmD on falling edge when device is not in valid frame mode. See input 'FRAME'.                                                                       |

| 15<br>14 | TCLK1<br>TCLK2 | Ι/O | Transmit clocks                       | Transmit Clock 1/2, samples TPOS/TNEG data on falling edge.                                                                                                                              |

| 76       | RmCLK          | 0   | Receive Clock<br>(support<br>channel) | Support channel receive clock<br>With frame = '0' then nominal<br>frequency = 64 KHz                                                                                                     |

| 78<br>77 | RCLK1<br>RCLK2 | 0   | Receive clocks                        | Receive Clock, RPOS/RNEG data is valid on edge selected by input "RESEL".                                                                                                                |

| 16<br>17 | TmD1<br>TmD2   | I   | Transmit<br>maintenance<br>Data       | NRZ maintenance channel. TmD is sampled on falling edge of TmCLK clock when frame mode is valid else data is sampled on falling edge of TCLK.                                            |

| 80<br>79 | RmD1<br>RmD2   | 0   | Receive<br>maintenance<br>Data        | NRZ maintenance channel. Data is set-up with repect to RCLK clock when frame mode is valid else data is set-up with respect to RmCLK. Data is valid on the clock edge selected by RESEL. |

| 35       | CKC            | Ι   | Clock Select                          | When CKC = 0, TCLK1/2 is configured as an output. When CKC = 1, TCLK1/2 is configured as an input                                                                                        |

| 36       | СКМ            | I   | Clock Select                          | When CKM = 0, TmCLK1/2 is configured as an output. When CKM = 1, TmCLK1/2 is configured as an input                                                                                      |

| 30       | ECLK           | I   | External Clock                        | External system clock input. Only valid when SCEXT = '1'. Clock must have at least 40% High and 40% Low time.                                                                            |

| 57       | SCEXT          | I   | Select Clock<br>External              | When SCEXT = '1', then the system clock will be the external clock applied to input 'ECLK'. When SCEXT = '0', then the system clock will be the crystal clock generated at XTI/XTO.      |

| 43       | Frame          | I   | Frame Mode                            | When Frame = '1', Support channels are configured in frame mode.                                                                                                                         |

Pin Description ACS4050 part 3

| Pin                  | Sym                      | Ю | Name                | Description                                                                                                                                                                                                       |

|----------------------|--------------------------|---|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41                   | Fhold                    | I | Format Hold         | When Fhold = '0', the device is configured for asymmetrical data communication. The most common setting for this input is Fhold = '1' supporting symmetrical communications.                                      |

| 42                   | SETB                     | Ι | LASER set-up        | SETB = 0, to adjust the<br>LASER output power.<br>SETB = 1, in operational mode.                                                                                                                                  |

| 46<br>45<br>44       | DM1<br>DM2<br>DM3        | I | Diagnostic<br>Modes | DM(3:1) input select the<br>Diagnostic Modes such as<br>local-loopback and remote-<br>loopback.                                                                                                                   |

| 50                   | IREF                     | I | Current reference   | A 51KΩ 1% resistor should be placed between IREF and GND.                                                                                                                                                         |

| 53                   | Rxdat-                   | Ι | Rxdat -ve<br>input  | This determines the slicing level for input Rxdat+. Should be set at DVDD / 2. On the next generation of devices this is likely to be derived from the ACS9010 device . Backward compatibilty will be maintained. |

| 60<br>59             | POL1<br>POL2             | I | Polarity            | Defines the polarity of input<br>signal TPOS/TNEG.<br>NRZ,HDB3, B8SZ or AMI.                                                                                                                                      |

| 65                   | LOS                      | 0 | LOSS of<br>Signal   | When LOSS = 1, receive data is unreliable. When LOSS = 0, receive data is reliable.                                                                                                                               |

| 68                   | ERRL                     | 0 | Error Latch         | If errors are detected in the 8B10B coding rules ERRL will be forced high ERRL will be reset low if the device is forced out of synchronisation e.g. PORB = 0.                                                    |

| 69                   | ERRC                     | 0 | Error count         | ERRC will go high coincident with each error detected in the 8B10B coding rules. Errors may be accumulated by means of an external electronic counter.                                                            |

| 73<br>72<br>71<br>70 | DR1<br>DR2<br>DR3<br>DR4 | I | Data Rate<br>Select | The DR(4:1) input select the Data Rates and number of channels. See section headed Data Rate Selection                                                                                                            |

Pin Description ACS9010 part 1

| Pin          | Sym            | Ю | Name                               | Description                                                                                                                                                                                                 |

|--------------|----------------|---|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3            | RSET2          | - | PLL frequency set                  | Tie to DVDD at all times.                                                                                                                                                                                   |

| 6            | LASER          | Ι | LASER                              | LASER = 1, when interfacing to a LASER.<br>LASER = 0, when interfacing to a LED.                                                                                                                            |

| 7            | RSET           | ı | Receive Bias<br>Set                | Internally sets the bias current for the analogue cells. Connect a 10nF capacitor between RSET and GND.                                                                                                     |

| 8            | LASRX          | Ι | LAP/LAN<br>Receive                 | When LASRX = 1, LAP and LAN are connected to the receiver. Required for LED ping-pong applications.                                                                                                         |

| 13           | PINRX          | I | PINP/PINN<br>Receive               | When PINRX = 1, PINP and PINN are connected to the receiver.                                                                                                                                                |

| 14           | RxFLG          | 0 | Receive<br>Power Flag              | When RxFLG = 1, receiver power > RxMN threshold. When RxFLG = 0, receive power < RxMN threshold.                                                                                                            |

| 15           | RxMN           | 0 | Receive<br>Monitor                 | Receive power monitor.                                                                                                                                                                                      |

| 16           | RxVDD          | - | Receive<br>Power Supply            | Power supply, 4.75 - 5.25 Volts.                                                                                                                                                                            |

| 17           | RxGND          | - | Ground                             | Power supply.                                                                                                                                                                                               |

| 18<br>19     | COEF1<br>COEF2 | - | Compensation<br>Capacitor          | Differential offset compensation capacitor. Connect a 1nF capacitor between pins 18,19.                                                                                                                     |

| 24<br>25     | PINP<br>PINN   | - | PIN Anode<br>PIN Cathode           | Connections for pin-diode receiver.                                                                                                                                                                         |

| 26           | PMN            | - | LASER mon-<br>pin                  | Connection to Anode of LASER monitor-pin.                                                                                                                                                                   |

| 27           | TxVDD          | - | Transmit<br>Power Supply           | Power supply, 4.75 - 5.25 Volts.                                                                                                                                                                            |

| 28<br>29     | LAP<br>LAN     | - | LASER<br>Anode<br>LASER<br>Cathode | Connections to LASER OR LED.                                                                                                                                                                                |

| 30           | TxGND          | - | Ground                             | Power supply.                                                                                                                                                                                               |

| 2<br>4<br>41 | GND            | ı | Ground                             | Power supply                                                                                                                                                                                                |

| 31<br>35     | CTX1<br>CTX2   | - | Driver<br>Smoothing<br>Capacitor   | When using LEDs: Place a 10 nF capacitor between CTX1 and GND. Place a 10 nF capacitor between CTX2 and GND. When using LASERs: Place a 10 nF capacitor between CTX1 and GND. Connect CTX2 directly to GND. |

Pin Description ACS9010 part 2

PIN Description of interface signals between ACS9010 and ACS4050.

| Pin | Sym   | Ю                                  | Name                                                                                                       | Description                                                                                                             |

|-----|-------|------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 36  | TxMN  | ı                                  | Transmit<br>Power<br>Monitor                                                                               | Monitors transmit output power.                                                                                         |

| 37  | TxFLG | 0                                  | Transmit Power Flag  When TxFLG = 1, transpower > TxMN threshol When TxFLG = 0, transpower < TxMN threshol |                                                                                                                         |

| 38  | TSET  | ı                                  | Transmit<br>Power Setting                                                                                  | A $40 \mathrm{K}\Omega$ resistor placed between TSET and GND will set the appropriate transmit power level.             |

| 42  | DVDD  | DVDD - Rxdat Slicin, level voltage |                                                                                                            | Provides the appropriate slicing level for Rxdat+. Use resistor arrangement seen in <i>fig 5</i> of this specification. |

| Pin      | Sym    | Ю      | Name                                 | Description                                                                                                    |

|----------|--------|--------|--------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 32<br>39 | ENTX   | O<br>I | Enable<br>Transmit                   | Transmit window active (ACS4050). Enable transmit (ACS9010).                                                   |

| 31<br>9  | ENRXB  | O<br>I | Enable<br>Receive                    | Receive Window active (ACS4050). Enable receive (AC9010).                                                      |

| 20       | ENCOFB | I      | Enables DC<br>Offset<br>Compensation | Enables the DC offset compensation - ENCOFB is normally connected to ENRXB (ACS9010).                          |

| 28<br>40 | Txdat  | O<br>I | Transmit Burst<br>Data.              | Transmit burst data out (ACS4050). Transmit burst data in (ACS9010).                                           |

| 5<br>52  | Rxdat+ | O<br>I | Receive Burst<br>Data                | Positive Differential receive burst data out (ACS9010). Positive Differential receive burst data in (ACS4050). |

#### Single Fiber LED link

**Link Budget Example** (Rtset set so LED launch current = 100 mA peak)

| Fiber type<br>Fiber size                              | Plastic<br>1000 micron | Glass<br>62.5micron | Glass<br>50 micron |

|-------------------------------------------------------|------------------------|---------------------|--------------------|

| Minimum transmit couple power to fiber $(\mu W)$      | 1000                   | 100                 | 50                 |

| Minimum LED responsivity (A/W)                        | 0.01                   | 0.1                 | 0.12               |

| Minimum ACS405CS sensitivity (nA)                     | 1500                   | 1500                | 1500               |

| Minimum input power to ACS405CS amplifier ( $\mu W$ ) | 100                    | 15                  | 12.5               |

| Link budget (dB)                                      | 10                     | 8.24                | 6.0                |

#### Single Fiber LASER link

**Link Budget Example** (Rtset set so LASER launch current = 25 mA peak)

| Fiber type<br>Fiber size                                     | Glass (single mode)<br>9 micron |

|--------------------------------------------------------------|---------------------------------|

| Minimum transmit couple power to fiber $(\mu W)$             | 1000                            |

| Minimum LASER & PIN responsivity (A/W)                       | 0.25                            |

| Minimum ACS405CS sensitivity (nA)                            | 1000                            |

| Minimum input power to ACS405CS amplifier ( $\mu W$ )        | 4                               |

| Link budget (dB) (single mode fiber attenuation = 0.3 dB/km) | 24                              |

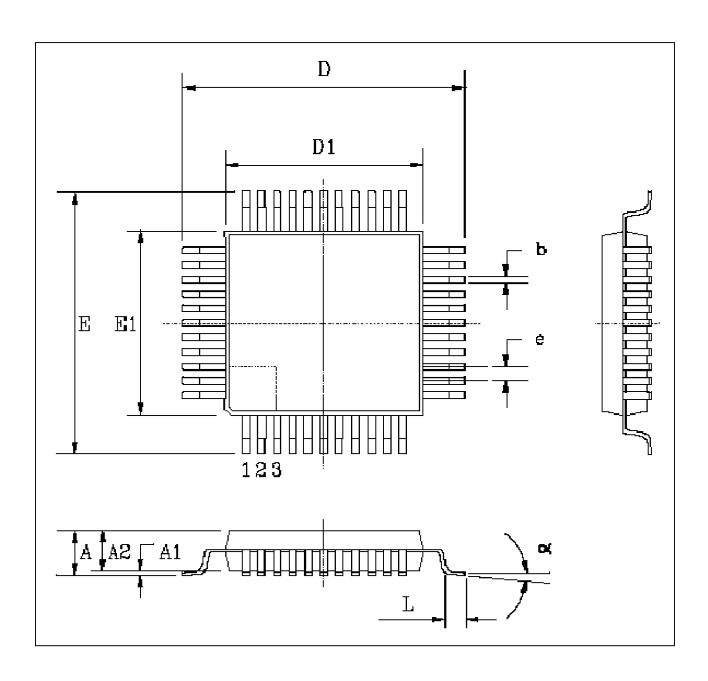

| Thin Quad Flat Pack dimensions in mm | E1/D1 | A    | A1   | A2   | e    | b    | L    | α  | E/D   | Copl. |

|--------------------------------------|-------|------|------|------|------|------|------|----|-------|-------|

| min                                  |       |      | 0.05 | 1.35 |      | 0.30 | 0.45 | 0° |       |       |

| TQFP44                               | 10.00 |      |      |      | 0.80 |      |      |    | 12.00 |       |

| max                                  |       | 1.60 | 0.15 | 1.45 |      | 0.45 | 0.75 | 7° |       | 0.10  |

| min                                  |       |      | 0.05 | 1.35 |      | 0.22 | 0.45 | 0° |       |       |

| TQFP80                               | 14.00 |      |      |      | 0.65 |      |      |    | 16.00 |       |

| max                                  |       | 1.60 | 0.15 | 1.45 |      | 0.38 | 0.75 | 7° |       | 0.10  |

Package information for the TQFP 44 and 80 pin packages

#### **Absolute Maximum Ratings**

| Parameter                                              | Symbol | Min     | Max     | Units |