## **Advance Information**

# ENHANCED PROGRAMMABLE COMMUNICATIONS INTERFACE (EPCI)

The MC2661/MC68661, Enhanced Programmable Communications Interface (EPCI), is a universal synchronous/asychronous data communications controller chip that is an enhanced version of the Signetics 2651. The EPCI directly interfaces to most 8-bit MPUs and easily to the MC68000 MPU and other 16-bit MPUs. It may be used in either a polled or interrupt driven system. Programmed instructions can be accepted from the host MPU while supporting many synchronous or asynchronous serial-data communication protocols in a full or half-duplex mode. Special support for BISYNC is provided.

The EPCI converts parallel data characters, accepted from the microprocessor data bus, into transmit-serial data. Simultaneously, the EPCI can convert receive-serial data to parallel data characters for input to the microprocessor.

A baud rate generator in the EPCI can be programmed to either accept an external clock, or to generate internal transmit or receive clocks. Sixteen different baud rates can be selected under program control when operating in the internal clock mode. Each version of the EPCI (A, B, C) has a different set of baud rates.

#### **FEATURES**

## Synchronous Operation

- Single or Double SYN Operation

- Internal or External Character Synchronization

- Transparent or Non-transparent Mode

- Transparent Mode DLE Stuffing (Tx) and Detection (Rx)

- Automatic SYN or DLE-SYN Insertion

- SYN, DLE, and DLE-SYN Stripping

- Baud Rate: dc to 1M bps (1X Clock)

## Asynchronous Operation

- 1, 1½, or 2 Stop Bits Transmitted

- Parity, Overrun, and Framing Error Detection

- Line Break Detection and Generation

- False Start Bit Detection

- Automatic Serial Echo Mode (Echoplex)

- Baud Rate: dc 1M bps (1X Clock)

dc to 62 5k bps (16X Clock)

dc to 62.5k bps (16X Clock) dc to 15.625k bps (64X Clock)

### Common Features

- Internal or External Baud Rate Clock; No System Clock Required

- 3 Baud Rate Sets (A, B, C); 16 Internal Rates for Each Set

- 5- to 8-Bit Characters plus parity; Odd, Even, or No Parity

- · Double Buffered Transmitter and Receiver

- · Dynamic Character Length Switching

- Full- or Half-Duplex Operation

- Local or Remote Maintenance Loop-Back Mode

- TTL-Compatible Inputs and Outputs

- RxC and TxC Pins and Short Circuit Protected

- 3 Open-Drain MOS Outputs can be Wire ORed

- Single 5 V Power Supply

#### Applications

- Intelligent Terminals

- Network Processors

- Front End Processors

- Remote Data Concentrators

- Computer-to-Computer Links

- Serial Peripherals

- BISYNC Adaptors

## MC2661A/MC68661A (Baud Rate Set A) MC2661B/MC68661B (Baud Rate Set B) MC2661C/MC68661C (Baud Rate Set C)

## MOS

(N-CHANNEL, SILICON-GATE)

ENHANCED PROGRAMMABLE COMMUNICATIONS INTERFACE (EPCI)

|             | PIN ASSIGN | IMEN | IT           |

|-------------|------------|------|--------------|

| D2 [        |            | 28   | ום ב         |

| D3 [        | 2          | 27   | <b>1</b> 00  |

| RxD [       | 3          | 26   | <b>ı</b> ∨cc |

| GND [       | 4          | 25   | RxC/BKDET    |

| D4 [        | 5          | 24   | J ÖTR        |

| D5 [        | 6          | 23   | ਸ ਜੋਵੇਂ      |

| D6 [        | 7          | 22   | DSR          |

| D7 [        | 8          | 21   | RESET        |

| TxC/XSYNC [ | 9          | 20   | BRCLK        |

| A1 [        | 10         | 19   | T TXD '      |

| CE [        | 11         | 18   | TXEMT/DSCHG  |

| A0 [        | 12         | 17   | n c⊤s        |

| R/W [       | 13         | 16   | व वटव        |

| RxRDY [     | 14         | 15   | TXRDY        |

|             |            |      | •            |

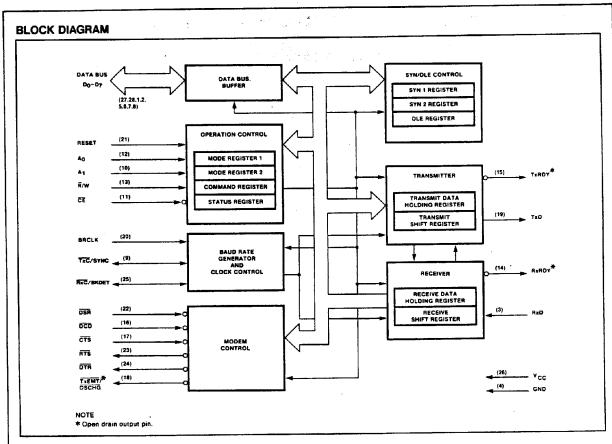

## **BLOCK DIAGRAM**

The EPCI consists of six major sections. These are the transmitter, receiver, timing, operation control, modem control and SYN/DLE control. These sections communicate with each other via an internal data bus and an internal control bus. The internal data bus interfaces to the microprocessor data bus via a data bus buffer.

## **Operation Control**

This functional block stores configuration and operation commands from the CPU and generates appropriate signals to various internal sections to control the overall device operation. It contains read and write circuits to permit communications with the microprocessor via the data bus and contains mode registers 1 and 2, the command register, and the status register. Details of register addressing and protocol are presented in the EPCI programming section of this data sheet.

Table 1 BAUD RATE GENERATOR CHARACTERISTICS Set A (BRCLK = 4.9152MHz)

| MR23-20 | BAUD<br>RATE | ACTUAL<br>FREQUENCY<br>16X CLOCK | PERCENT<br>ERROR | DIVISOR |

|---------|--------------|----------------------------------|------------------|---------|

| 0000    | 50           | 0.8kHz                           | -                | 6144    |

| 0001    | 75           | 1.2                              | -                | 4096    |

| 0010    | 110          | 1.7598                           | -0.01            | 2793    |

| 0011    | 134.5        | 2.152                            | -                | 2284    |

| 0100    | 150          | 2.4                              | -                | 2048    |

| 0101    | 200          | 3.2                              | -                | 1536    |

| 0110    | 300          | 4.8                              | -                | 1024    |

| 0111    | 600          | 9.6                              | -                | 512     |

| 1000    | 1050         | 16.8329                          | 0.196            | 292     |

| 1001    | 1200         | 19.2                             | -                | 256     |

| 1010    | 1800         | 28.7438                          | -0.19            | 171     |

| 1011    | 2000         | 31.9168                          | -0.26            | 154     |

| 1100    | 2400         | 38.4                             | -                | 128     |

| 1101    | 4800         | 76.8                             | -                | 64      |

| 1110    | 9600         | 153.6                            | -                | 32      |

| 1111    | 19200        | 307.2                            | -                | 16      |

#### Timing

The EPCI contains a baud rate generator (BRG) which is programmable to accept external transmit or receive clocks or to divide an external clock to perform data communications. The unit can generate 16 commonly used baud rates, any one of which can be selected for full duplex operation. See table 1.

#### Receiver

The receiver accepts serial data on the RxD pin, converts this serial input to parallel format, checks for bits or characters that are unique to the communication technique and sends an "assembled" character to the CPU.

#### **Transmitter**

The transmitter accepts parallel data from the CPU, converts it to a serial bit stream, inserts the appropriate characters or bits (based on the communication technique) and outputs a composite serial stream of data on the TxD output pin.

#### **Modem Control**

The modem control section provides interfacing for three input signals and three output signals used for "handshaking" and status indication between the CPU and a modem.

## SYN/DLE Control

This section contains control circuitry and three 8-bit registers storing the SYN1, SYN2, and DLE characters provided by the CPU. These registers are used in the synchronous mode of operation to provide the characters required for synchronization, idle fill and data transparency.

Table 1 BAUD RATE GENERATOR CHARACTERISTICS (Cont'd) Set B (BRCLK = 4.9152MHz)

| MR23-20 | BAUD<br>RATE | ACTUAL<br>FREQUENCY<br>16X CLOCK | PERCENT<br>ERROR | DIVISOR |

|---------|--------------|----------------------------------|------------------|---------|

| 0000    | 45.5         | 0.7279kHz                        | 0.005            | 6752    |

| 0001    | 50           | 0.8                              | -                | 6144    |

| 0010    | 75           | 1.2                              | -                | 4096    |

| 0011    | 110          | 1.7598                           | -0.01            | 2793    |

| 0100    | 134.5        | 2.152                            | -                | 2284    |

| 0101    | 150          | 2.4                              | -                | 2048    |

| 0110    | 300          | 4.8                              | -                | 1024    |

| 0111    | 600          | 9.6                              | -                | 512     |

| 1000    | 1200         | 19.2                             | -                | 256     |

| 1001    | 1800         | 28.7438                          | -0.19            | 171     |

| 1010    | 2000         | 31.9168                          | -0.26            | 154     |

| 1011    | 2400         | 38.4                             | -                | 128     |

| 1100    | 4800         | 76.8                             | _                | 64      |

| 1101    | 9600         | 153.6                            | -                | 32      |

| 1110    | 19200        | 307.2                            | -                | 16      |

| 1111    | 38400        | 614.4                            | -                | 8       |

#### Set C (BRCLK = 5.0688MHz)

| MR23-20 | BAUD<br>RATE | ACTUAL<br>FREQUENCY<br>16X CLOCK | PERCENT<br>ERROR | DIVISOR |

|---------|--------------|----------------------------------|------------------|---------|

| 0000    | 50           | 0.8kHz                           | -                | 6336    |

| 0001    | 75           | 1.2                              | -                | 4224    |

| 0010    | 110          | 1.76                             | -                | 2880    |

| 0011    | 134.5        | 2.1523                           | 0.016            | 2355    |

| 0100    | 150          | 2.4                              | -                | 2112    |

| 0101    | 300          | 4.8                              | -                | 1056    |

| 0110    | 600          | 9.6                              | -                | 528     |

| 0111    | 1200         | 19.2                             | -                | 264     |

| 1000    | 1800         | 28.8                             | -                | 176     |

| 1001    | 2000         | 32.081                           | 0.253            | 158     |

| 1010    | 2400         | 38.4                             | -                | 132     |

| 1011    | 3600         | 57.6                             | -                | 88      |

| 1100    | 4800         | 76.8                             | -                | 66      |

| 1101    | 7200         | 115.2                            | -                | 44      |

| 1110    | 9600         | 153.6                            | -                | 33      |

| 1111    | 19200        | 316.8                            | 3.125            | 16      |

NOTE

16X clock is used in asynchronous mode. In synchronous mode, clock multiplier is 1X and BRG can be used only for TxC.

## **ORDERING CODE**

| PACKAGES    | COMMERCIAL RANGES  VCC = 5V ±5%, TA = 0°C to 70°C        |                            |  |  |  |  |

|-------------|----------------------------------------------------------|----------------------------|--|--|--|--|

| Ceramic DIP | MC2661A/MC68661A<br>MC2661B/MC68661B<br>MC2661C/MC68661C | See table 1 for baud rates |  |  |  |  |

| Plastic DIP | MC2661A/MC68661A<br>MC2661B/MC68661B<br>MC2661C/MC68661C | See table 1 for baud rates |  |  |  |  |

| Table 2 CPU-RELATED SIG | NA | LS |

|-------------------------|----|----|

|-------------------------|----|----|

|                                |                       | INPUT/      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------|-----------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME                       | PIN NO.               | OUTPUT      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                | 26                    | 1           | +5V supply input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCC                            | 4                     | ·<br>       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

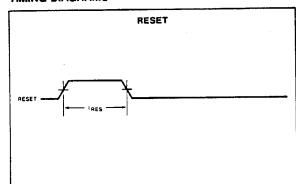

| GND                            | 21                    | 1           | A high on this input performs a master                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| HESE                           | ,                     | ·           | reset on the 2661. This signal asynchro-<br>nously terminates any device activity and<br>clears the mode, command and status reg-<br>isters. The device assumes the idle state<br>and remains there until initialized with the<br>appropriate control words.                                                                                                                                                                                                                                          |

| A <sub>1</sub> -A <sub>0</sub> | 10,12                 | 1           | Address lines used to select internal EPCI registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| R/W                            | 13                    | I           | Read command when low, write command when high.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CĒ                             | 11                    | 1           | Chip enable command. When low, indicates that control and data lines to the EPCI are valid and that the operation specified by the $\overline{R}/W$ , $A_1$ and $A_0$ inputs should be performed. When high, places the $D_0$ - $D_7$ lines in the three-state condition.                                                                                                                                                                                                                             |

| D <sub>7</sub> -D <sub>0</sub> | 8,7,6,5,<br>2,1,28,17 | 1/ <b>0</b> | 8-bit, three-state data bus used to transfer commands, data and status between EPCI and the CPU. Do is the least significant bit; D7 the most significant bit.                                                                                                                                                                                                                                                                                                                                        |

| TxRDY                          | 15                    | 0           | This output is the complement of status register bit SRO. When low, it indicates that the transmit data holding register (THR) is ready to accept a data character from the CPU. It goes high when the data character is loaded. This output is valid only when the transmitter is enabled. It is an open drain output which can be used as an interrupt to the CPU.                                                                                                                                  |

| RXRDY                          | 14                    | 0           | This output is the complement of status register bit SR1. When low, it indicates that the receive data holding register (RHR) has a character ready for input to the CPU. It goes high when the RHR is read by the CPU, and also when the receiver is disabled. It is an open drain output which can be used as an interrupt to the CPU.                                                                                                                                                              |

| TXEMT/<br>DSCHG                | 18                    | 0           | This output is the complement of status register bit SR2. When low, it indicates that the transmitter has completed serialization of the last character loaded by the CPU, or that a change of state of the DSR or DCD inputs has occurred. This output goes high when the status register is read by the CPU, if the TxEMT condition does not exist. Otherwise, the THR must be loaded by the CPU for this line to go high. It is an open drain output which can be used as an interrupt to the CPU. |

#### **OPERATION**

The functional operation of the 2661 is programmed by a set of control words supplied by the CPU. These control words specify items such as synchronous or asynchronous mode, baud rate, number of bits per character, etc. The programming procedure is described in the EPCI programming section of the data sheet.

After programming, the EPCI is ready to perform the desired communications functions. The receiver performs serial to parallel conversion of data received from a modem or equivalent device. The transmitter converts parallel data received from the CPU to a serial bit stream. These actions are accomplished within the framework specified by the control words.

#### Receiver

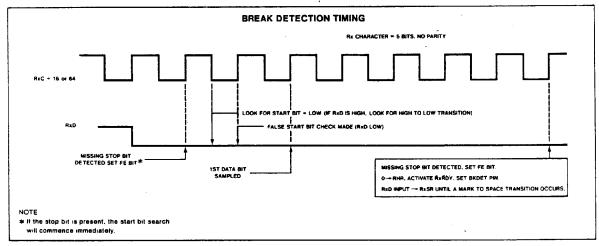

The 2661 is conditioned to receive data when the DCD input is low and the RxEN bit in the command register is true. In the asynchronous mode, the receiver looks for a high to low (mark to space) transition of the start bit on the RxD input line. If a transition is detected, the state of the RxD line is sampled again after a delay of one-half of a bit time. If RxD is now high, the search for a valid start bit is begun again. If RxD is still low, a valid start bit is assumed and the receiver continues to sample the input line at one bit time intervals until the proper number of data bits, the parity bit, and one stop bit have been assembled. The data are then transferred to the receive data holding register, the RxRDY bit in the status register is set, and the RxRDY output is asserted. If the character length is less than 8 bits, the high order unused bits in the holding register are set to zero. The parity error, framing error, and overrun error status bits are strobed into the status register on the positive going edge of RxC corresponding to the received character boundary. If the stop bit is present, the receiver will immediately begin its search for the next start bit. If the stop bit is absent (framing error), the receiver will interpret a space as a start bit if it persists into the next bit time interval. If a break condition is detected (RxD is low for the entire character as well as the stop bit), only one character consisting of all zeros (with the FE status bit SR5 set) will be transferred to the holding register. The RxD input must return to a high condition before a search for the next start bit begins.

Pin 25 can be programmed to be a break detect output by appropriate setting of MR27-MR24. If so, a detected break will cause that pin to go high. When RxD returns to mark for one RxC time, pin 25 will go low. Refer to the break detection timing diagram.

Table 3 DEVICE-RELATED SIGNALS

|            |         | INPUT/ |                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME   | PIN NO. | OUTPUT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                         |

| BRCLK      | 20      | 1      | Clock input to the internal baud rate generator (see table 1). Not required if external receiver and transmitter clocks are used.                                                                                                                                                                                                                                                                                |

| •RxC/BKDET | 25      | 1/0    | Receiver clock. If external receiver clock is programmed, this input controls the rate at which the character is to be received. Its frequency is 1X, 16X or 64X the baud rate, as programmed by mode register 1. Data are sampled on the rising edge of the clock. If internal receiver clock is programmed, this pin can be a 1X/16X clock or a break detect output pin.                                       |

| *TxC/XSYNC | 9       | 1/0    | Transmitter clock. If external transmitter clock is programmed, this input controls the rate at which the character is transmitted, Its frequency is 1X, 16X or 64X the baud rate, as programmed by mode register 1. The transmitted data changes on the falling edge of the clock. If internal transmitter clock is programmed, this pin can be a 1X/16X clock output or an external jam synchronization input. |

| RxD        | 3       | 1      | Serial data input to the receiver. "Mark" is high, "space" is low.                                                                                                                                                                                                                                                                                                                                               |

| TxD        | 19      | 0      | Serial data output from the transmitter. "Mark" is high, "space" is low. Held in mark condition when the transmitter is dis- abled.                                                                                                                                                                                                                                                                              |

| DSR        | 22      |        | General purpose input which can be used for data set ready or ring indicator condition. Its complement appears as status register bit SR7. Causes a low output on TxEMT/DSCHG when its state changes if CR2 or CR0 = 1.                                                                                                                                                                                          |

| DCD        | 16      | ı      | Data carrier detect input. Must be low in order for the receiver to operate. Its complement appears as status register bit SR6. Causes a low output on TxEMT/DSCHG when its state changes if CR2 or CR0 = 1. If DCD goes high while receiving, the RxC is internally inhibited.                                                                                                                                  |

| CTS        | 17      | 1      | Clear to send input. Must be low in order for the transmitter to operate. If it goes high during transmission, the character in the transmit shift register will be transmitted before termination.                                                                                                                                                                                                              |

| DTR        | 24      | 0      | General purpose output which is the com-<br>plement of command register bit CR1. Nor-<br>mally used to indicate data terminal ready.                                                                                                                                                                                                                                                                             |

| ĀTS        | 23      | O      | General purpose output which is the complement of command register bit CR5. Normally used to indicate request to send. If the transmit shift register is not empty when CR5 is reset (1 to 0), then RTS will go high one TxC time after the last serial bit is transmitted.                                                                                                                                      |

When the EPCI is initialized into the synchronous mode, the receiver first enters the hunt mode on a 0 to 1 transition of RxEN(CR2). In this mode, as data are shifted into the receiver shift register a bit at a time, the contents of the register are compared to the contents of the SYN1 register. If the two are not equal, the next bit is shifted in and the comparison is repeated. When the two registers match, the hunt mode is terminated and character assembly mode begins. If single SYN operation is programmed, the SYN DETECT status bit is set. If double SYN operation is programmed, the first character assembled after SYN1 must be SYN2 in order for the SYN DETECT bit to be set. Otherwise, the EPCI returns to the hunt mode. (Note that the sequence SYN1-SYN1-SYN2 will not achieve synchronization.) When synchronization has been achieved, the EPCI continues to assemble characters and transfer them to the holding register, setting the RxRDY status bit and asserting the RxRDY output each time a character is transferred. The PE and OE status bits are set as appropriate. Further receipt of the appropriate SYN sequence sets the SYN DETECT status bit. If the SYN stripping mode is commanded, SYN characters are not transferred to the holding register. Note that the SYN characters used to establish initial synchronization are not transferred to the holding register in any case.

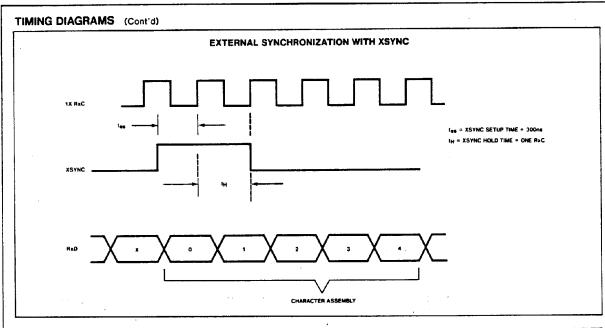

External jam synchronization can be achieved via pin 9 by appropriate setting of MR27-MR24. When pin 9 is an XSYNC input, the internal SYN1, SYN1-SYN2, and DLE-SYN1 detection is disabled. Each positive going signal on XSYNC will cause the receiver to establish synchronization on the rising edge of the next RxC pulse. Character assembly will start with the RxD input at this edge. XSYNC may be lowered on the next rising edge of RxC. This external synchronization will cause the SYN DETECT status bit to be set until the status register is read. Refer to XSYNC timing diagram.

## Transmitter

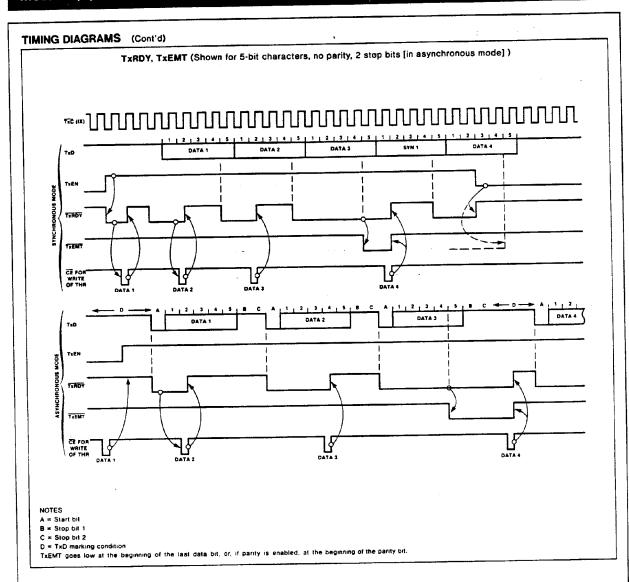

The EPCI is conditioned to transmit data when the CTS input is low and the TxEN command register bit is set. The 2661 indicates to the CPU that it can accept a character for transmission by setting the TxRDY status bit and asserting the TxRDY output. When the CPU writes a character into the transmit data holding register, these conditions are negated. Data are transferred from the holding register to the transmit shift register when it is idle or has completed transmission of the previous character. The TxRDY conditions are then asserted again. Thus, one full character time of buffering is provided.

NOTE

\*RXC and  $\overline{\text{TXC}}$  outputs have short circuit protection max.  $C_L=100pF$ . Outputs become open circuited upon detection of a zero pulled high or a one pulled low.

In the asynchronous mode, the transmitter automatically sends a start bit followed by the programmed number of data bits, the least significant bit being sent first. It then appends an optional odd or even parity bit and the programmed number of stop bits. If, following transmission of the data bits, a new character is not available in the transmit holding register, the TxD output remains in the marking (high) condition and the TxEMT/DSCHG output and its corresponding status bit are asserted. Transmission resumes when the CPU loads a new character into the holding register. The transmitter can be forced to output a continuous low (BREAK) condition by setting the send break command bit (CR3) high.

In the synchronous mode, when the 2661 is initially conditioned to transmit, the TxD output remains high and the TxRDY condition is asserted until the first character to be transmitted (usually a SYN character) is loaded by the CPU. Subsequent to this, a continuous stream of characters is transmitted. No extra bits (other than parity, if commanded) are generated by the EPCI unless the CPU fails to send a new character to the EPCI by the time the transmitter has completed sending the previous character. Since synchronous communication does not allow gaps between characters, the EPCI asserts TxEMT and automatically "fills" the gap by transmitting SYN1s, SYN1-SYN2 doublets, or DLE-SYN1 doublets, depending on the state of MR16 and MR17. Normal transmission of the message resumes when a new character is available in the transmit data holding register. If the SEND DLE bit in the command register is true, the DLE character is automatically transmitted prior to transmission of the message character in the THR.

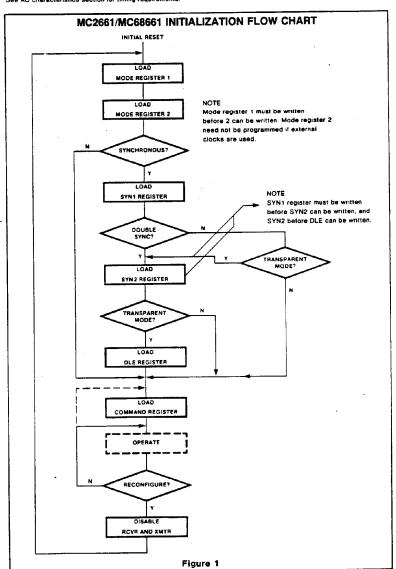

## **EPCI PROGRAMMING**

Prior to initiating data communications, the 2661 operational mode must be programmed by performing write operations to the mode and command registers. In addition, if synchronous operation is programmed, the appropriate SYN/DLE registers must be loaded. The EPCI can be reconfigured at any time during program execution. A flowchart of the intialization process appears in figure 1.

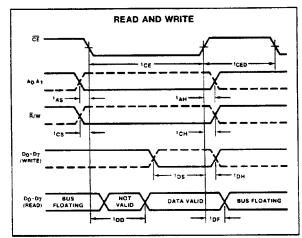

The internal registers of the EPCI are accessed by applying specific signals to the  $\overline{\text{CE}}$ ,  $\overline{R}/W$ ,  $A_1$  and  $A_0$  inputs. The conditions necessary to address each register are shown in table 4.

The SYN1, SYN2, and DLE registers are accessed by performing write operations with the conditions  $A_1=0$ ,  $A_0=1$ , and

Table 4 MC2661/MC68661 REGISTER ADDRESSING

| CE | A <sub>1</sub> | Ao  | R/W | FUNCTION                        |  |

|----|----------------|-----|-----|---------------------------------|--|

| 1  | ×              | X   | X   | Three-state data bus            |  |

| 0  | 0              | 0   | 0   | Read receive holding register   |  |

| 0  | 0              | . 0 | 1   | Write transmit holding register |  |

| 0  | ٥              | 1 1 | 0   | Read status register            |  |

| o  | 0              | 1   | 1   | Write SYN1/SYN2/DLE registers   |  |

| 0  | 1              | 0   | 0   | Read mode registers 1/2         |  |

| 0  | 1              | 0   | 1   | Write mode registers 1/2        |  |

| o  | 1              | 1   | 0   | Read command register           |  |

| 0  | 1              | 1   | 1   | Write command register          |  |

NOTE

See AC characteristics section for timing requirements

R/W = 1. The first operation loads the SYN1 register. The next loads the SYN2 register, and the third loads the DLE register. Reading or loading the mode registers is done in a similar manner. The first write (or read) operation addresses mode register 1, and a subsequent operation addresses mode register 2. If more than the required number of accesses are made, the internal sequencer recycles to point at the first register. The pointers are reset to SYN1 register and mode register 1 by a RESET input or by performing a read command register operation, but are unaffected by any other read or write operation.

The 2661 register formats are summarized in tables 5, 6, 7 and 8. Mode registers 1 and 2 define the general operational characteristics of the EPCI, while the command register controls the operation within this basic framework. The EPCI indicates its status in the status register. These registers are cleared when a RESET input is applied.

#### Mode Register 1 (MR1)

Table 5 illustrates Mode Register 1. Bits MR11 and MR10 select the communication format and baud rate multiplier. 00 specifies synchronous mode and 1X multiplier. 1X, 16X, and 64X multipliers are programmable for asynchronous format. However, the multiplier in asynchronous format applies only if the external clock input option is selected by MR24 or MR25.

MR13 and MR12 select a character length of 5, 6, 7 or 8 bits. The character length does not include the parity bit, if programmed, and does not include the start and stop bits in asynchronous mode.

MR14 controls parity generation. If enabled, a parity bit is added to the transmitted char-

acter and the receiver performs a parity check on incoming data. MR15 selects odd or even parity when parity is enabled by MR14.

In asynchronous mode, MR17 and MR16 select character framing of 1, 1.5, or 2 stop bits. (If 1X baud rate is programmed, 1.5 stop bits defaults to 1 stop bits on transmit.) in synchronous mode, MR17 controls the number of SYN characters used to establish synchronization and for character till when the transmitter is idle. SYN1 alone is used if MR17 = 1, and SYN1-SYN2 is used when MR17 = 0. If the transparent mode is specified by MR16, DLE-SYN1 is used for character fill and SYN detect, but the normal synchronization sequence is used to establish character sync. When transmitting, a DLE character in the transmit holding register will cause a second DLE character to be transmitted. This DLE stuffing eliminates the software DLE compare and stuff on each transparent mode data character. If the send DLE command (CR3) is active when a DLE is loaded into THR, only one additional DLE will be transmitted. Also, DLE stripping and DLE detect (with MR14 = 0) are enabled.

The bits in the mode register affecting character assembly and disassembly (MR12-MR16) can be changed dynamically (during active receive/transmit operation). The character mode register affects both the transmitter and receiver; therefore in synchronous mode, changes should be made only in half duplex mode (RxEN = 1 or TxEN = 1, but not both simultaneously = 1). In asynchronous mode, character changes should be made when RxEN and TxEN=0 or when TxEN = 1 and the transmitter is marking in half duplex mode (RxEN = 0).

To effect assembly/disassembly of the next received/transmitted character, MR12-15 must be changed within n bit times of the active going state of RxRDY/TxRDY. Transparent and non-transparent mode changes (MR16) must occur within n-1 bit times of the character to be affected when the receiver or transmitter is active. (n = smaller of the new and old character lengths.)

#### Mode Register 2 (MR2)

Table 6 illustrates mode register 2. MR23, MR21, MR21 and MR20 control the frequency of the internal baud rate generator (BRG). Sixteen rates are selectable for each EPCI version (A, B, C). Versions A and B specify a 4.9152 MHz TTL input at BRCLK (pin 20); version C specifies a 5.0688 MHz input which is identical to the Signetics 2651. MR23-20 are don't cares if external clocks are selected (MR25-MR24 = 0). The individual rates are given in table 1.

MR24-MR27 select the receive and transmit clock source (either the BRG or an external input) and the function at pins 9 and 25. Refer to table 6.

### Command Register (CR)

Table 7 illustrates the command register. Bits CR0 (TxEN) and CR2 (RxEN) enable or disable the transmitter and receiver respectively. A 0 to 1 transition of CR2 forces start bit search (async mode) or hunt mode (sync mode) on the second RxC rising edge. Disabling the receiver causes RxRDY to go high (inactive). If the transmitter is disabled, it will complete the transmission of the character in the transmit shift register (if any) prior to terminating operation. The TxD output will then remain in the marking state

Table 5 MODE REGISTER 1 (MR 1)

| MR17                                                                                        | MR16                                                  | MR15                       | MR14                        | MR13 MR12                                                | MR11 MR10                                                                                                         |  |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|-----------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| Sync/Async                                                                                  |                                                       | Parity Type Parity Control |                             | Character<br>Length                                      | Mode and Baud<br>Rate Factor                                                                                      |  |

| Async: Stop Bit Length  00 = Invalid  01 = 1 stop bit  10 = 1 % stop bits  11 = 2 stop bits |                                                       | 0 = Odd<br>1 = Even        | 0 = Disabled<br>1 = Enabled | 00 = 5 bits<br>01 = 6 bits<br>10 = 7 bits<br>11 = 8 bits | 00 = Synchronous 1X rate<br>01 = Asynchronous 1X rate<br>10 = Asynchronous 16X rate<br>11 = Asynchronous 64X rate |  |

| Sync:<br>Number of<br>SYN char<br>0 = Double<br>SYN<br>1 = Single<br>SYN                    | Sync: Transparency Control 0 = Normal 1 = Transparent |                            |                             |                                                          |                                                                                                                   |  |

NOTE

Baudirate factor in asynchronous applies only if external clock is selected. Factor is 18X if internal clock is selected. Mode must be selected (MR11, MR10) in any case.

Table 6 MODE REGISTER 2 (MR2)

|      | MR27-MR24 |     |       |        |      |     |     |            |         | MR23-MR20 |                           |

|------|-----------|-----|-------|--------|------|-----|-----|------------|---------|-----------|---------------------------|

|      | TxC       | RxC | Pin 9 | Pin 25 |      | TxC | RxC | Pin 9      | Pin 25  | Mode      | Baud Rate Selection       |

| 0000 | E         | E   | TxC   | RxC    | 1000 | E   | E   | XSYNC1     | RxC/TxC | sync      |                           |

| 0001 | Ē         | ī   | TxC   | 1X     | 1001 | E   | 1   | TxC        | BKDET   | async     |                           |

| 0010 | ī         | E   | 1X    | RxC    | 1010 | 1   | E   | XSYNC1     | RxC     | sync      |                           |

| 0011 | ì         | 1   | 1X    | 1X     | 1011 | 1   | - 1 | 1 <b>X</b> | BKDET   | async     | See baud rates in table 1 |

| 0100 | Ē         | E   | TxC   | RxC    | 1100 | E   | E   | XSYNC      | RxC/TxC | sync      |                           |

| 0101 | Ē         | ī   | TxC   | 16X    | 1101 | E   | 1   | TxC        | BKDET   | async     | <b>\</b>                  |

| 0110 | ī         | Ē   | 16X   | RxC    | 1110 | - 1 | Ε   | XSYNC      | RxC     | sync      |                           |

| 0111 | i         | ī   | 16X   | 16X    | 1111 | 1   | 1   | 16X        | BKDET   | async     | 1                         |

NOTE

### Table 7 COMMAND REGISTER (CR)

| CR7 CR6                                                                                                                                                                 | CR5                                                                                        | CR4                                                                         | CR3                                             | CR2                          | CR1                                                | CRO                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------|------------------------------|----------------------------------------------------|-------------------------------|

| Operating Mode                                                                                                                                                          | Request<br>To Send                                                                         | Reset Error                                                                 | Sync/Async                                      | Receive<br>Control<br>(RxEN) | Data Terminal<br>Ready                             | Transmit<br>Control<br>(TxEN) |

| Operating Mode  OD = Normal operation  O1 = Async:     Automatic     echo mode     Sync: SYN and/or     DLE stripping mode  10 = Local loop back  11 = Remote loop back | O = Force RTS output high one clock time after TxSR serialization 1 = Force RTS output low | 0 = Normal 1 = Reset error flags in status register (FE, OE, PE/DLE detect) |                                                 | 0 = Disable<br>1 = Enable    | 0 = Force DTR output high 1 = Force DTR output low | 0 = Disable<br>1 = Enable     |

|                                                                                                                                                                         |                                                                                            |                                                                             | Sync:<br>Send DLE<br>0 = Normal<br>1 = Send DLE | ,                            |                                                    |                               |

Table 8 STATUS REGISTER (SR)

| SR7               | SR6                                        | SR5                                          | SR4                                | SR3                                               | SR2                                                                       | SR1                                                                      | SR0                                                                    |

|-------------------|--------------------------------------------|----------------------------------------------|------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------|

| Data Set<br>Ready | Data Carrier<br>Detect                     | FE/SYN Detect                                | Overrun                            | PE/DLE Detect                                     | TxEMT/DSCHG                                                               | RxRDY                                                                    | TxRDY                                                                  |

|                   | 0 = DCD input is high 1 = DCD input is low | Async:<br>0 = Normal<br>1 = Framing<br>Error | O = Normal<br>1 = Overrun<br>Error | Async:<br>0 = Normal<br>1 = Parity error          | 0 = Normal 1 = Change in DSR, or DCD, or transmit shift register is empty | 0 = Receive holding register empty 1 = Receive holding register has data | 0 = Transmit holding register busy 1 = Transmit holding register empty |

|                   |                                            | Sync:<br>0 = Normal<br>1 = SYN<br>detected   |                                    | Sync: 0 = Normal 1 = Parity error or DLE received |                                                                           |                                                                          |                                                                        |

(high) while TxRDY and TxEMT will go high (inactive). If the receiver is disabled, it will terminate operation immediately. Any character being assembled will be neglected. A 0 to 1 transition of CR2 will initiate start bit search (async) or hunt mode (sync).

Bits CR1 (DTR) and CR5 (RTS) control the DTR and RTS outputs. Data at the outputs are the logical complement of the register data.

In asynchronous mode, setting CR3 will force and hold the TxD output low (spacing condition) at the end of the current transmitted character. Normal operation resumes when CR3 is cleared. The TxD line will go high for at least one bit time before beginning transmission of the next character in the transmit data holding register. In synchronous mode, setting CR3 causes the transmission of the DLE register contents prior to sending the character in the transmit

data holding register. Since this is a one time command, CR3 does not have to be reset by software. CR3 should be set when entering and exiting transparent mode and for all DLE—non-DLE character sequences.

Setting CR4 causes the error flags in the status register (SR3, SR4, and SR5) to be cleared. This is a one time command. There is no internal latch for this bit.

<sup>1.</sup> When pin 9 is programmed as XSYNC input, SYN1, SYN1-SYN2, and DLE-SYN1 detec-

tion is disabled.

E = External clock ( = internal clock (BRG)

<sup>1</sup>X and 16X are clock outputs

Table 9 MC2661/MC68661 EPCI vs SIGNETICS 2651 PCI

| FEATURE                                                         | EPCI                                                        | PCI                                                                               |

|-----------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 1. MR2 Bit 6, 7                                                 | Control pin 9, 25                                           | Not used                                                                          |

| 2. DLE detect-SR3                                               | SR3 = 0 for DLE-DLE,<br>DLE-SYNC1                           | SR3 = 1 for DLE-DLE,<br>DLE-SYNC1                                                 |

| 3. Reset of SR3, DLE detect                                     | Second character after DLE, or receiver disable, or CR4 = 1 | Receiver disable, or CR4 = 1                                                      |

| 4. Send DLE-CR3                                                 | One time command                                            | Reset via CR3 on next TxRDY                                                       |

| 5. DLE stuffing in<br>transparent mode                          | Automatic DLE stuffing when DLE is loaded except if CR3 = 1 | None                                                                              |

| SYNC1 stripping     in double sync     non-transparent     mode | All SYNC1                                                   | First SYNC1 of pair                                                               |

| 7. Baud rate versions                                           | Three                                                       | One                                                                               |

| 8. Terminate ASYNC transmission (drop RTS)                      | Reset CR5 in response to TxRDY changing from 0 to 1         | Reset CRO when TXEMT goes from 1 to 0. Then reset CR5 when TXEMT goes from 0 to 1 |

| 9. Break detect                                                 | Pin 251                                                     | FE and null character                                                             |

| 10. Stop bit searched                                           | One                                                         | Two                                                                               |

| 11. External jam sync                                           | Pin 9 <sup>2</sup>                                          | No                                                                                |

| 12. Data bus timing                                             | Improved over 2651                                          | -                                                                                 |

| <ol><li>Data bus drivers</li></ol>                              | Sink 2.2mA                                                  | Sink 1.6mA                                                                        |

|                                                                 | Source 400µA                                                | Source 100µA                                                                      |

NOTES

- 1. Internal BRG used for RxC.

- 2. Internal BRG used for TxC

When CR5 (RTS) is set, the RTS pin is forced low and the transmit serial logic is enabled. A 1 to 0 transition of CR5 will cause RTS to go high (inactive) one TxC time after the last serial bit has been transmitted (if the transmit shift register was not empty).

The EPCI can operate in one of four submodes within each major mode (synchronous or asynchronous). The operational sub-mode is determined by CR7 and CR6. CR7-CR6 = 00 is the normal mode, with the transmitter and receiver operating independently in accordance with the mode and status register instructions.

In asynchronous mode, CR7-CR6 = 01 places the EPCI in the automatic echo mode. Clocked, regenerated received data are automatically directed to the TxD line while normal receiver operation continues. The receiver must be enabled (CR2 = 1), but the transmitter need not be enabled. CPU to receiver communications continues normally, but the CPU to transmitter link is disabled. Only the first character of a break condition is echoed. The TxD output will go high until the next valid start is detected. The following conditions are true while in automatic echo mode:

- Data assembled by the receiver are automatically placed in the transmit holding register and retransmitted by the transmitter on the TxD output.

- The transmitter is clocked by the receive clock.

- TxRDY output = 1.

- 4. The TxEMT/DSCHG pin will reflect only the data set change condition.

- 5. The TxEN command (CR0) is ignored.

In synchronous mode, CR7-CR6 = 01 places the EPCI in the automatic SYN/DLE stripping mode. The exact action taken depends on the setting of bits MR17 and MR18:

- In the non-transparent, single SYN mode (MR17-MR16 = 10), characters in the data stream matching SYN1 are not transferred to the receive data holding register (RHR).

- In the non-transparent, double SYN mode (MR17-MR16 = 00), characters in the data stream matching SYN1, or SYN2 if immediately preceded by SYN1, are not transferred to the RHR.

- In transparent mode (MR16 = 1), characters in the data stream matching DLE, or SYN1 if immediately preceded by DLE, are not transferred to the RHR. However,

only the first DLE of a DLE-DLE pair is stripped.

Note that automatic stripping mode does not affect the setting of the DLE detect and SYN detect status bits (SR3 and SR5).

Two diagnostic sub-modes can also be configured. In local loop back mode (CR7-CR6 = 10), the following loops are connected internally:

- 1. The transmitter output is connected to the receiver input.

- 2. DTR is connected to DCD and RTS is connected to CTS.

- The receiver is clocked by the transmit clock.

- 4. The DTR, RTS and TxD outputs are held high.

- The CTS, DCD, DSR and RxD inputs are ignored.

Additional requirements to operate in the local loop back mode are that CR0 (TxEN), CR1 (DTR), and CR5 (RTS) must be set to 1. CR2 (RxEN) is ignored by the EPCI.

The second diagnostic mode is the remote loop back mode (CR7-CR8 = 11). In this mode:

- Data assembled by the receiver are automatically placed in the transmit holding register and retransmitted by the transmitter on the TxD output.

- The transmitter is clocked by the receive clock.

- No data are sent to the local CPU, but the error status conditions (PE, OE, FE) are set.

- 4. The RxRDY, TxRDY, and TxEMT/DSCHG outputs are held high.

- 5. CR1 (TxEN) is ignored.

- 6. All other signals operate normally.

#### Status Register

The data contained in the status register (as shown in table 8) indicate receiver and transmitter conditions and modem/data set status.

SR0 is the transmitter ready (TxRDY) status bit. It, and its corresponding output, are valid only when the transmitter is enabled. If equal to 0, it indicates that the transmit data holding register has been loaded by the CPU and the data has not been transferred to the transmit shift register. If set equal to 1, it indicates that the holding register is ready to accept data from the CPU. This bit is initially set when the transmitter is enabled by CR0, unless a character has previously been loaded into the holding register. It is not set when the automatic echo or remote loopback modes are programmed. When this bit is set, the TxRDY output pin is low. In

the automatic echo and remote loop back modes, the output is held high.

cleared by loading the transmit data holding register. The DSCHG condition is enabled

SR1, the receiver ready (RxRDY) status bit, indicates the condition of the receive data holding register. If set, it indicates that a character has been loaded into the holding register from the receive shift register and is ready to be read by the CPU. If equal to zero, there is no new character in the holding register. This bit is cleared when the CPU reads the receive data holding register or when the receiver is disabled by CR2. When set, the RxRDY output is low.

The TxEMT/DSCHG bit, SR2, when set, indicates either a change of state of the DSR or DCD inputs (when CR2 or CR0 = 1) or that the transmit shift register has completed transmission of a character and no new character has been loaded into the transmit data holding register. Note that in synchronous mode this bit will be set even though the appropriate "fill" character is transmitted. TxEMT will not go active until at least one character has been transmitted. It is

cleared by loading the transmit data holding register. The DSCHG condition is enabled when TxEN = 1 or RxEN = 1. It is cleared when the status register is read by the CPU. If the status register is read twice and SR2 = 1 while SR6 and SR7 remain unchanged, then a TxEMT condition exists. When SR2 is set, the TxEMT/DSCHG output is low.

SR3, when set, indicates a received parity error when parity is enabled by MR14. In synchronous transparent mode (MR16 = 1), with parity disabled, it indicates that a character matching DLE register was received and the present character is neither SYN1 nor DLE. This bit is cleared when the next character following the above sequence is loaded into RHR, when the receiver is disabled, or by a reset error command, CR4.

The overrun error status bit, SR4, indicates that the previous character loaded into the receive holding register was not read by the CPU at the time a new received character was transferred into it. This bit is cleared

when the receiver is disabled or by the reset error command, CR4.

In asynchronous mode, bit SR5 signifies that the received character was not framed by a stop bit, i.e., only the first stop bit is checked. If RHR = 0 when SR5 = 1, a break condition is present. In synchronous nontransparent mode (MR16 = 0), it indicates receipt of the SYN1 character in single SYN. mode or the SYN1-SYN2 pair in double SYN mode. In synchronous transparent mode  $(\dot{M}R16 = 1)$ , this bit is set upon detection of the initial synchronizing characters (SYN1 or SYN1-SYN2) and, after synchronization has been achieved, when a DLE-SYN1 pair is received. The bit is reset when the receiver is disabled, when the reset error command is given in asynchronous mode, or when the status register is read by the CPU in the synchronous mode.

SR6 and SR7 reflect the conditions of the DCD and DSR inputs respectively. A low input sets its corresponding status bit, and a high input clears it.

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| PARAMETER                                        | RATING       | UNIT |

|--------------------------------------------------|--------------|------|

| Operating ambient temperature <sup>2</sup>       | 0 to +70     | °C   |

| Storage temperature                              | -55 to +150  | °C   |

| All voltages with respect to ground <sup>3</sup> | -0.3 to +7.0 | V    |

#### THERMAL CHARACTERISTICS

| CHARACTERISTIC     | SYMBOL | VALUE | UNIT |

|--------------------|--------|-------|------|

| Thermal Resistance |        |       |      |

| Ceramic            |        | 50    |      |

| Plastic            | ALθ    | 100   | °C/W |

| Cerdip             |        | 60    |      |

## DC ELECTRICAL CHARACTERISTICS TA = 0°C to +70°C, VCC = 5.0V ±5% 4.5.6

|                         |                                                           |                                                     | LIMITS      |     |            |      |

|-------------------------|-----------------------------------------------------------|-----------------------------------------------------|-------------|-----|------------|------|

| PARAMETER               |                                                           | TEST CONDITIONS                                     | Min         | Тур | Max        | UNIT |

| V <sub>IL</sub><br>VIH  | Input voltage<br>Low<br>High                              |                                                     | -0.3<br>2.0 |     | 0.8<br>VCC | V    |

| V <sub>OL</sub><br>VOH' | Output voltage<br>Low<br>High                             | I <sub>OL</sub> = 2.2mA<br>I <sub>OH</sub> = -400µA | 2.4         |     | 0.4        | ٧    |

| ΊL                      | Input leakage current                                     | V <sub>IN</sub> = 0 to 5.5 V                        |             |     | 10         | μА   |

| ILH<br>ILL              | 3-state output leakage current Data bus high Data bus low | V <sub>OUT</sub> = 0 to 5.25 V                      |             |     | 10<br>10   | μА   |

| ICC                     | Power supply current                                      |                                                     |             |     | 150        | mA   |

## CAPACITANCE TA = 25°C, VCC = 0V

| PARAMETER  Capacitance C <sub>IN</sub> Input |                          |                                          | LIMITS |     |          |      |

|----------------------------------------------|--------------------------|------------------------------------------|--------|-----|----------|------|

|                                              |                          | TEST CONDITIONS                          | Min    | Тур | Max      | UNIT |

|                                              |                          | V <sub>IN</sub> = V <sub>OUT</sub> = 0 V | 20     |     | 20       | ρF   |

| C <sub>OUT</sub>                             | Output<br>Input / Output | tc = 1MHz Unmeasured pins tied to ground |        |     | 20<br>20 |      |

Notes on following page

## AC ELECTRICAL CHARACTERISTICS TA = 0°C to +70°C, VCC = 5.0V ± 5% 4.5.6

|                                                        | PARAMETER                                                                                                                                                                                | TEST CONDITIONS                                  | Min                                            | Тур              | Max                     | UNIT |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------|------------------|-------------------------|------|

| <sup>t</sup> RES<br><sup>t</sup> CE                    | Pulse width<br>Reset<br>Chip enable                                                                                                                                                      |                                                  | 1000<br>250                                    |                  |                         | ns   |

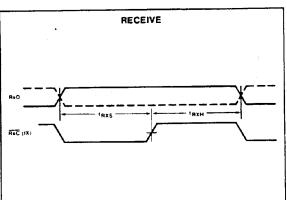

| tas<br>tah<br>tos<br>toh<br>tds<br>tdh<br>trxs<br>trxh | Setup and hold time Address setup Address hold R/W control setup R/W control hold Data setup for write Data hold for write Rx data setup Rx data hold                                    |                                                  | 10<br>10<br>10<br>10<br>150<br>0<br>300<br>350 |                  |                         | ns   |

| tDD<br>tDF<br>tCED                                     | Data delay time for read Data bus floating time for read CE to CE delay                                                                                                                  | C <sub>L</sub> = 150pF<br>C <sub>L</sub> = 150pF | 600                                            |                  | 200<br>100              | ns   |

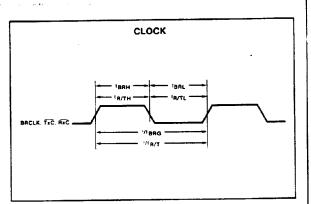

| fBRG<br>fBRG<br>fR/T                                   | Input clock frequency Baud rate generator (MC2661A,B/MC68661A,B) Baud rate generator (MC2661C/MC68661C) TxC or RxC                                                                       |                                                  | 1.0<br>1.0<br>dc                               | 4.9152<br>5.0688 | 4.9202<br>5.0738<br>1.0 | MHz  |

| tBRH9 tBRH9 tBRL9 tBRL9 tBRL7 tBRL7 tBRL7              | Clock width Baud rate high (MC2661A,B/MC68661A,B) Baud rate high (MC2661C/MC68661C) Baud rate low (MC2661A,B/MC68661A,B) Baud rate low (MC2661C/MC68661C) TxC or RxC high TxC or RxC low |                                                  | 75<br>70<br>75<br>70<br>480<br>480             |                  |                         | ns   |

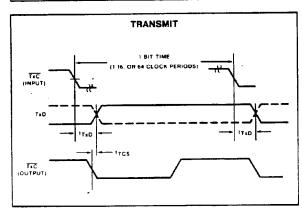

| †TXD                                                   | TxD delay from falling edge of TxC                                                                                                                                                       | CL = 150pF                                       | +                                              |                  | 650                     | ns   |

| tTCS                                                   | Skew between TxD changing and falling edge of TxC output <sup>8</sup>                                                                                                                    | C <sub>L</sub> = 150pF                           | TBD                                            |                  | TBD                     |      |

## NOTES

- 1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operation section of this specification is not implied

- 2. For operating at elevated temperatures, the device must be derated based on + 150°C maximum junction temperature and thermal resistance of 60°C/W junction to ambient (IQ ceramic

- 3. This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltages larger than the rated maxima.

4. Parameters are valid over operating temperature range unless otherwise specified.

- 5. All voltage measurements are referenced to ground. All time measurements are at the 50% level for inputs (except tggH and tggL) and at 0.8 V and 2.0 V for outputs. Input levels swing between 0.4 V and 2.4 V, with a transition time of 20ns maximum.

6. Typical values are at +28°C, typical supply voltages and typical processing parameters.

- 7. TxRDY, RxRDY and TxEMT/DSCHG outputs are open drain.

- 8. Parameter applies when internal transmitter clock is used.

- 9. Under test conditions of 5.0688 MHz IBRG (MC2661C/MC58881C) and 4.9152 MHz IBRG (MC2861A,B/MC68661A,B), IBRH and IBRL measured at VIH and VIL respectively.

#### **POWER CONSIDERATIONS**

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from:

TA = Ambient Temperature, °C

$\theta_{\rm JA}$  = Package Thermal Resistance, Junction-to-Ambient, °C/W

PD = PINT + PPORT

PINT=ICC×VCC, Watts - Chip Internal Power

PPORT ■ Port Power Dissipation, Watts - User Determined

drive Darlington bases or sink LED loads.

An approximate relationship between PD and TJ (if PPORT is neglected) is:

$$P_D = K + (T_J + 273$$

°C)

(2)

(1)

Solving equations 1 and 2 for K gives:

$$K = PD \bullet (T_A + 273 \circ C) + \theta JA \bullet PD^2$$

Where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring PD (at equilibrium) for a known TA. Using this value of K the values of PD and TJ can be obtained by solving equations (1) and (2) iteratively for any value of TA.

## TIMING DIAGRAMS

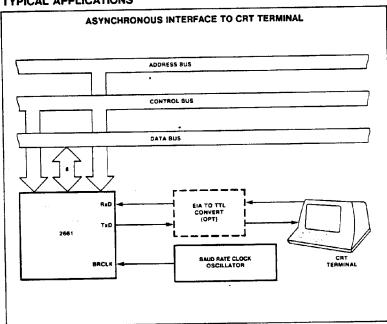

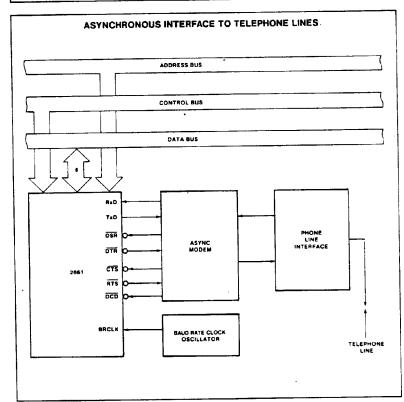

## TYPICAL APPLICATIONS

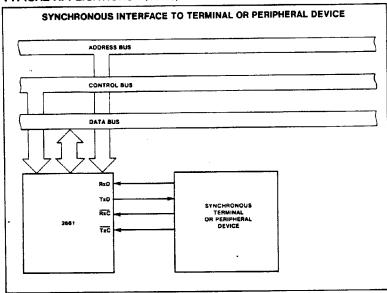

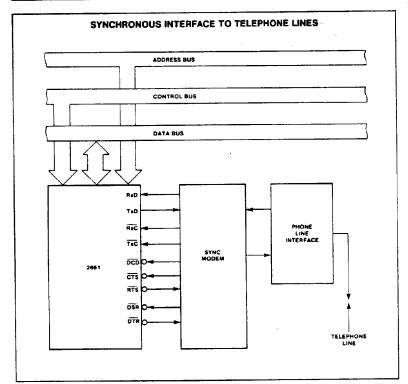

## TYPICAL APPLICATIONS (Cont'd)

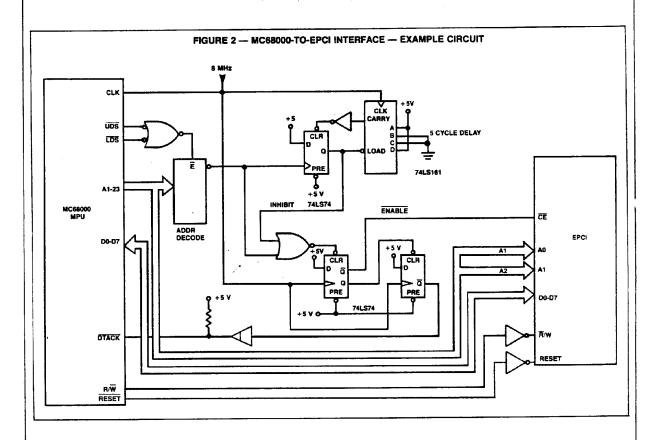

## MC68000 MPU-TO-EPCI INTERFACE REQUIREMENTS

The circuit shown in Figure 2 interfaces the EPCI to the MC68000 MPU. The 8-bit data bus of the EPCI is connected to the low order 8 bits of the MPU data bus (D0-D7). Due to this, the EPCI's registers are addressed on word (even byte) boundaries and so address line A1 of the MPU is connected to the A0 address line of the EPCI. Similarly, A2 of the MPU is connected to A1 of the EPCI. R/W on the MC68000 is inverted and connected to R/ W of the EPCI.

The CE signal must be generated for the EPCI and the DTACK signal must be supplied to the MPU. To allow for the data setup time on a read of the EPCI, CE must be delayed onehalf clock cycle and DTACK generated on the next rising edge of the system clock. This causes the processor to insert one wait state in the bus cycle. In addition to this, CE must not be reasserted until the chip enable period tCE has expired. Since some instructions on the MC68000 can cause access to consecutive addresses on consecutive bus cycles (e.g., MOVEP), an INHIBIT signal must be generated to hold-off an access during this period. A state machine consisting of a 74LS161 binary counter and a 74LS74 D flip-flop is configured as a digital "one shot." The rising edge of CE starts the counter which times out after given number of clock cycles. Since tCE is 600 ns. a minimum of 5 clock cycles at 8 MHz (625 ns) is required. The timing for two consecutive read bus cycles is shown in Figure 3. The IN-HIBIT signal prevents CE from being generated and DTACK from being asserted, causing the processor to generate wait states until IN-HIBIT is negated.

#### M6809 FAMILY MPU-TO-EPCI INTERFACE REQUIREMENTS

The M6809 family of microprocessors can be easily interfaced to the EPCI as shown in Figure 4.