## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# 4-Bit Single Chip-Microcomputer

## **Data Sheet**

#### Description

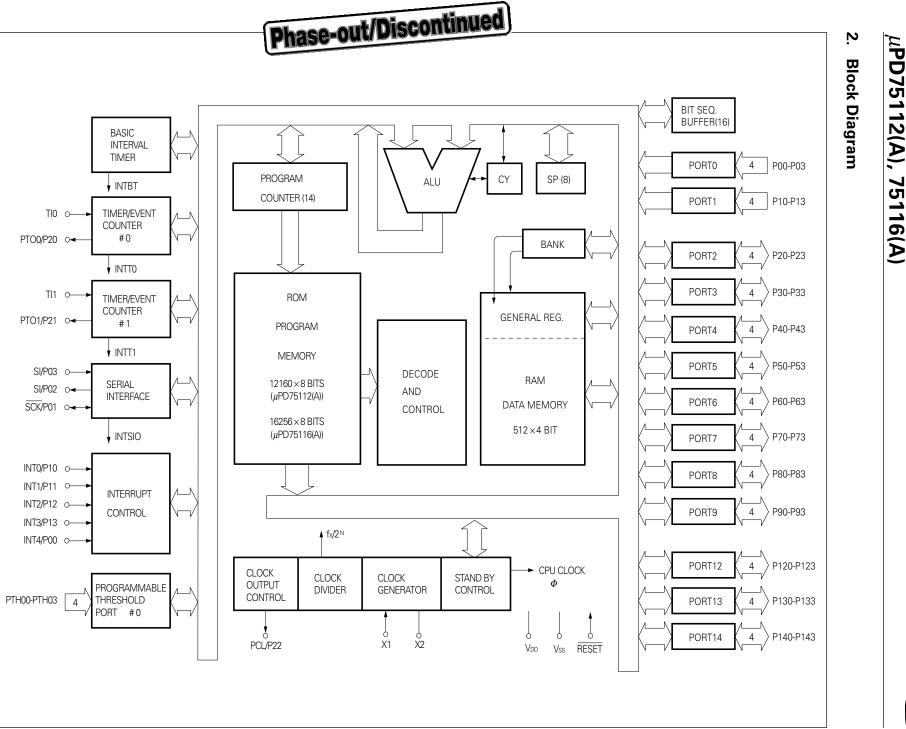

The  $\mu$ PD75116(A) is one of the 4-bit single-chip microcomputer 75X series.

The  $\mu$ PD75116(A) is a product with the extended ROM capacity of the  $\mu$ PD75108(A). In addition of high-speed operations, it can manipulate data in units of 1, 4 and 8 bits. In particular, the I/O operation of the  $\mu$ PD75116 have been improved by a wide variety of bit control instructions. The  $\mu$ PD75116 is provided with interface inputs/outputs with peripheral circuits having different power voltages, and analog inputs and suitable for controlling automobile electrical equipment, etc. For the  $\mu$ PD75116(A), an on-chip pin-compatible one-time PROM product ( $\mu$ PD75P116) is separately available for system development evaluation.

Functions are described in detail in the following User's Manual, which should be read when carrying out design work.

$\mu$ PD751×× Series User's Manual: IEM-992

#### Features

- Higher reliability than  $\mu$ PD75116

- Architecture "75X" equivalent to 8-bit microcomputer

- Minimum instruction execution time (high-speed operation): 0.95 μs (when operated at 4.19 MHz and 5 V)

- Instruction execution variable function: 0.95μs/1.91μs/ 15.3 μs (when operated at 4.19 MHz)

- Many input/output ports: 58

- 3-channel on-chip 8-bit timers

- 8-bit on-chip serial interface

- Multi-interruptible vector interrupt function

#### Applications

Automobile electrical equipment, etc.

| Ordering Code          | Package                                | Qualty Grade |

|------------------------|----------------------------------------|--------------|

| μPD75112CW(A)-×××      | 64-pin plastic shrink DIP              | Special      |

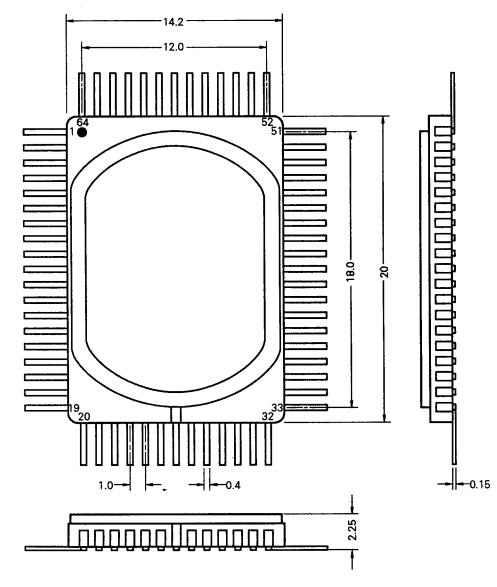

| μPD75112GF(A)-×××-3BE  | (750 mil)<br>64-pin plastic QFP        | Special      |

|                        | (14 × 20 mm)                           | Special      |

| $\mu$ PD75116CW(A)-XXX | 64-pin plastic shrink DIP<br>(750 mil) | Special      |

| μPD75116GF(A)-XX-3BE   | 64-pin plastic QFP<br>(14 × 20 mm)     |              |

**Remarks**: XXX is a ROM code number.

Please refer to "Quality Grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

Unless there are any particular functional differences, the  $\mu$ PD75116(A) is described in this document as a representative product.

The information in this document is subject to change without notice. The mark  $\bigstar$  shows major revised points.

#### Defferences between $\mu$ PD75112(A), 75116(A) and $\mu$ PD75112, 75116

|                                                    | Product Name |                                         |                         |

|----------------------------------------------------|--------------|-----------------------------------------|-------------------------|

| ltem                                               |              | μPD75112(A), 75116(A)                   | μPD75112, 75116         |

| Quality grade                                      |              | Special                                 | Standard                |

| Electrical specifications Absolute maximum ratings |              | Different high-level output current and | ow-level output current |

| DC characteristics                                 |              | Different low-level output voltage      |                         |

| Direct LED drive                                   |              | Not possible                            | Possible                |

#### **Outline of Functions**

| ltem                     |            | Description                                                                                                                                                                                                                                                                                                        |  |

|--------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| No. of basic instruction |            | 43                                                                                                                                                                                                                                                                                                                 |  |

| Min. instruction exect   | ution time | 0.95 $\mu$ s/1.91 $\mu$ s/15.3 $\mu$ s (when operated at 4.19 MHz), switchable at 3 levels                                                                                                                                                                                                                         |  |

| On-chip memory           | ROM        | 12160 × 8 (μPD75112(A)), 16256 × 8 (μPD75116(A))                                                                                                                                                                                                                                                                   |  |

|                          | RAM        | 512 × 4                                                                                                                                                                                                                                                                                                            |  |

| General register         |            | 4 bits $\times$ 8 $\times$ 4 banks (memory mapping)                                                                                                                                                                                                                                                                |  |

| Accumulator              |            | Three accumulated in compliance with controlled date lengths<br>•1-bit accumulator (CY), 4-bit accumulator (A), 8-bit accumulator (XA)                                                                                                                                                                             |  |

| Input/output port        |            | <ul> <li>58 in total</li> <li>CMOS input pin : 10</li> <li>CMOS input/output pin (LED direct drive enable): 32</li> <li>Intermediate withstand voltage N-ch open drain : 12<br/>input/output pin (bit-wise pull-up resistor inscorporation possible)</li> <li>Comparator input pin (4-bit accuracy) : 4</li> </ul> |  |

| Timer/counter            |            | <ul> <li>8-bit timer/event counter × 2</li> <li>8-bit basic interval timer (applicable to watchdog timer)</li> </ul>                                                                                                                                                                                               |  |

| Serial interface         |            | <ul> <li>8-bits</li> <li>First LSB/first MSB switchable</li> <li>Two transfer modes (transmit and receiver/receive dedicated mode)</li> </ul>                                                                                                                                                                      |  |

| Vector interrupt         |            | External : 3, Internal : 4                                                                                                                                                                                                                                                                                         |  |

| Test input               |            | External : 2                                                                                                                                                                                                                                                                                                       |  |

| Standby                  |            | STOP/HALT mode                                                                                                                                                                                                                                                                                                     |  |

| Operating temperatu      | re range   | -40 to +85°C                                                                                                                                                                                                                                                                                                       |  |

| Operating voltage        |            | 2.7 to 6.0 V                                                                                                                                                                                                                                                                                                       |  |

| Others                   |            | <ul> <li>On-chip power-on reset circuit (mask option)</li> <li>On-chip bit contol memory (bit sequential buffer)</li> </ul>                                                                                                                                                                                        |  |

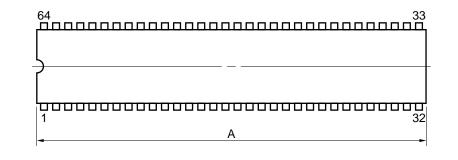

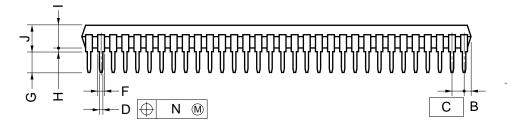

| Package                  |            | <ul> <li>64-pin plastic shrink DIP (750 mil)</li> <li>64-pin plastic QFP (14 × 20 mm)</li> </ul>                                                                                                                                                                                                                   |  |

**Phase-out/Discontinued**

μ**PD75112(A), 75116(A)**

#### CONTENTS

| 1.  | Pin Configuration (Top View)                                                                                                                               | 4                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 2.  | Block Diagram                                                                                                                                              | . 6                                            |

| 3.  | Pin Functions.         3.1 Port Pins.         3.2 Non-Port Pins.         3.3 Pin Input/Output Circuits.         3.4 Recommended Connection of Unused Pins. | . 7<br>8<br>9                                  |

| 4.  | 3.5 Caution Relating to Use of P00/INT4 Pin and RESET Pin<br>Memory Configuration                                                                          | 10                                             |

| 5.  | Peripheral Hardware Functions                                                                                                                              | 14                                             |

|     | <ul> <li>5.2 Clock Generator</li></ul>                                                                                                                     | 14<br>16<br>16<br>17<br>17<br>19<br>21<br>. 22 |

| 6.  | 5.9 Power-On Flag (Mask Option)                                                                                                                            |                                                |

| 7.  | Standby Functions                                                                                                                                          | 25                                             |

| 8.  | Reset Functions                                                                                                                                            | 26                                             |

| 9.  | Instruction Set                                                                                                                                            | 29                                             |

|     | Mask Option Selection                                                                                                                                      | 37                                             |

|     | Electrical Specifications                                                                                                                                  |                                                |

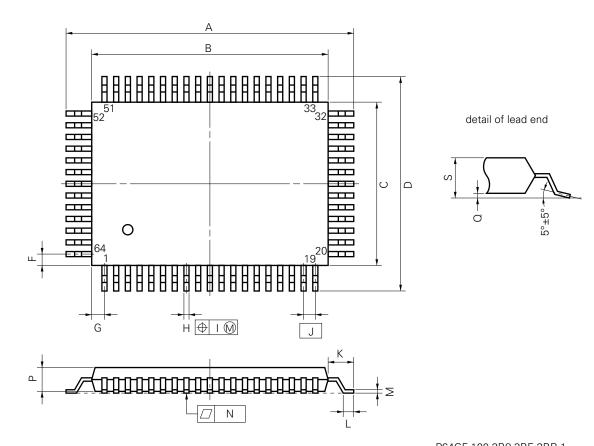

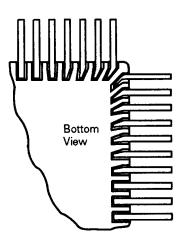

|     | Package Information                                                                                                                                        |                                                |

|     | Recommended Soldering Conditions                                                                                                                           | 51                                             |

| API | PENDIX A. Diffeences between µPD751××(A) Series Products<br>and Related PROM Products                                                                      | 52                                             |

| API | PENDIX B. Development Tools                                                                                                                                | 53                                             |

| API | PENDIX C. Related Documentations                                                                                                                           | 54                                             |

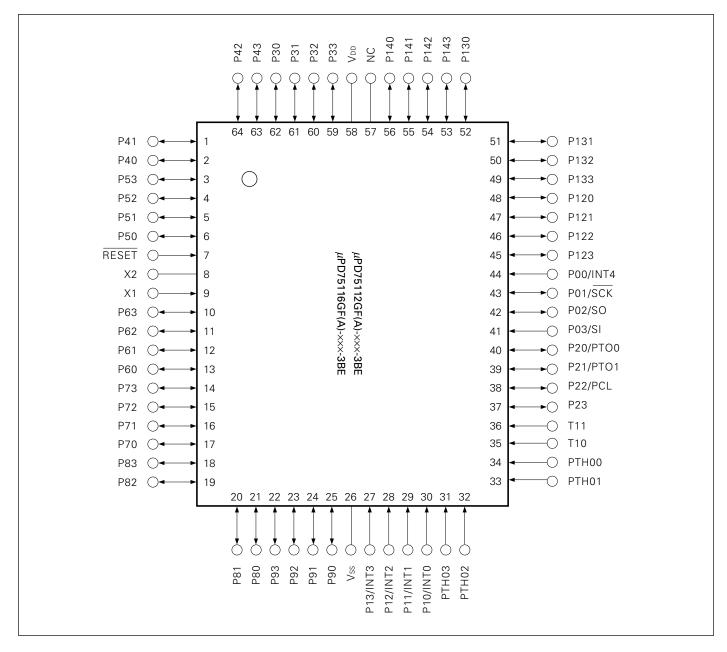

#### 1. Pin Configuration (Top View)

Г

#### 64-Pin Plastic Shrink DIP (750 mil)

| P13/INT3 🔘 | 1           |                                         | 64 ———————————————————————————————————— | Vss   |

|------------|-------------|-----------------------------------------|-----------------------------------------|-------|

| P12/INT2 〇 | → 2         | 6                                       | 63 <b>→→</b> ○                          | P90   |

| P11/INT1 🔘 | → 3         | 6                                       | 52 ←→○                                  | P91   |

| P10/INT0 🔿 | → 4         | 6                                       | 51 <b>▲→</b> ○                          | P92   |

| PTH03 🔘    | → 5         | 6                                       |                                         | P93   |

| PTH02 🔿    | 6           | Ę                                       | 59 ←→○                                  | P80   |

| PTH01 🔿    | <b>→</b> 7  | Ę                                       | 58                                      | P81   |

| PTH00 🔿    |             | Ę                                       | 57 ◀-►○                                 | P82   |

| TIO 🔘      | ▶ 9         | Ę                                       | 6 ←→○                                   | P83   |

| TI1 🔘      | <b>→</b> 10 | Ę                                       | 55                                      | P70   |

| P23 ()     | ◀ ▶ 11      | Ę                                       | 54 ◄►○                                  | P71   |

| P22/PCL 🔿  | ◀ ▶ 12      | Ę                                       | 53 ◀━►○                                 | P72   |

| P21/PTO1 🔿 | ◀ → 13      | 3 4 4                                   | 52 ◀ ◄ ► ◯                              | P73   |

| ,          | ◀ ▶ 14      | PD7                                     | 51                                      | P60   |

| P03/SI ()  | <b>→</b> 15 | µPD75112CW(A)->>><br>µPD75116CW(A)->>>> | 50 <b></b>                              | P61   |

| P02/SO 🔿   | ◀ ▶ 16      | 6CW 4                                   | l9 <b></b> ►○                           | P62   |

| P01/SCK 🔿  | ◄ ► 17      | /(A)                                    | 8                                       | P63   |

| P00/INT4 🔿 | <b>→</b> 18 | ××× 4                                   | 7                                       | X1    |

| P123 ()    | ◀ ▶ 19      |                                         | 46 <u> </u>                             | X2    |

| P122 ()    | <b>→</b> 20 | 2                                       | 45 <b>-</b>                             | RESET |

| P121 ()    | ◄ ► 21      | 2                                       | 4 ◀━━◯                                  | P50   |

| P120 🔿     | ←→ 22       | 2                                       | 43 ◀━►○                                 | P51   |

| P133 🔘     | ←→ 23       | 2                                       | 2 ←→○                                   | P52   |

| P132 🔿     | ◄ ► 24      | 2                                       | 1 ←→○                                   | P53   |

| P131 🔘     | ◄ ► 25      | 2                                       | 0 <b>→→</b>                             | P40   |

| P130 🔿     | ◄ ► 26      |                                         | 89 ←→○                                  | P41   |

| P143 🔘     | ◄ 27        | (                                       | 88                                      | P42   |

| P142 🔘     | ◄ 28        | (                                       | 37 ◀—▶○                                 | P43   |

| P141 🔘     | ←→ 29       | C                                       | 36 ◀-►○                                 | P30   |

| P140 🔿     | → 30        | :                                       | 85 ◀━►○                                 | P31   |

| NC 🔾       | 31          | :                                       | 34 ◀┻◯                                  | P32   |

| Vdd 🔿      | 32          |                                         | 33 ◀—▶○                                 | P33   |

**Phase-out/Discontinued**

μ**PD75112(A)**, 75116(A)

#### 64-Pin Plastic QFP (14 $\times$ 20 mm)

#### Pin Name \*

| P00-P03   | : Port0  | SCK              | : Serial Clock                      |

|-----------|----------|------------------|-------------------------------------|

| P10-P13   | : Port1  | SO               | : Serial Output                     |

| P20-P23   | : Port2  | SI               | : Serial Input                      |

| P30-P33   | : Port3  | PTO0, PTO1       | : Programmable Timer Output         |

| P40-P43   | : Port4  | PCL              | : Programmable Clock                |

| P50-P53   | : Port5  | PTH00-PTH03      | : Programmable Threshold Input      |

| P60-P63   | : Port6  | INT0, INT1, INT4 | : External Vectored Interrupt Input |

| P70-P73   | : Port7  | INT2, INT3       | : External Test Input               |

| P80-P83   | : Port8  | TI0, TI1         | : Timer Input                       |

| P90-P93   | : Port9  | <u>X1, X2</u>    | : Clock Oscillation                 |

| P120-P123 | : Port12 | RESET            | : Reset                             |

| P130-P133 | : Port13 | NC               | : No Connection                     |

| P140-P143 | : Port14 | Vdd              | : Positive Power Supply             |

|           |          | Vss              | : Ground                            |

6

# μ**PD75112(A)**,

#### 3. Pin Functions

#### 3.1 Port Pins

| Pin Name     | Input/ Output | Dual<br>Function Pin | Function                                                                                                                                              | 8-Bit I/O | At Reset        | I/O Circuit<br>Type * <b>1</b> |

|--------------|---------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|--------------------------------|

| P00          | Input         | INT4                 | 4-bit input port (PORT0)                                                                                                                              | ×         | Input           | B                              |

| P01          | Input/output  | SCK                  |                                                                                                                                                       |           |                 | E                              |

| P02          | Input/output  | SO                   |                                                                                                                                                       |           |                 | E                              |

| P03          | Input         | SI                   |                                                                                                                                                       |           |                 | B                              |

| P10          | Input         | INT0                 | 4-bit input port (PORT1)                                                                                                                              |           | Input           | B                              |

| P11          |               | INT1                 |                                                                                                                                                       |           |                 |                                |

| P12          |               | INT2                 |                                                                                                                                                       |           |                 |                                |

| P13          |               | INT3                 |                                                                                                                                                       |           |                 |                                |

| P20          | Input/output  | PTO0                 | 4-bit input/output port (PORT2)                                                                                                                       | ×         | Input           | E                              |

| P21          |               | PTO1                 |                                                                                                                                                       |           |                 |                                |

| P22          |               | PCL                  |                                                                                                                                                       |           |                 |                                |

| P23          |               |                      |                                                                                                                                                       |           |                 |                                |

| P30 to P33   | Input/output  |                      | Programmable 4-bit input/output port (PORT3)<br>Bit-wise input/output setting enable                                                                  |           | Input           | E                              |

| P40 to P43   | Input/output  |                      | 4-bit input/output port (PORT4)                                                                                                                       | 0         | Input           | E                              |

| P50 to P53   | Input/output  |                      | 4-bit input/output port (PORT5)                                                                                                                       |           | Input           | E                              |

| P60 to P63   | Input/output  |                      | Programmable 4-bit input/output port (PORT6)<br>Bit-wise input/output setting enable                                                                  | 0         | Input           | E                              |

| P70 to P73   | Input/output  |                      | 4-bit input/output port (PORT7)                                                                                                                       |           | Input           | E                              |

| P80 to P83   | Input/output  |                      | 4-bit input/output port (PORT8)                                                                                                                       | 0         | Input           | E                              |

| P90 to P93   | Input/output  |                      | 4-bit input/output port (PORT9)                                                                                                                       |           | Input           | E                              |

| P120 to P123 | Input/output  |                      | N-ch open drain 4-bit input/ output port (PORT12)<br>Bit-wise pull-up resistor incorporation enable<br>(mask option)<br>2 V withstand for open drain  | 0         | Input* <b>2</b> | М                              |

| P130 to P133 | Input/output  |                      | N-ch open drain 4-bit input/ output port (PORT13)<br>Bit-wise pull-up resistor incorporation enable<br>(mask option)<br>12 V withstand for open drain |           | Input* <b>2</b> | М                              |

| P140 to P143 | Input/output  |                      | N-ch open drain 4-bit input/output port (PORT14)<br>Bit-wise pull-up resistor incorporation enable<br>(mask option)<br>12 V withstand for open drain  |           | Input* <b>2</b> | М                              |

<sup>\* 1:</sup> Circles indicate Schmitt trigger inputs.

2: High impedance for open drain High level for on-chip pull-up resistors

#### 3.2 Non-Port Pins

|                | Input/Output | Dual<br>Function<br>Pin | Function                                                                                                                                     | At Reset | l/O<br>Circuit<br>Type* <b>1</b> |

|----------------|--------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------|

| PTH00 to PTH03 | Input        |                         | Threshold voltage ariable 4-bit analogy input port.                                                                                          |          | N                                |

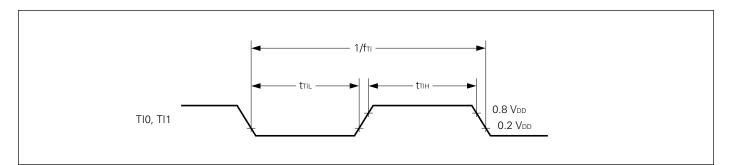

| TIO<br>TI1     | Input        |                         | External event pulse input for the timer/event counter or edge detect vector interrupt input. 1-bit input enable.                            |          | В                                |

| PTO0           | Input/output | P20                     | Timer/event counter output.                                                                                                                  | Input    | E                                |

| PTO1           |              | P21                     |                                                                                                                                              |          |                                  |

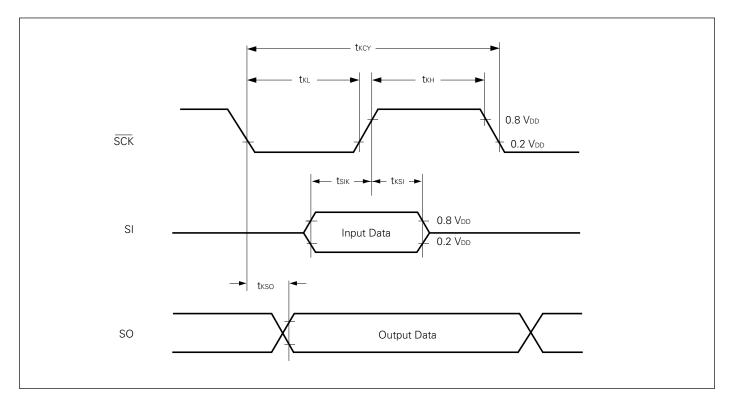

| SCK            | Input/output | P01                     | Serial clock input/output.                                                                                                                   | Input    | F                                |

| SO             | Input/output | P02                     | Serial data output.                                                                                                                          | Input    | E                                |

| SI             | Input        | P03                     | Serial data input.                                                                                                                           | Input    | В                                |

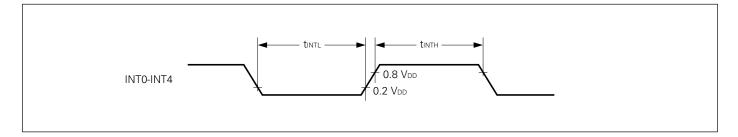

| INT4           | Input        | P00                     | Edge detect vector interrupt input (for detecting both rising and falling edges).                                                            | Input    | B                                |

| INT0           | Input        | P10                     | Edge detect vector interrupt input (detected edge selectable).                                                                               | Input    | В                                |

| INT1           |              | P11                     |                                                                                                                                              |          |                                  |

| INT2           | Input        | P12                     | Edge detect testable input (for rising edge detection).                                                                                      | Input    | В                                |

| INT3           |              | P13                     |                                                                                                                                              |          |                                  |

| PCL            | Input/output | P22                     | Clock output.                                                                                                                                | Input    | E                                |

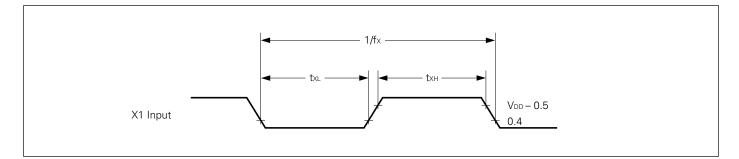

| X1, X2         |              |                         | Crystal/ceramic connect pin (system clock oscillation).<br>In case with the external clock, input a signal to X1 and the<br>antiphase to X2. |          |                                  |

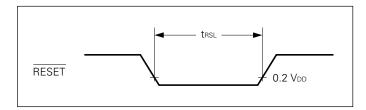

| RESET          | Input        |                         | System reset input (low level active).                                                                                                       |          | В                                |

| NC*2           |              |                         | No Connection                                                                                                                                |          |                                  |

| Vdd            |              |                         | Positive power supply.                                                                                                                       |          |                                  |

| Vss            |              |                         | GND potential.                                                                                                                               |          |                                  |

\* 1: Circles indicate Schmitt trigger inputs. 2: When the PWB is shared with the  $\mu$ PD75P116, connect the NC pin to VDD directly.

# NEC

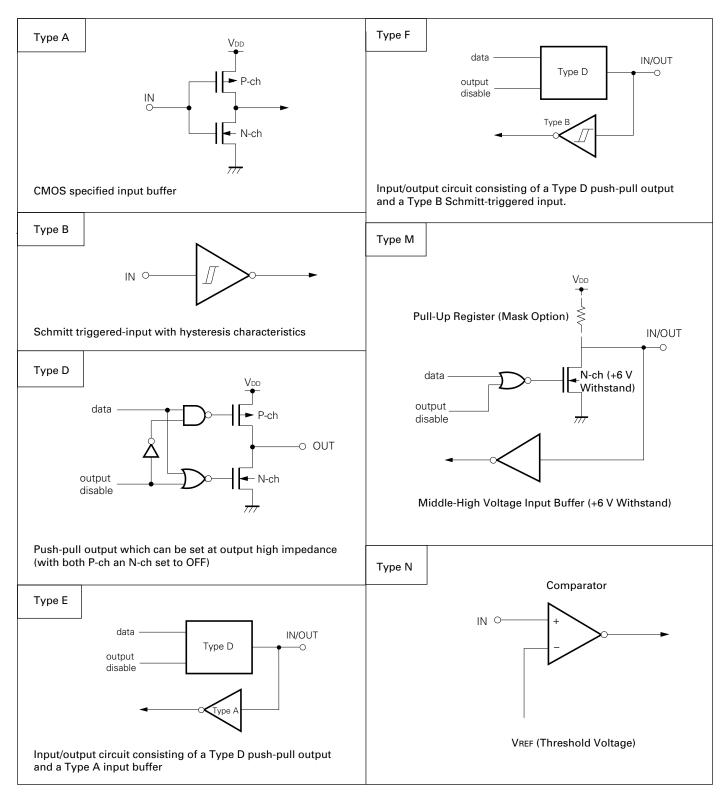

#### 3.3 Pin Input/Output Circuits

$\mu \text{PD75116}(\text{A})$  pin input/output crcuit are shown in schematic form.

#### Figure 3-1 Pin Input/Output Circuits

#### 3.4 Recommended Connection of Unused Pins

| Pin            | Recommended Connecting Method       |

|----------------|-------------------------------------|

| PTH00 to PTH03 | Connect to Vss or VDD               |

| тю             |                                     |

| TI1            |                                     |

| P00            | Connect to Vss                      |

| P01 to P03     | Connect to Vss or VDD               |

| P10 to P13     | Connect to Vss                      |

| P20 to P23     | Input state : Connect to Vss or VDD |

| P30 to P33     | Output state: Leave open            |

| P40 to P43     |                                     |

| P50 to P53     |                                     |

| P60 to P63     |                                     |

| P70 to P73     |                                     |

| P80 to P83     |                                     |

| P90 to P93     |                                     |

| P120 to P123   |                                     |

| P130 to P133   |                                     |

| P140 to P143   |                                     |

| RESET          | Connect to VDD*1                    |

| NC             | Leave open or connect to VDD*2      |

- \*1: Only when a power-on reset generator is built in by mask option, connect t VDD.

- 2: When the PWB is shared with the  $\mu \rm PD75P116,$  connect the NC pin to VDD directly.

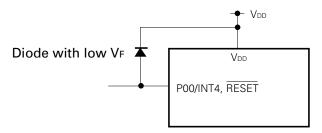

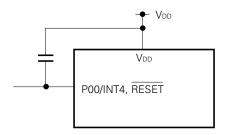

**3.5 Caution Relating to Use of P00/INT4 Pin and RESET Pin** In addition to the functions described in sections 3.1 and 3.2, the P00/INT4 pin and the RESET pin have the function to set the IC test mode for testing the  $\mu$ PD75116(A) internal operations.

When a voltage larger than VDD is applied to one of these two pins, the test mode is set. Thus, if noise exceeding VDD is applied even during normal operations, the test mode is set and normal operations may be discontinued.

For example, if a cable from the P00/INT4 or RESET pin is too long, inter-wiring noise may be applied to the pin, the pin voltage may become larger than VDD, causing malfunctioning.

Thus, carry out wiring to minimize inter-wiring noise. If the noise cannot be suppressed completely, carry out the following countermeasure against noise using an externally mounted component.

o Connect a diode with low VF (max 0.3 V) between VDDs

o Connect acapacitor between VDDs

# **Phase-out/Discontinued**

## μ**PD75112(A), 75116(A)**

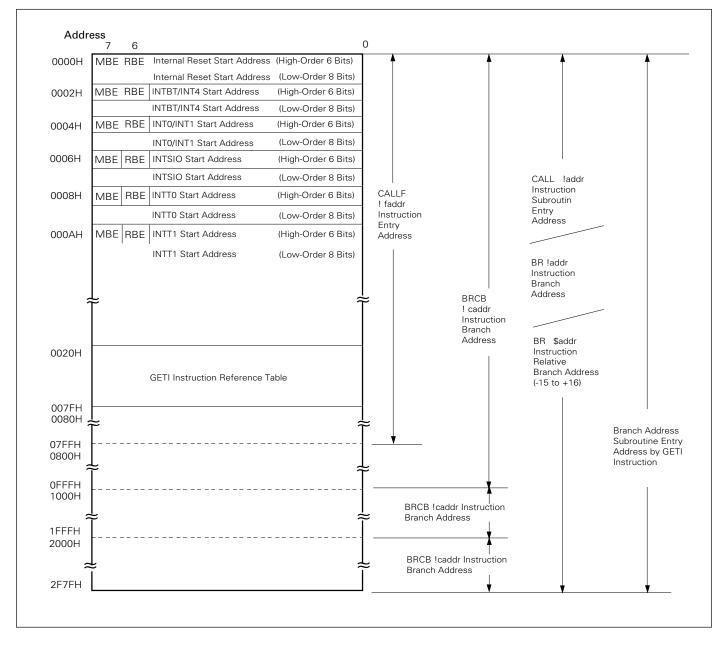

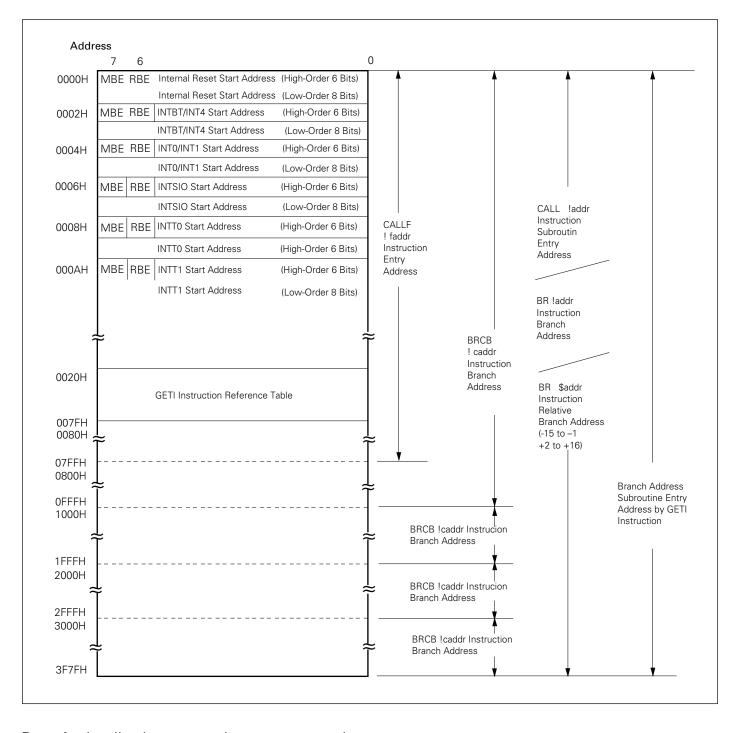

#### 4. Memory Configuration

- Program Memory (ROM) 12160 × 8 bits (0000H to 2F7FH): μPD75112(A) 16256 × 8 bits (0000H to 3F7FH): μPD75116(A)

- 0000H to 0001H: Vector table for writing the program start address by reset

- 0002H to 000BH: Vector table for writing the program start address by interrupt

#### Figure 4-1 Program Memory Map (µPD75112(A))

- 0020H to 007FH: Table area to be referred to by the GETI instruction

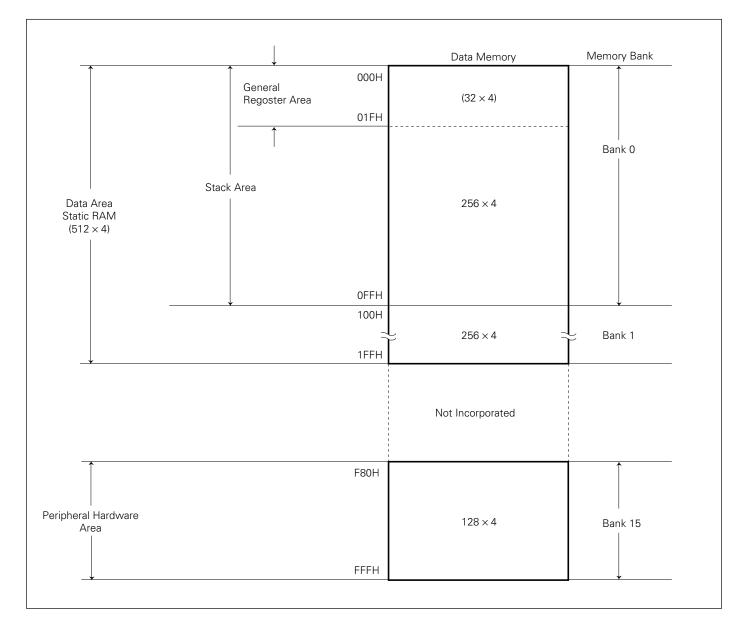

- Data Memory

- Data area 512 × 4 bits (000H to 1FFH)

- Peripheral hardware area

- 128 imes 4 bits (F80H to FFFH)

**Remarks**: In all other cases, the program can be branched by the BR PCDE and BR PCXA

instructions to an address with only the lower 8 bits of PC changed.

## μ**PD75112(A)**, **75116(A)**

#### Figure 4-2 Program Memory Map (µPD75116(A))

**Remarks:** In all other cases, the program can be branched by the BR PCDE and BR PCXA instructions to an address with only the lower 8 bits of PC changed.

**Phase-out/Discontinued**

μ**PD75112(A), 75116(A)**

#### Figure 4-3 Data Memory Map

52

#### 5. Peripheral Hardware Functions

#### 5.1 Digital Input/Output Port

The digital input/output port has the following tree types.

- CMOS input (PORT0, 1) : 8

- CMOS input/output (PORT 2 to PORT 9) : 32

- N-ch open-drain input/output (PORT 12 to PORT 14): 12

Total

#### **Table 5-1 Functions of Digital Ports**

| Port (Code)                                        | Functions                                                                     | Operations and Features                                                                                                                                  | Remarks                                                             |

|----------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| PORT0<br>PORT1                                     | 4-bit input                                                                   | Read or test always enable irrespectively of the operating mode of dual-function pins.                                                                   | Share the pins with SI, SO, SCK and INT0 to 4.                      |

| PORT3<br>PORT6                                     | 4-bit input/<br>output                                                        | Can be set bit-wise to the input or output mode.                                                                                                         |                                                                     |

| PORT2<br>PORT4<br>PORT5<br>PORT7<br>PORT8<br>PORT9 |                                                                               | Can be set in 4-bit units to the input or output mode.<br>Ports 4 and 5, 6 and 7, 8 and 9 can form pairs and data can be<br>input/output in 8-bit units. | Port 2 shares the pin with PTO0,<br>PTO1 and PCL.                   |

| PORT12<br>PORT13<br>PORT14                         | 4-bit input/<br>output<br>(N-ch open-<br>drain, 12 V<br>withstand<br>voltage) | Can be set in 4-bit units the input or output mode.<br>Ports 12 and 13 can form a pair and data can be input/output in 8-<br>bit units.                  | On-chip pull-up registers can be specified bit-wise by mask option. |

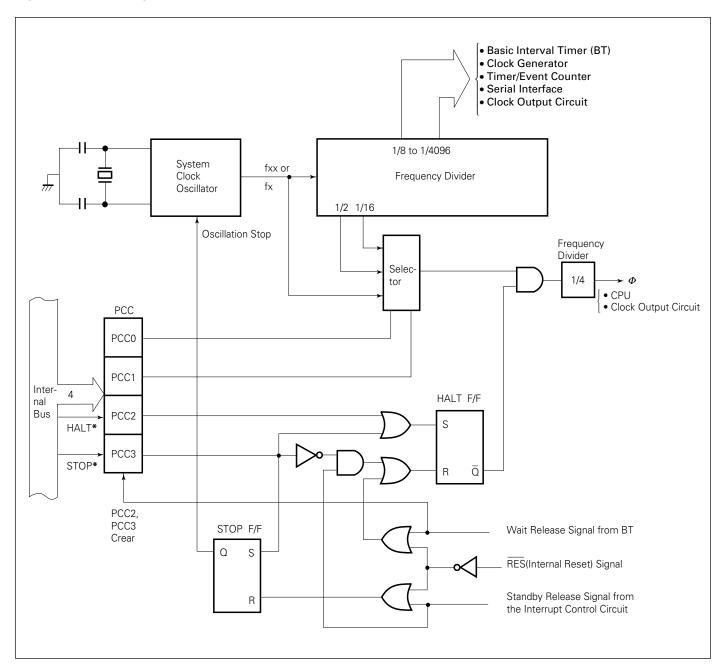

#### 5.2 Clock Generator

The clock generator is a circuit which supplies the CPU and peripheral hardware with various clocks and controls the CPU operating mode.

The instruction execution time can be changed.

• 0.95 μs/1.91 μs/15.3 μs (at 4.19 MHz operation)

# NEC

**Phase-out/Discontinued** µPD75112(A), 75116(A)

#### Figure 5-1 Block Diagram of Clock Generator ★

- **Remarks 1**: fxx=crystal/ceramic oscillator frequency.

- 2: fx=external clock frequency.

- 3: *Ф*=CPU clock

- **4**: \*indicates instruction execution.

- 5: PCC (processor clock control register)

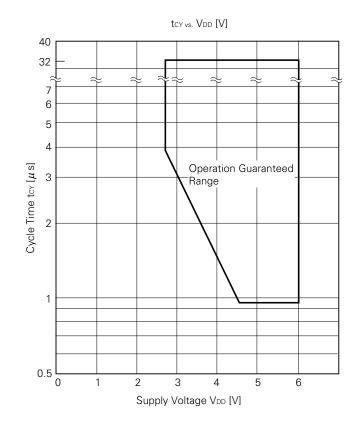

- 6: 1 clock cycle (tcr) of Φ is 1 michine cycle of the instruction. For tcr, see the AC characteristics in the 11."Electrical Specifications".

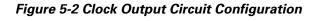

### 5.3 Clock Output Circuit

μ**PD75112(A)**, 75116(A)

The clock output circuit is a circuit to generate clock pulses from the P22/PCL pin. It is used to supply the peripheral LSIs with clock pulses.

•Clock output (PCL): $\Phi$ , 524 kHz, 262 kHz (at 4.19 MHz operation)

The clock output cicuit configuration is shown as the following.

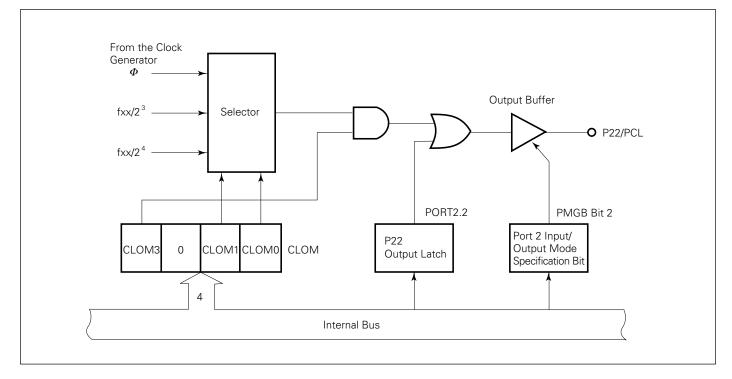

#### 5.4 Basic Interval Timer

The basic interval timer has the following functions;

- Interval timer operation to generate reference time interrupts

- Watchdog timer application to detect program overrun

- Wait time selection and count when the standby mode is released

- Count content read

# NEC

**Phase-out/Discontinued**

μ**PD75112(A), 75116(A)**

Figure 5-3 Basic Interval Timer Configuration

Remark: \* indicates instruction execution.

#### 5.5 Timer/Event Counter

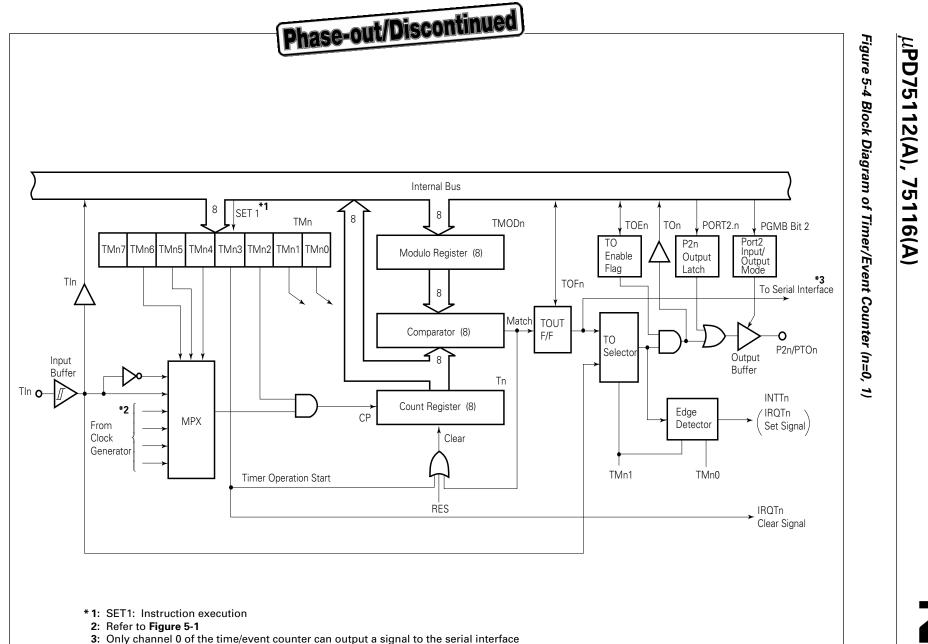

The  $\mu$ PD75116(A) has a two-channel on-chip timer/ event counters.

Channels 0 and 1 of the timer/event counter have the same configuration and functions. They differ only in the selectable count pulse (CP) and the function of supplying clocks to the serial interface.

The timer/event counter has the following functions:

- Programmable interval timer operation

- Output of square wave having any selected frequency to PTOn pin

- Event counter operation

- Use of TIn pin as an external interrupt input pin

- Output of TIn pin input divided by N to PTOn pin (frequency divider operation)

- Serial shift clock supply to the serial interface circuit (channel 0 only)

- Count status read function

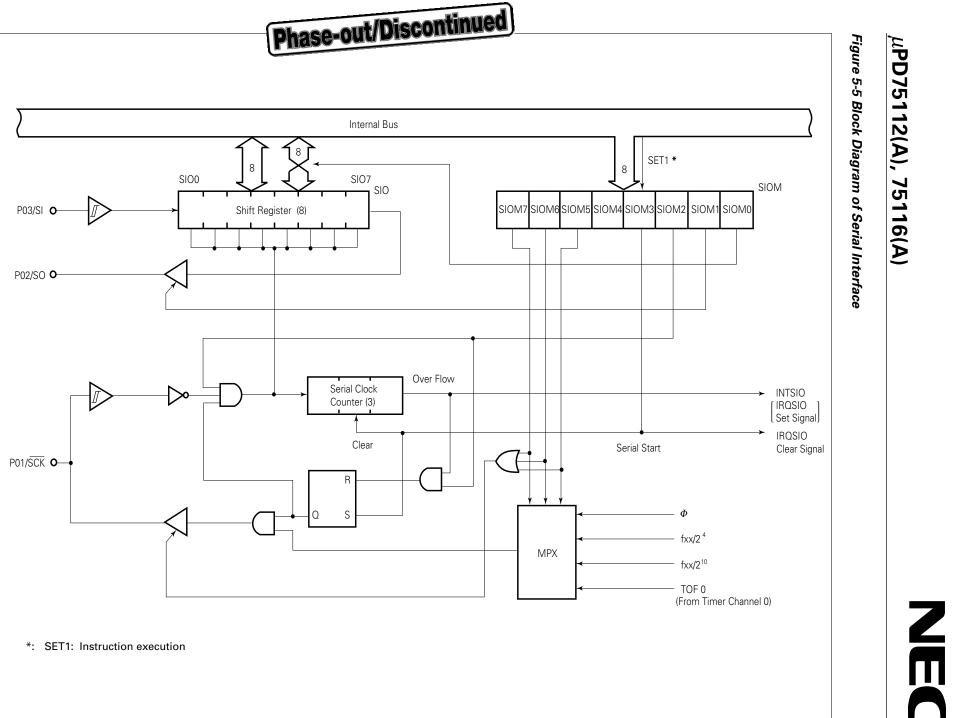

#### 5.6 Serial Interface

The  $\mu$ PD75116(A) incorporates the clock synchronous 8-bit serial interface. The serial interface has the following two modes.

- Operation stop mode

- 3-wire serial I/O mode (MSB/LSB top switching possible)

Connection with the  $\mu$ PD75116(A) and the 75X series, 78K series and various I/O devices is possible in the 3-wire serial I/O mode.

20

µPD75112(A), 75116(A)

## $\mu$ PD75112(A), 75116(A)

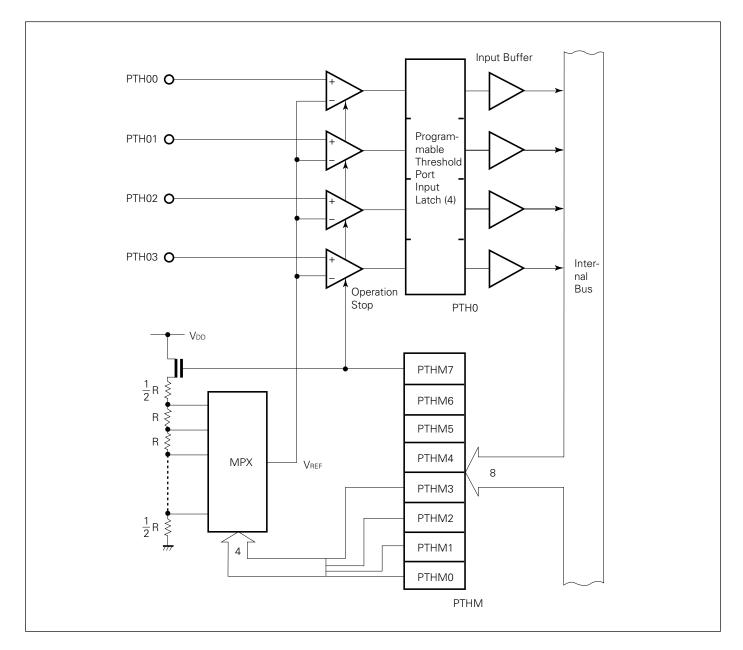

#### 5.7 ProgrammableThreshold Port (Analog Input Port)

The  $\mu$ PD75116(A) is equipped with 4-bit analog input pins (PTH00 to PTH03) capable of changing the threshold voltage. These pins are configured as shown in Figure 5-6.

Sixteen threshold voltage (VREF) values (V<sub>DD</sub>  $\times \frac{0.5}{16}$  -V<sub>DD</sub>  $\times \frac{15.5}{16}$ ) are available and analog signals can be directly input.

The analog input port can also be used as a digital signal input port by selecting  $V_{\text{DD}} \times \frac{7.5}{16}$  for VREF.

#### Figure 5-6 Block Diagram of Programmable Threshold Port

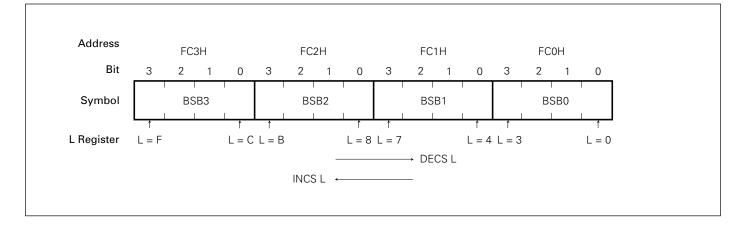

#### 5.8 Bit Sequential Buffer ... 16 bit

The bit sequential buffer is a special data memory for bit control. Since this buffer can easily operate bits by sequentially changing address and bit specifications, it can be conveniently be used for bit-wise processing of data having long bit lengths.

**Remarks:** In pmen. @L addressing, the specified bit moves in accordance with the L register.

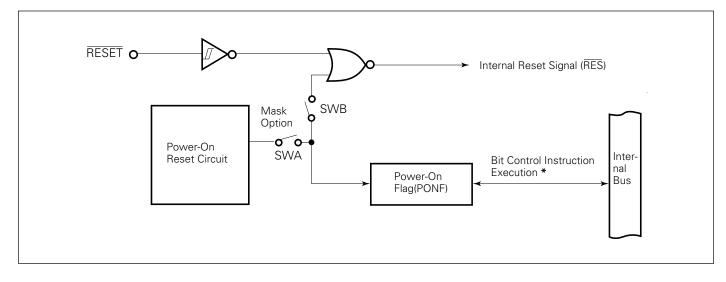

#### 5.9 Power-On Flag (Mask Option)

The power-on flag (PONF) is only set (1) when the power-on reset circuit is activated and the power-on reset signal is generated (see **Figure 8-1**).

PONF is mapped on bit 0 at address FD1H of the data memory space and is manipulated by a bit manipulation instruction

However, it cannot be set(1) by the SET1 instruction.

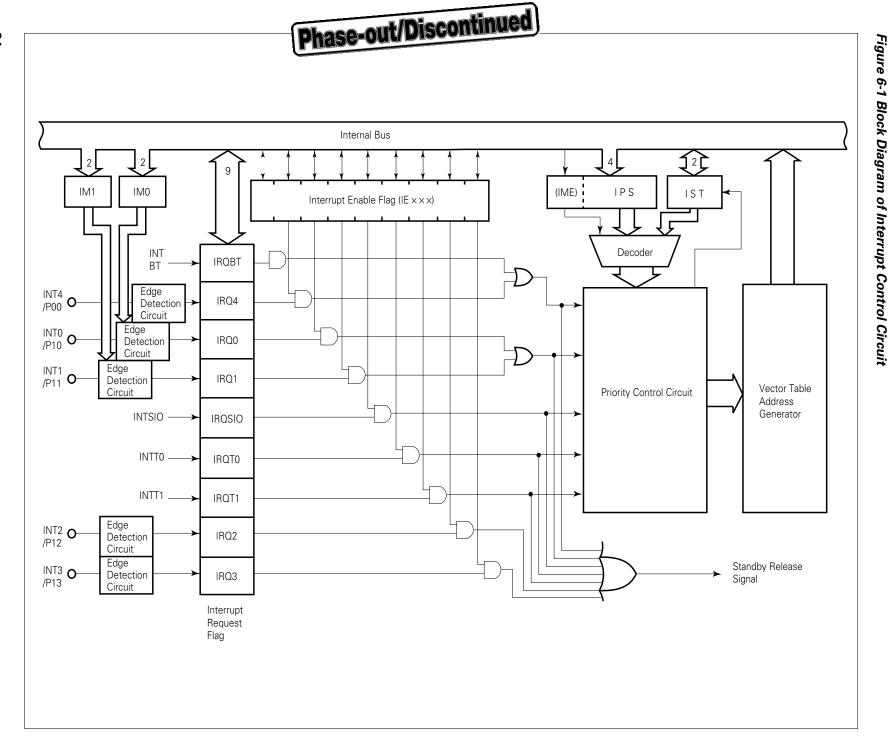

#### 6. Interrupt Functions

There are seven types of interrupt sources for the  $\mu$ PD75116(A) to allow multi-interruption with priority.

The  $\mu$ PD75116(A) is also provided with two types of edge detection testable inputs.

The  $\mu$ PD75116 interrupt control circuit has the following functions;

- Hardware controlled vector interrupt function which enables to control by the interrupt enable flag (IE×××) and the interrupt master enable flag (IME) whether an interrupt should be enabled.

- Interrupt start address can be set freely.

- Multiple interrupt function which enables to specify priority by the interrupt priority select register (IPS).

- Interrupt request flag (IRQ×××) test function (interrupt generation can be checked by the software).

- Standby mode release (the interrupt to be released can be selected by the interrupt enable flag).

# µPD75112(A), 75116(A)

24

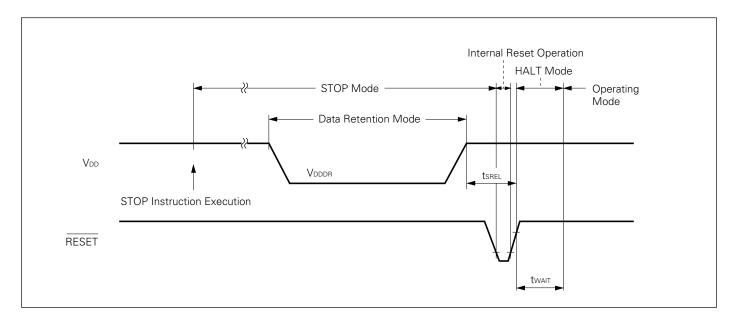

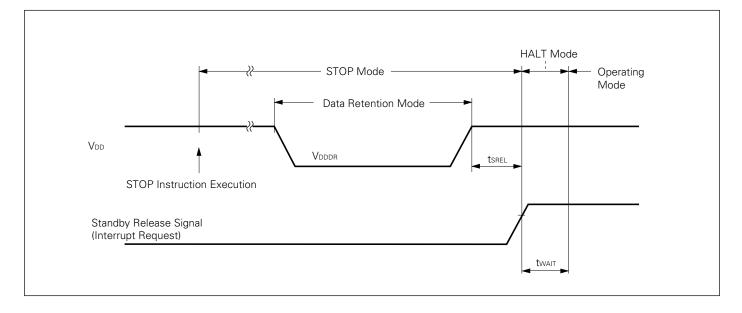

#### 7. Stanby Functions

Two types of standby modes (STOP and HALT modes) are available for the  $\mu$ PD75116(A) to decrease power consumption during standby for program.

#### Table 7-1 Operation Statuses in Standby Mode

|                  |                      | STOP Mode                                                                                                                                                             | HALT Mode                                                                          |

|------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Set instructi    | on                   | STOP instruction                                                                                                                                                      | HALT instruction                                                                   |

| Operation status | Clock generator      | Clock oscillation stop                                                                                                                                                | Only CPU clock $arPhi$ stop                                                        |

| Status           | Basic interval timer | Operation stop                                                                                                                                                        | Operation (IRQBT set at reference time intervals)                                  |

|                  | Serial interface     | Operation enabled only when external SCK<br>input and TO0 clock are set for serial clocks<br>(when timer/event counter 0 is set to external<br>TI0 input) is selected | Operation enabled when aclock other than $arPhi$ is specified for the serial clock |

|                  | Timer/event counter  | Operation enabled only when TIn pin input is specified for the count clock                                                                                            | Operation enabled                                                                  |

|                  | Clock output circuit | Operation stop                                                                                                                                                        | Clock other than CPU clock $arPhi$ enabled for output                              |

|                  | CPU                  | Operation stop                                                                                                                                                        | Operation stop                                                                     |

| Release sig      | nal                  | Interrupt request signal enabled by interrupt enable flag or RESET input                                                                                              |                                                                                    |

## μ**PD75112(A), 75116(A)**

#### 8. Reset Functions

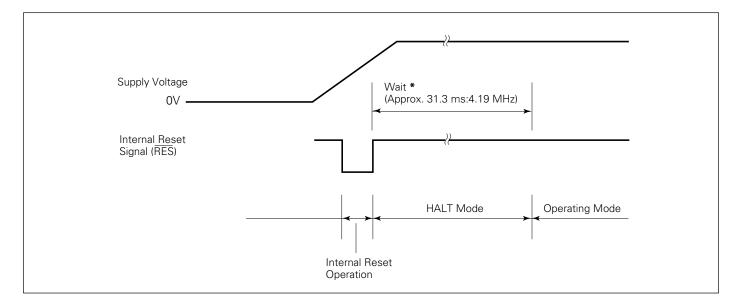

The reset signal (RES) generator is configured as shown in Figure 8-1.

#### Figure 8-1 Reset Signal Generator

\*: PONF setting (1) by SET1 instruction is not possible.

The power-on reset circuit generates the internal reset signal by rising of supply voltage. This pulse is used in the three ways according to the specification of mask option of SWA and SWB shown in Figure 8-1 (refer to "10. Mask Option Selection").

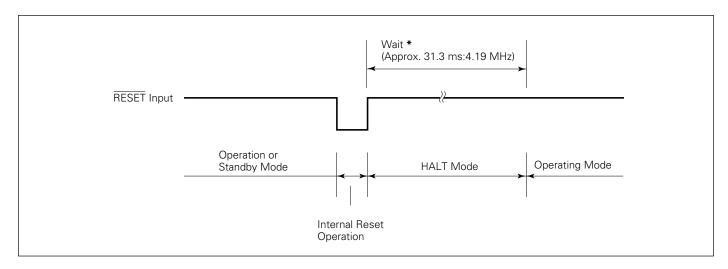

Reset operations are shown in Figures 8-2 and 8-3.

Figure 8-3 Reset Operation by Reset Input

\*: The wait time does not include a time from the generation of RES signal to the start of oscillation.

Each hardware status after reset operation is shown in Table 8-1.

# $\mu$ PD75112(A), 75116(A)

#### Table 8-1 Hardware Statuses after Reset

| Hardware                     |          |                                                   | lware                     | RESET Input in Standby Mode                                                                                                       | RESET Input in Power-On<br>Reset or Operation |

|------------------------------|----------|---------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Program counter (PC)         |          |                                                   |                           | Lower 6 bits of address 0000H of the program memory are set to PC13 to PC8 and the content of address 0001H is set to PC7 to PC0. | same as left                                  |

| PWS Carry flag (CY)          |          | CY)                                               | Hold                      | Undefined                                                                                                                         |                                               |

|                              | Skip fl  | lag (SK                                           | 0 to SK2)                 | 0                                                                                                                                 | 0                                             |

|                              | Interru  | upt stat                                          | tus flag (IST0, 1)        | 0                                                                                                                                 | 0                                             |

|                              | Bank e   | enable                                            | flags (MBE, RBE)          | Bits 6 and 7 of address 0000H of the program memory are set to RBE and MBE, respectively.                                         | same as left                                  |

| Stack poir                   | ter (SP  | ')                                                |                           | Undefined                                                                                                                         | Undefined                                     |

| Data mem                     | ory (RA  | AM)                                               |                           | Hold *1                                                                                                                           | Undefined                                     |

| General re                   | gisters  | (X, A,                                            | H, L, D, E, B, C)         | Hold                                                                                                                              | Undefined                                     |

| Bank selec                   | t regist | ters (M                                           | BS, RBS)                  | 0, 0                                                                                                                              | 0, 0                                          |

| Basic inte                   | erval ti | imer                                              | Counter (BT)              | Undefined                                                                                                                         | Undefined                                     |

|                              |          |                                                   | Mode register (BTM)       | 0                                                                                                                                 | 0                                             |

| Timer/ ev                    | ent      | Cou                                               | nter (Tn)                 | 0                                                                                                                                 | 0                                             |

| counter<br>(n = 0, 1)        |          | Modulo register (TMODn)                           |                           | FFH                                                                                                                               | FFH                                           |

|                              |          | Мос                                               | le register (TMn)         | 0                                                                                                                                 | 0                                             |

|                              |          | TOE                                               | n, TOFn                   | 0, 0                                                                                                                              | 0, 0                                          |

| Serial                       | S        | Shift register (SIO)                              |                           | Hold                                                                                                                              | Undefined                                     |

| interface                    | М        | Mode register (SIOM)                              |                           | 0                                                                                                                                 | 0                                             |

| Clock<br>generator,<br>clock |          | rocesso<br>egister                                | or clock control<br>(PCC) | 0                                                                                                                                 | 0                                             |

| output<br>circuit            |          |                                                   | tput mode<br>(CLOM)       | 0                                                                                                                                 | 0                                             |

| Interrupt                    | In       | iterrupt                                          | t request flag (IRQ×××)   | Reset (0)                                                                                                                         | Reset (0)                                     |

|                              | In       | iterrupt                                          | t enable flag (IE×××)     | 0                                                                                                                                 | 0                                             |

|                              | Pi       | riority s                                         | select resister (IPS)     | 0                                                                                                                                 | 0                                             |

|                              | IN       | JT0, 1 r                                          | node resisters (IM0, IM1) | le resisters (IM0, IM1) 0, 0                                                                                                      |                                               |

| Digital<br>port              | 0        | utput buffer Off                                  |                           | Off                                                                                                                               |                                               |

| μοτι                         | 0        | utput la                                          | atch                      | Clear (0)                                                                                                                         |                                               |

|                              |          | Input/output mode registers<br>(PMGA, PMGB, PMGC) |                           | 0                                                                                                                                 | 0                                             |

| Analog                       | P        | TH00 to                                           | o PTH03 input latches     | Undefined                                                                                                                         | Undefined                                     |

| port                         | М        | lode re                                           | gister (PTHM)             | 0                                                                                                                                 | 0                                             |

| Power-on                     | flag (P0 | ONF)                                              |                           | Hold                                                                                                                              | 1 or undefined <b>*2</b>                      |

| Bit seauer                   | tial but | ffers (B                                          | SB0 to BSB3)              | 0                                                                                                                                 | 0                                             |

# **Phase-out/Discontinued**

### μ**PD75112(A)**, 75116(A)

#### 9. Instruction Set

#### (1) Operand identifier and description method

In the operand column of each instruction, describe the corresponding operand in accordance with the description method for the operand identifier of the instruction (refer to the **"RA75X Assembler Package User's Manual Language Volume" (EEU-730)** for details). If more than one description method is available, select one of them. Capital alphabetic letters, plus and minus signs are key words. Describe them as they are.

In the case of immediate data, describe appropriate numeric values or labels.

Symbols of various registers and flags can be described as labels instead of mem, fmem, pmem, bit, etc. (Refer to the " $\mu$ PD751×× Series User's Manual (IEM-922)" for details). Labels which can be described are limited for fmem and pmem.

| Identifier                      |                                                                                                                | Description Method |  |  |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|

| reg<br>reg1                     | X, A, B, C, D, E, H, L<br>X, B, C, D, E, H, L                                                                  |                    |  |  |  |  |

| rp<br>rp1<br>rp2<br>rp'<br>rp'1 | XA, BC, DE, HL<br>BC, DE, HL<br>BC, DE<br>XA, BC, DE, HL, XA', BC', DE', HL'<br>BC, DE, HL, XA', BC', DE', HL' |                    |  |  |  |  |

| rpa<br>rpa1                     | HL, HL+, HL-, DE, DL<br>DE, DL                                                                                 |                    |  |  |  |  |

| n4<br>n8                        | 4-bit immediate data or label<br>8-bit immediate data or label                                                 |                    |  |  |  |  |

| mem<br>bit                      | 8-bit immediate data or label*<br>2-bit immediate data or label                                                |                    |  |  |  |  |

| fmem<br>pmem                    | FB0H to FBFH and FF0H to FFFH immediate data<br>or labels<br>FC0H to FFFH immediate data or labels             |                    |  |  |  |  |

| addr                            | μPD75112(A) 0000H to 2F7FH immediate data or labels                                                            |                    |  |  |  |  |

|                                 | μPD75116(A) 0000H to 3F7FH immediate data or labels                                                            |                    |  |  |  |  |

| caddr                           | 12-bit immediate data or label                                                                                 |                    |  |  |  |  |

| faddr                           | 11-bit immediate data or label                                                                                 |                    |  |  |  |  |

| taddr                           | 20H to 7FH immediate data (bit = 0) or labels                                                                  |                    |  |  |  |  |

| PORTn<br>IE×××<br>RBn<br>MBn    | PORT0 to PORT9, PORT12 to PORT14<br>IEBT, IESIO, IET0, IET1, IE0 to IE4<br>RB0 to RB3<br>MB0, MB1, MB15        |                    |  |  |  |  |

\*: In the case of 8-bit data processing, only even address can be described for "mem".

$\mu$ PD75112(A), 75116(A) Phase-out/Discontinued

#### (2) Legend in the description of operations

| А     | : | A register; 4-bit accumulator         |

|-------|---|---------------------------------------|

| В     | : | B register                            |

| С     | : | C register                            |

| D     | : | D register                            |

| Е     | : | E register                            |

| Н     | : | H register                            |

| L     | : | L register                            |

| Х     | : | X register                            |

| XA    | : | Register pair (XA); 8-bit accumulator |

| BC    | : | Register pair (BC)                    |

| DE    | : | Register pair (DE)                    |

| HL    | : | Register pair (HL)                    |

| XA'   | : | Extended register pair (XA')          |

| BC'   | : | Extended register pair (BC')          |

| DE'   | : | Extended register pair (DE')          |

| HL′   | : | Extended register pair (HL')          |

| PC    | : | Program counter                       |

| SP    | : | Stack pointer                         |

| CY    | : | Carry flag; bit accumulator           |

| PSW   | : | Program status word                   |

| MBE   | : | Memory bank enable flag               |

| RBE   | : | Register bank enable flag             |

| PORTn | : | Port n (n = 0 to 9, 12 to 14)         |

| IME   | : | Interrupt mask enable flag            |

| IPS   | : | Interrupt priority select register    |

| IE××× | : | Interrupt enable flag                 |

| RBS   | : | Register bank select register         |

| MBS   | : | Memory bank select register           |

| PCC   | : | Processor clock control register      |

|       | : | Address and bit division              |

| (×× ) | : | Content addressed by xx               |

| ××Н   | : | Hexadecimal data                      |

|       |   |                                       |

#### (3) Description of symbols in the addressing area column

|     |                                                                                                                                                                                                                                                                             | 1                                     |  |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|

| *1  | MB=MBE•MBS<br>(MBS=0, 1, 15)                                                                                                                                                                                                                                                |                                       |  |  |

| *2  | MB=0                                                                                                                                                                                                                                                                        |                                       |  |  |

| *3  | MBE=0 : MB=0 (00H-7FH)<br>MB=15 (80H-FFH)<br>MBE=1 : MB=MBS (MBS=0, 1, 15)                                                                                                                                                                                                  | Data Memory<br>Addressing             |  |  |

| *4  | MB=15, fmem=FB0H-FBFH,<br>FF0H=FFFH                                                                                                                                                                                                                                         |                                       |  |  |

| *5  | MB=15, pmem=FC0H-FFFH                                                                                                                                                                                                                                                       |                                       |  |  |

| *6  | addr=0000H-2F7FH (µPD75112(A))<br>=0000H-3F7FH (µPD75116(A))                                                                                                                                                                                                                | A A A A A A A A A A A A A A A A A A A |  |  |

| *7  | addr=(Current PC) -15 to<br>(Current PC) +16                                                                                                                                                                                                                                |                                       |  |  |

| *8  | *8 caddr=0000H-0FFFH (PC13, PC12=00B : μPD75112(A), 116(A)) or<br>=1000H-1FFFH (PC13, PC12=01B : μPD75112(A), 116(A)) or<br>=2000H-2F7FH (PC13, PC12=10B : μPD75112(A)) or<br>=2000H-2FFFH (PC13, PC12=10B : μPD75116(A)) or<br>=3000H-3F7FH (PC13, PC12=11B : μPD75116(A)) |                                       |  |  |

| *9  | faddr=0000H-07FFH                                                                                                                                                                                                                                                           |                                       |  |  |

| *10 | taddr=0020H-007FH                                                                                                                                                                                                                                                           |                                       |  |  |

**Remarks** 1: MB indicates an accessible memory bank.

- 2: In \*2, MB = 0 irrespectively of MBE and MBS.

3: In \*4 and \*5, MB = 15 irrespectively of MBE and MBS.

- 4: **\*6** to **\*10** indicate addressable areas.

- (4) Description of machine cycle column

S indicates the number of machine cycles required for the instruction having skip function to execute skip operation. The value of S varies as follows:

- When no skip ..... S = 0

- When 3-byte instruction (BR !addr, CALL !addr instructions) is skipped ...... S = 2

- Note: GETI instruction is skipped in one-machine cycle.

One machine cycle is equal to one cycle (=tcy)of CPU clock. Three values are available for the one machine cycle by PCC setting.

**Phase-out/Discontinued**

# μ**PD75112(A), 75116(A)**

| Instructions | Mnemonic | Operand         | No. of Bytes | Machine Cycle | Operation                                         | Addressing Area | Skip Condition |

|--------------|----------|-----------------|--------------|---------------|---------------------------------------------------|-----------------|----------------|

| Transfer     | MOV      | A, #n4          | 1            | 1             | A←n4                                              |                 | Stack A        |

|              |          | reg1, #n4       | 2            | 2             | reg1←n4                                           |                 |                |

|              |          | XA, #n8         | 2            | 2             | XA←n8                                             |                 | Stack A        |

|              |          | HL, #n8         | 2            | 2             | HL←n8                                             |                 | Stack B        |

|              |          | rp2, #n8        | 2            | 2             | rp2←n8                                            |                 |                |

|              |          | A, @HL          | 1            | 1             | A←(HL)                                            | *1              |                |

|              |          | A, @HL+         | 1            | 2+S           | A←(HL), then L←L+1                                | *1              | L=0            |

|              |          | A, @HL-         | 1            | 2+S           | A←(HL), then L←L-1                                | *1              | L=FH           |

|              |          | A, @rpa1        | 1            | 1             | A←(rpa1)                                          | *2              |                |

|              |          | XA, @HL         | 2            | 2             | XA←(HL)                                           | *1              |                |

|              |          | @HL, A          | 1            | 1             | (HL)←A                                            | *1              |                |

|              |          | @HL, XA         | 2            | 2             | (HL)←XA                                           | *1              |                |

|              |          | A, mem          | 2            | 2             | A←(mem)                                           | *3              |                |

|              |          | XA, mem         | 2            | 2             | XA←(mem)                                          | *3              |                |

|              |          | mem, A          | 2            | 2             | (mem)←A                                           | *3              |                |

|              |          | mem, XA         | 2            | 2             | (mem)←XA                                          | *3              |                |

|              |          | A, reg          | 2            | 2             | A←reg                                             |                 |                |

|              |          | XA, rp'         | 2            | 2             | XA←rp'                                            |                 |                |