#### **Features**

- Fast Read Access Time 100 ns

- Low Power

35 mA Maximum (Active)

100 uA Maximum (Standby)

- 2-V Data Retention

- Fully Static: No Clock Required

- Three Control Inputs (CE1, CE2, and OE)

- TTL Compatible Inputs and Outputs

- 5 V ± 10% Supply

- 28-Lead Dual In-line and Surface Mount Packages

- JEDEC Pinout

- Commercial and Industrial Temperature Ranges

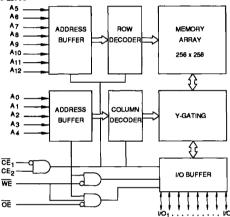

#### **Block Diagram**

#### Description

The AT3864L is a high performance CMOS static Random Access Memory. Its 64K of memory is organized as 8192 words by 8 bits. Manufactured with an advanced CMOS technology, the AT3864L offers access times down to 100 ns with power dissipation of under 200 mW. When the AT3864L is deselected, the standby current is just 100  $\mu$ A. In addition, the AT3864L offers a data retention capability of only 100  $\mu$ W power dissipation when operated on a 2-volt power supply.

The AT3864L powers down to the standby mode when deselected  $(\overline{CE}_1)$  is HIGH or  $\underline{CE}_2$  is LOW). The I/O pins remain in the high impedance state unless the chip is selected  $(\overline{CE}_1)$  is LOW and CE<sub>2</sub> is HIGH), the outputs are enabled  $(\overline{OE})$  is LOW), and Write Enable is not active  $(\overline{WE})$  is HIGH).

The AT3864L is completely TTL compatible and requires a single 5-volt power supply. The device is fully static and does not need any clocks or refresh control signals for operation.

### **Pin Configurations**

|                                    | <del></del>   |

|------------------------------------|---------------|

| Pin Name                           | Function      |

| A0-A12                             | Addresses     |

| I/O <sub>1</sub> -I/O <sub>8</sub> | Outputs       |

| CE <sub>1</sub> , CE <sub>2</sub>  | Chip Enables  |

| ŌĒ                                 | Output Enable |

| WE                                 | Write Enable  |

| Vcc, GND                           | Power, Ground |

| NC                                 | No Connect    |

|                                        | Ţ       |                       | ~ |                                        | L                        |             |

|----------------------------------------|---------|-----------------------|---|----------------------------------------|--------------------------|-------------|

| NC                                     | ч       |                       |   | 28                                     | Ľ                        | VCC         |

| A12                                    | q       | 2                     |   | 2/                                     | Р                        | WE          |

| <b>A</b> 7                             | q       | 3                     |   | 27<br>26                               | P                        | CE2         |

| A6                                     | d       | 4                     |   | 25                                     | Þ                        | AB          |

| A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | <u></u> | 1<br>2<br>3<br>4<br>5 |   | 25<br>24<br>23<br>22<br>21<br>20<br>19 | <del>onananananana</del> | A9          |

| <b>A4</b>                              | þ       | 6<br>7                |   | 23                                     | Þ                        | A11<br>OE   |

| A3                                     | ₫       | 7                     |   | 22                                     | Þ                        | Œ           |

| A2                                     | ₫       | 8                     |   | 21                                     | Þ                        | A10         |

| A1                                     | þ       | 9                     |   | 20                                     | Þ                        | CE1         |

| AO                                     | 덕       | 10                    |   | 19                                     | Þ                        | <b>VO8</b>  |

| 1/01                                   |         | 11                    |   | 18                                     | Þ                        | VO7         |

| VO2                                    | þ       | 12                    |   | 17<br>16<br>15                         | þ                        | <b>I/O6</b> |

| 1/03                                   | þ       | 13                    |   | 16                                     | Þ                        | 1/05        |

| <b>GND</b>                             | þ       | 14                    |   | 15                                     | Þ                        | 1/04        |

|                                        | l       |                       | _ |                                        | 1                        |             |

# 64K (8K x 8) CMOS SRAM

#### **Absolute Maximum Ratings\***

| Temperature Under Bias40° C to 85° C                                                         |

|----------------------------------------------------------------------------------------------|

| Storage Temperature55° C to 125° C                                                           |

| All Input Voltages (including NC Pins) with Respect to Ground0.3 V to V <sub>CC</sub> +0.3 V |

| All Output Voltages with Respect to Ground0.3 V to Vcc+0.3 V                                 |

| Maximum Supply Voltage+7.0 V                                                                 |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Device Operation**

<u>READ</u>: When  $\overline{CE}_1$  is LOW,  $\overline{CE}_2$  is HIGH,  $\overline{OE}$  is LOW, and WE is HIGH, the eight bits of data stored at the memory location determined by the address input (pins A<sub>0</sub> through A<sub>12</sub>) are inserted on the data outputs (pins I/O<sub>1</sub> through I/O<sub>8</sub>).

WRITE: When  $\overline{CE}_1$  is LOW, CE<sub>2</sub> is HIGH, and  $\overline{WE}$  is LOW, the eight bits of data placed on the input pins (I/O<sub>1</sub> through I/O<sub>8</sub>)

are stored at the memory location determined by the address input (pins A<sub>0</sub> through A<sub>12</sub>).

DATA RETENTION: When the chip is in standby mode,  $V_{CC}$  can be reduced to as low as two volts without impacting data integrity. Power dissipation will be reduced to  $100~\mu W$  maximum.

#### **Operating Modes**

| MODE\PIN             | CE <sub>1</sub> | CE <sub>2</sub> | ŌĒ               | WE | I/O    |

|----------------------|-----------------|-----------------|------------------|----|--------|

| Read                 | L               | н               | L                | Н  | Dout   |

| Write                | L               | Н               | X <sup>(1)</sup> | L  | Din    |

| Standby <sub>1</sub> | Н               | ×               | х                | Х  | High Z |

| Standby <sub>2</sub> | X               | L               | x                | Х  | High Z |

| Output Disable       | x               | ×               | Н                | x  | High Z |

Note: 1. X can be L (Low) or H (High)

#### D.C. and A.C. Operating Range

|                    |            | AT3864L-10   | AT3864L-12   | AT3864L-15   |

|--------------------|------------|--------------|--------------|--------------|

| Operating          | Commercial | 0°C - 70°C   | 0°C - 70°C   | 0°C - 70°C   |

| Temperature (Case) | Industrial | -40°C - 85°C | -40°C - 85°C | -40°C - 85°C |

| Vcc Power Supply   |            | 5 V ± 10%    | 5 V± 10%     | 5 V± 10%     |

### **D.C. and Operating Characteristics**

| Symbol | Parameter                 | Conditions                                                                                                                                                                                                                                                                           | Min   | Тур | Max     | Units |

|--------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|---------|-------|

| Iц     | Input Load Current        | VIN = 0 to VCC                                                                                                                                                                                                                                                                       | -1.0  |     | 1.0     | μА    |

| lLO    | Output Leakage<br>Current | $\overline{CE}_1 = 2.2 \text{ V to V}_{CC} + 0.3 \text{ V or}$<br>$\underline{CE}_2 = -0.3 \text{ V to } 0.8 \text{ V or}$<br>$\underline{OE} = 2.2 \text{ V to V}_{CC} + 0.3 \text{ V or}$<br>$\overline{WE} = -0.3 \text{ V to } 0.8 \text{ V}$<br>$V_{I/O} = 0 \text{ to V}_{CC}$ | -1.0  |     | 1.0     | μА    |

| ISB1   | Standby Current<br>(CMOS) | $\begin{array}{l} \underline{CE_2} \leq 0.2 \text{ V or} \\ \overline{CE_1} \geq V_{CC} - 0.2 \text{ V,} \\ CE_2 \geq V_{CC} - 0.2 \text{ V or } CE_2 \leq 0.2 \text{ V} \\ V_{IN} = 0 \text{ to } V_{CC} \end{array}$                                                               |       | 2   | 100     | μА    |

| ISB2   | Standby Current<br>(TTL)  | $\underline{CE}_2 = -0.3 \text{ V to } 0.8 \text{ V or}$<br>$\overline{CE}_1 = 2.2 \text{ V to Vcc} +0.3 \text{ V,}$<br>$\overline{V}_{IN} = 0 \text{ to Vcc}$                                                                                                                       |       |     | 3       | mA    |

| lcc    | Vcc Active Current (TTL)  | $\overline{CE}_1 = -0.3 \text{ V to } 0.8 \text{ V},$ $CE_2 = 2.2 \text{ V to } V_{CC} + 0.3 \text{ V},$ $I_{OUT} = 0 \text{ mA, min cycle}$                                                                                                                                         |       | 20  | 35      | mA    |

| VIL    | Input Low Voltage         |                                                                                                                                                                                                                                                                                      | -0.3  |     | 0.8     | ٧     |

| ViH    | Input High Voltage        |                                                                                                                                                                                                                                                                                      | 2.2 V |     | Vcc+0.3 | V     |

| Vol    | Output Low Voltage        | loL = 2.0 mA                                                                                                                                                                                                                                                                         |       |     | 0.4     | ٧     |

| Voн    | Output High Voltage       | I <sub>OH</sub> = -1.0 mA                                                                                                                                                                                                                                                            | 2.4   |     |         | V     |

# **Pin Capacitance** $(f = 1 \text{ MHz}, T = 25^{\circ}\text{C})^{(1)}$

| Symbol | Parameter                | Conditions | Min | Тур | Max | Units |

|--------|--------------------------|------------|-----|-----|-----|-------|

| Соит   | Input/Output Capacitance | Vout = 0 V |     | 6   | 10  | pF    |

| Cin    | Input Capacitance        | VIN = 0 V  |     | 6   | 10  | pF    |

Note: 1. Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.

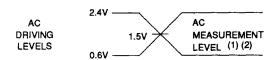

### **Input Test Waveforms and Measurement Levels**

Notes: 1. Input rise and fall time 5 ns.

2. Output load: 1TTL gate + 10 0pF.

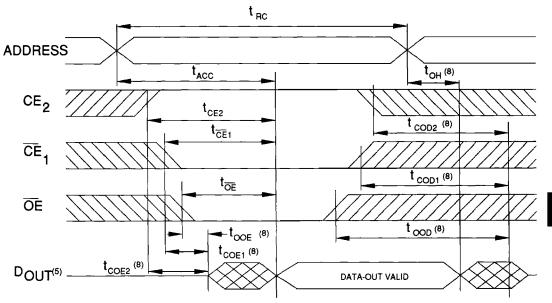

#### A.C. Characteristics for Read

|           |                                                       | AT3864L-10 |          | AT3864L-12 |     | AT3864L-15 |     |       |

|-----------|-------------------------------------------------------|------------|----------|------------|-----|------------|-----|-------|

| Symbol    | Parameter                                             | Min        | Max      | Min        | Max | Min        | Max | UnitS |

| trc       | Read Cycle Time                                       | 100        | •        | 120        |     | 150        |     | ns    |

| tacc      | Address Access Time                                   |            | 100      |            | 120 |            | 150 | ns    |

| tCE1,tCE2 | CE <sub>1</sub> ,CE <sub>2</sub> Access Time          |            | 100      |            | 120 |            | 150 | ns    |

| tOE       | OE Access Time                                        |            | 50       |            | 60  |            | 70  | ns    |

| toн       | Output Hold Time                                      | 15         | <u> </u> | 15         |     | 15         |     | ns    |

| tCOE1,2   | CE <sub>1</sub> , CE <sub>2</sub> Output Enable Time  | 10         |          | 10         |     | 10         |     | ns    |

| tooe      | OE Output Enable Time                                 | 5          |          | 5          |     | 5          |     | ns    |

| tcoD1,2   | CE <sub>1</sub> , CE <sub>2</sub> Output Disable Time | •          | 45       |            | 45  |            | 60  | ns    |

| toop      | OE Output Disable Time                                |            | 40       |            | 40  |            | 50  | ns    |

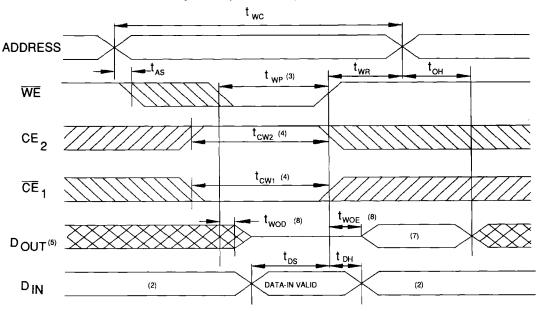

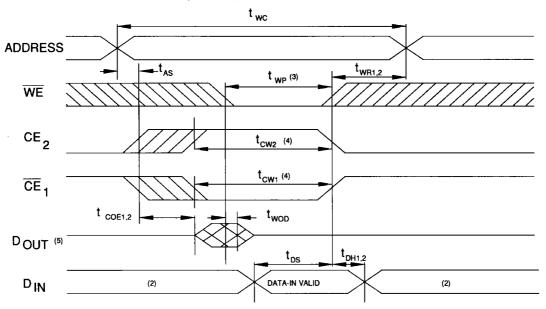

## A.C. Characteristics for Write

|        |                                                       | AT3864L-10 |     | AT3864L-12 |     | AT3864L-15 |     |       |

|--------|-------------------------------------------------------|------------|-----|------------|-----|------------|-----|-------|

| Symbol | Parameter                                             | Min        | Max | Min        | Max | Min        | Max | Units |

| twc    | Write Cycle Time                                      | 100        |     | 120        |     | 150        |     | ns    |

| tas    | Address Setup Time                                    | 0          |     | 0          |     | 0          |     | ns    |

| twp    | Write Pulse Width                                     | 60         |     | 70         |     | 90         |     | ns    |

| tcw1,2 | CE <sub>1</sub> , CE <sub>2</sub> Setup Time          | 80         |     | 80         |     | 90         |     | ns    |

| twn    | Write Recovery Time                                   | 0          |     | 0          |     | 0          |     | ns    |

| twR1,2 | CE <sub>1</sub> , CE <sub>2</sub> Write Recovery Time | 0          |     | 0          |     | 0          |     | ns    |

| tos    | Data Setup Time                                       | 40         |     | 50         |     | 60         |     | ns    |

| tон    | Data Hold Time                                        | 0          |     | 0 0        |     |            | ns  |       |

| tDH1,2 | CE <sub>1</sub> , CE <sub>2</sub> Data Hold Time      | 0          |     | 0          |     | 0          |     | ns    |

| twoE   | WE Output Enable Time                                 | 5          |     | 5          |     | 5          |     | ns    |

| twop   | WE Output Disable Time                                |            | 40  |            | 40  |            | 50  | ns    |

## A.C. Waveforms for Read Cycle (1)

## A.C. Waveforms for Write Cycle 1 (WE Write) (6)

## A.C. Waveforms for Write Cycle 2 (WE Write) (6)

#### Notes:

- 1. During a Read Cycle, WE should be HIGH.

- During this period, I/O pins are in the output state.

A Write occurs when CE<sub>1</sub>, CE<sub>2</sub> and WE are all active at the same time.

A Write begins at the latest transition among  $\overline{CE}_1$  going LOW, CE2 going HIGH and WE going LOW.

A Write ends at the earliest transition among  $\overline{CE}_1$  going HIGH, CE2 going LOW and WE going HIGH.

twp is measured from the beginning of Write to the end of Write.

- 4. t<sub>CW</sub> is measured from the later of  $\overline{CE}_1$  going LOW or CE<sub>2</sub> going HIGH to the end of Write.

- 5. If OE or CE1 is HIGH, or CE2 or WE is LOW, DOUT goes to a HIGH impedance state.

- 6. During a write cycle,  $\overline{OE} = V_{IH}$  or  $V_{IL}$ .

- 7. DOUT is equal to the Input Data written during the same cycle.

- 8. Parameter is sampled and not 100% tested.

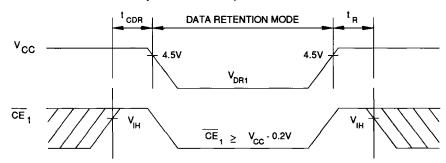

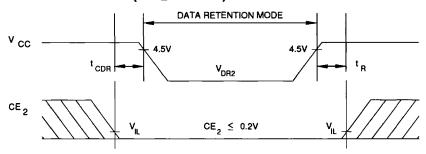

#### **Data Retention Characteristics**

| Parameter                           | Symbol           | Conditions                                                                                                           | Min                | Тур | Max | Units |

|-------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----|-------|

| Data Retention Power Supply Voltage | VDR1             | CE <sub>1</sub> ≥ V <sub>CC</sub> - 0.2 V<br>CE <sub>2</sub> ≥ V <sub>CC</sub> - 0.2 V or<br>CE <sub>2</sub> ≤ 0.2 V | 2.0                |     | 5.5 | V     |

|                                     | V <sub>DR2</sub> | CE <sub>2</sub> ≤ 0.2 V                                                                                              | 2.0                |     | 5.5 |       |

| Data Retention<br>Current           | ICCDR1           | $\frac{V_{CC}}{CE_1}$ ≥ $V_{CC}$ = 0.2 V<br>$CE_2$ ≥ $V_{CC}$ - 0.2 V or<br>$CE_2$ ≤ 0.2 V                           |                    | 1   | 50  | μΑ    |

|                                     | ICCDR2           | $V_{CC} = 3.0 \text{ V},$<br>$CE_2 \le 0.2 \text{ V}$                                                                |                    | 1   | 50  | μА    |

| Chip Enable Setup Time              | todr             |                                                                                                                      | 0                  |     |     | ns    |

| Chip Enable Hold Time               | tR               |                                                                                                                      | tRC <sup>(1)</sup> |     |     | ns    |

Note: 1. t<sub>RC</sub> = Read Cycle Time

## Data Retention Waveform 1 (CE<sub>1</sub> Control)

### Data Retention Waveform 2 (CE 2 Control)

# **Ordering Information**

| tacc | lcc    | Icc (mA) | Ordovina Osala               |             |                              |

|------|--------|----------|------------------------------|-------------|------------------------------|

| (ns) | Active | Standby  | Ordering Code                | Package     | Operation Range              |

| 100  | 35 0.1 |          | AT3864L-10PC<br>AT3864L-10RC | 28P6<br>28R | Commercial<br>(0° to 70°C)   |

|      |        |          | AT3864L-10PI<br>AT3864L-10RI | 28P6<br>28R | Industrial<br>(-40° to 85°C) |

| 120  | 35     | 0.1      | AT3864L-12PC<br>AT3864L-12RC | 28P6<br>28R | Commercial<br>(0° to 70°C)   |

|      |        |          | AT3864L-12PI<br>AT3864L-12RI | 28P6<br>28R | Industrial<br>(-40° to 85°C) |

| 150  | 35     | 0.1      | AT3864L-15PC<br>AT3864L-15RC | 28P6<br>28R | Commercial<br>(0° to 70°C)   |

|      |        |          | AT3864L-15PI<br>AT3864L-15RI | 28P6<br>28R | Industrial<br>(-40° to 85°C) |

| Package Type |                                                             |  |  |  |  |

|--------------|-------------------------------------------------------------|--|--|--|--|

| 28P6         | 28 Lead, 0.600" Wide, Plastic Dual Inline Package (PDIP)    |  |  |  |  |

| 28R          | 28 Lead, 0.330" Wide Plastic Gull Wing Small Outline (SOIC) |  |  |  |  |