## MN1237A, MN1237AD

## CMOS LSIs for CRT Interface

#### Outline

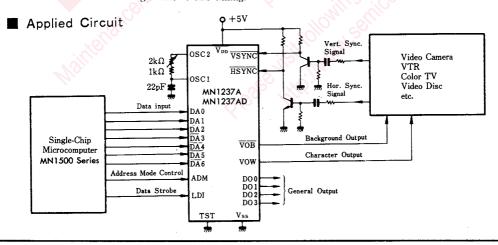

The MN1237A and MN1237AD are high-performance CMOS LSIs for highly efficient CRT interface, which can display times, channels, programs, etc. up to 60 characters(12 characters×5Lines) on the CRT screens of video equipment such as video cameras, color TV sets, VTRs, video disks, etc., using alphabets, numerals, symbols, etc.

#### Features

- Displays up to 60 characters(12 characters × 5 lines).

- 44 Kinds of characters(5×7 dots) (with rounding function); A-Z, 0-9, ., :, •, -, ?, (background), (blank)

- Black background to display characters clearly

- Character size selectable out of 4 types, depending on programs.

- Display position selectable out of 57 horizontal directions and 64 vertical direction, depending on programs.

- Available for various controls because 4-bit general purpose output latches are porvided.

- +5V single power supply

- CMOS process

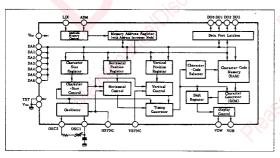

## ■ Block Diagam

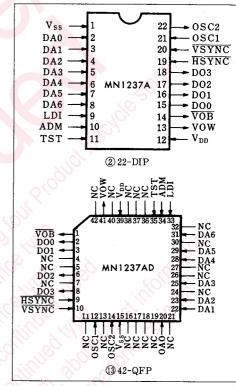

#### Pin Configuration

## ■ Absolute Maximum Ratings(V<sub>ss</sub>=0 V, Ta=25°C)

| Item                          | Symbol            | Rating                   | Unit |

|-------------------------------|-------------------|--------------------------|------|

| Supply voltage                | $V_{\mathrm{DD}}$ | -0.3~+8                  | V    |

| Input voltage                 | VI                | $-0.3 \sim V_{DD} + 0.3$ | V    |

| Output voltage                | Vo                | $-0.3 \sim V_{DD} + 0.3$ | V    |

| Power Dissipation             | Pp                | 100                      | mW   |

| Operating ambient temperature | Topr              | -20~+70                  | °C   |

| Storage temperature           | $T_{ m stg}$      | $-50 \sim +120$          | °C   |

## ■ Operating Conditions(Ta=25°C)

| Item                       | Symbol | Condition                                          | min. | typ. | max. | Unit |

|----------------------------|--------|----------------------------------------------------|------|------|------|------|

| Supply voltage             | VDD    | $V_{SS} = 0V$                                      | 4.5  | 5    | 5.5  | V    |

| Self-oscillation           |        |                                                    |      | 10   |      |      |

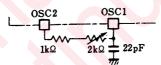

| Self-oscillation frequency | fosc   | $R=1\sim 3k\Omega$ , $R_{fix}=1k\Omega$ , $C=22pF$ | 4.5  | 5    | 5.5  | MHz  |

\*1 Recommended self-oscillator circuit

## ■ Electrical Characteristics (V<sub>DD</sub>=5 V±5%, V<sub>SS</sub>=0 V, Ta=0 to +70°C)

#### • DC Characteristics

| V <sub>DD</sub> =5V, Output terminal open | 8                                                                | 5                                                                     | · 8<br>40                                                              | mA<br>mW                                              |

|-------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|

|                                           | ۷                                                                |                                                                       | 40                                                                     | mW                                                    |

|                                           | 0.                                                               | 1/ //                                                                 |                                                                        |                                                       |

|                                           |                                                                  |                                                                       | :00                                                                    |                                                       |

|                                           | 3                                                                |                                                                       | 0.,,                                                                   | V                                                     |

| $V_{DD} = 5V$                             | 11/10                                                            |                                                                       | 0.8                                                                    | V                                                     |

| $V_{\rm I} = V_{\rm DD}$                  | 0,                                                               | 0///                                                                  | 30                                                                     | μΑ                                                    |

| by the for the s                          |                                                                  |                                                                       |                                                                        |                                                       |

| V -5V                                     | 3                                                                |                                                                       |                                                                        | V                                                     |

| ADD=2A                                    |                                                                  |                                                                       | 0.8                                                                    | V                                                     |

| $V_{I} = V_{DD}$                          |                                                                  |                                                                       | 30                                                                     | $\mu$ A                                               |

| 110, 611                                  |                                                                  |                                                                       |                                                                        |                                                       |

| $V_{DD} = 5V$ , $I_{OH} = 300 \mu A$      | 3.2                                                              |                                                                       |                                                                        | V                                                     |

| $V_{DD} = 5V$ , $I_{OL} = 2mA$            |                                                                  |                                                                       | 0.5                                                                    | V                                                     |

|                                           | $V_{DD} = 5V$ $V_{I} = V_{DD}$ $V_{DD} = 5V, I_{OH} = 300 \mu A$ | $V_{DD} = 5V$ 3 $V_{I} = V_{DD}$ $V_{DD} = 5V, I_{OH} = 300\mu A$ 3.2 | $V_{DD} = 5V$ 3 $V_{I} = V_{DD}$ $V_{DD} = 5V, I_{OH} = 300 \mu A$ 3.2 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

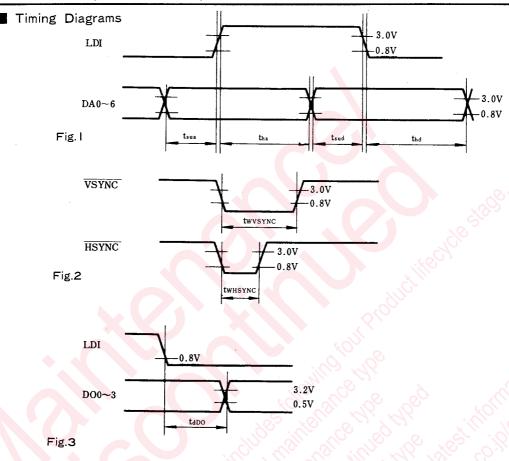

#### ● AC Characteristics

| Item                    | Symbol  | Condition                             | min. | typ. | max. | Unit | Note   |  |

|-------------------------|---------|---------------------------------------|------|------|------|------|--------|--|

| Address setup time      | tsua    | $V_{DD} = 5.0 V$                      | 4    |      |      | μs   |        |  |

| Address hold time       | tha     | $V_{IH} = 4.0 V$<br>$V_{II} = 0.8 V$  | 7    |      |      | μs   | Fig.1  |  |

| Data setup time         | tud     | $V_{IL} = 0.8 V$<br>$V_{IHS} = 4.0 V$ | 4    |      |      | μs   | rig.i  |  |

| Data hold time          | thd     | $V_{\rm ILS} = 0.8V$                  | 8    |      |      | μs   |        |  |

| VSYNC pulse width       | twvsync | 77 - 077                              | 6    |      |      | μs   | Fig.2  |  |

| HSYNC pulse width       | twhsync | $V_{DD} = 5.0V$                       | 3    |      |      | μs   | 1.1g.2 |  |

| DOO-3 output delay time | tado    | $V_{DD} = 5.0 \text{V}$               | 5    |      |      | μs   | Fig.3  |  |

## Pins Description

| Symbol            | Pin                               | Description                                                                               |

|-------------------|-----------------------------------|-------------------------------------------------------------------------------------------|

| $V_{\mathrm{DD}}$ | V <sub>DD</sub> power supply      | Connects to the V <sub>DD</sub> supply voltage(+5V).                                      |

| $V_{SS}$          | Vss power supply                  | Connects to the Vss supply voltage (0V).                                                  |

| OSC1~2            | Self-oscillation pin              | Pins to connect: C and R for determining a self-oscillation frequency.                    |

| TST               | Test input                        | Set to the "L" level in other cases than chip test.                                       |

| VSYNC             | Vert. sync. pulse input           | Pin to input a TV vertical sync. A sync. signal is active at the "L" level.               |

| HSYNC             | Hor. sync pulse input             | Pin to input a horizontal sync. signal. A sync. signal is active at the "L" level.        |

| DA0~6             | Data bus input                    | 7-bit data input pin. Active at the "H" level                                             |

| ADM               | Address mode select input         | Input pin for a signal which selects an address setting mode.                             |

| LDI               | Strobe pulse input                | Input pin for a strobe signal which latches an address and data                           |

| VOW               | Video signal output(W)            | Video signal output pin. A white signal is outputted at the "H" level.(character output)  |

| VOB               | Video signal output(B)            | Video signal output pin. A black signal is outputted at the "L" level.(background output) |

| DO0~3             | Output with general purpose latch | 4-bit general purpose output pin                                                          |

#### ■ Description of Operation

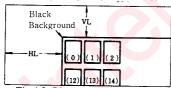

#### 1. Screen Configuration

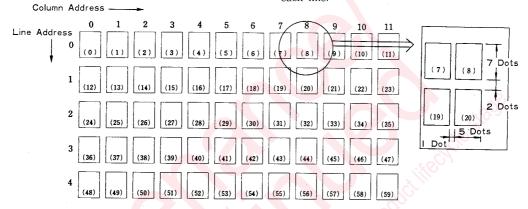

The MN1237A and MN1237AD can display up to 60 characters; 12 characters per line  $\times$ 5 lines. Each

character has a  $5 \times 7$  dot matrix. There is a 1-dot space between each character, and a 2-dot space between each line.

Note Numerals O through 59 in frames indicate display memory addresses.

Fig.4 Relations between Screen Configuration and Display Memory Addresses

#### 2. Memory Configuration

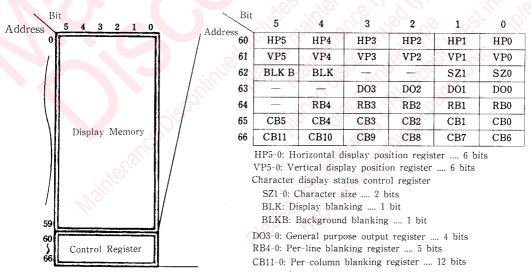

A memory address consists of 7 bits. Addresses 0(0000000) through 59(0111011) are display data memory. Fig.4 shows its relations with the screen.

Addresses 60(0111100) through 66(1000010) are display control register. Fig.5 shows a memory map.

Fig.5 Memory Map

(Supplement: Differences between MN1237 and MN1227)

Address

The MN1237 is a pin compatible CMOS LSI with the MN1227. As it uses a precharge system at RAM write/read time along with a CMOS-oriented trend, precharge may affect read RAM data under the following circumstances. In writing a character code at the RAM address "n", display data may be affected by precharge when displaying the data of the same address, within a period of 3µs from a rise edge of the LDI signal.

### 3. Character Codes and Their Patterns

The MN1237A/MN1237AD incorporates a 5×7-dot ROM type character generator. Each character corresponds to the codes shown in Table 1.

Table I Character Codes List

| , 45                               |       |   |            |

|------------------------------------|-------|---|------------|

| Upper<br>2 Bits<br>Lower<br>4 Bits | 0     | 1 | 2          |

| 0                                  | A     | N | . 0        |

| 1                                  | В     | 0 | 1          |

| 2                                  | С     | P | 2          |

| 3                                  | D     | Q | 3          |

| 4                                  | E     | R | 4          |

| 5                                  | F     | S | 5          |

| 6                                  | G     | T | 6          |

| 7                                  | Н     | U | 7          |

| 8                                  | I     | V | 8          |

| 9                                  | J     | W | 9          |

| 10                                 | K     | X |            |

| 11                                 | L     | Y | • (Period) |

| 12                                 | M     | Z | <u> </u>   |

| 13                                 | (Dot) | ? |            |

| 14                                 |       |   |            |

| 15                                 | L     |   |            |

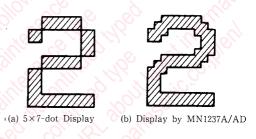

Fig.6 shows character patterns registered in the ROM. Fig.8 Horizontal Display Position Register Since the MN1237A/MN1237AD has a rounding This register specifies a display start position in the function, corners of each characters are rounded to display characters more naturally, compared with a general 5×7-dot display.

#### 4. Display Memory Configuration

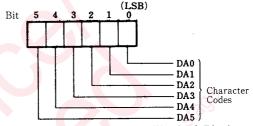

The display memory is a  $60 \times 6$ -bits RAM. Bits 5-0 specify character codes. Fig.7 shows a configuration of one word of the display memory. Character codes are shown in Table 1.

Fig.7 Configuration of One Word of Display

#### Memory 5. Control Registers

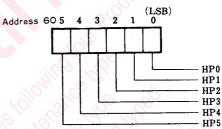

(I) Horizontal display position register (HP5-0)

horizontal direction on the CRT. HP5-0 are not allowed to be(000000) through(000110).

For a horizontal display start position, see Fig.10.

ABCDEFGHI (2) Vertical display position register(VP5-0) Address 61 5 PORS Υ 3456789

Fig.6 Character Types

(Character patterns registered in ROM: 44 types, 1 vertical direction on the CRT screen. character:  $5 \times 7$  dots)

# VP0 VP4 VP5

Fig.9 Vertical display Position Register

This register specifies a display start position in the

For a vertical display start position, see Fig.10.

#### [Horizontal and Vertical Disply Start Positions]

Horizontal and vertical display start positions on the CRT screen are specified by specifying a black background display position in accordance with values of HP5-0 and those of VP5-0. (See Fig. 10) Assuming that the horizontal and vertical display start positions are HL and VL, respectively, they can be obtained by the following formulas, where an oscillation cycle is t (s) and H is one cycle of a horizontal sync. signal when an oscillation frequency is fosc (Hz).

$HL = t \times \{4(HP5 \times 2^5 + HP4 \times 2^4 + HP3 \times 2^3 + HP2 \times 2^2\}$

$+ HP1 \times 2 + HPO) + A$

$VL = H \times 4(VP5 \times 2^5 + VP4 \times 2^4 + VP3 \times 2^3 + VP2 \times 2^2$

$+VP1\times2+VPO$

Note) The value of A changes as shown in Table 2. depending on character sizes(SZ1 0).

t=1/fosc: Oscillation frequency(5 MHz typ.)

H: Horizontal sync. signal cycle(63.5 µs typ.)

Fig. 10 Display Start Position Table 2 Relations between Character Size(SZI O) and A

| - |     |     |    |

|---|-----|-----|----|

|   | SZ1 | SZ0 | A  |

|   | 0   | 0   | 8  |

|   | 0 . | 1   | 10 |

|   | 1   | 0   | 11 |

|   | 1   | 1   | 12 |

|   |     |     |    |

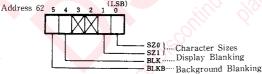

#### (3) Character display status control register

Fig. I I Character Display State Control Register ① Character size(SZI-O)

SZ1 and SZ0 are bits to specify a character size. One of four types of character sizes shown in Table 3 can be selected depending on data in SZ1-SZ0.

| ŀ |       |     | vs a 5×7               | dot matrix                 | configuration.  |

|---|-------|-----|------------------------|----------------------------|-----------------|

|   | Table | e 3 |                        |                            | Hor.<br>5 Dots  |

|   | Со    | de  | Character Siz<br>H: He | ze(1-dot Size)<br>or. Line |                 |

|   | SZ1   | SZ0 | Vert.                  | Hor.                       | <b>H</b>        |

|   | 0     | 0   | 14H (2H)               | $2\mu s(0.4\mu s)$         | Vert.<br>7 Dots |

|   | 0     | 1   | 28H (4H)               | $4\mu s(0.8\mu s)$         | H+++++          |

|   | 1     | 0   | 42H (6H)               | $6\mu s(1.2\mu s)$         |                 |

|   | 1     | 1   | 56H (8H)               | $8\mu s(1.6\mu s)$         | Fig. 12         |

Notes) • H means a horizontal line;  $H = 63.5(\mu s)$ .

· Values in the Hor. column are when the oscillation frequency fosc is 5 MHz.

#### ② Display blanking(BLK)

This bit specifies a display screen state. When BLK is "1", all the display is suppressed regardless of other date. To display, it is necessary to reset BLK to "0". The BLK status is indefinite when power is turned

#### 3 Background blanking(BLKB)

This bit specifies a background display state. When BLKB is "1", background output(VOB) is suppressed regardless of other data. To display the background, it is necessary to reset BLKB to "0". The BLKB status is indefinite when power is turned on.

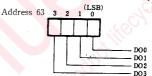

## (4) General purpose register(DO3-0)

Fig. 13 General Purpose Output Register

This is an output with 4-bits latch, and data written in DO3-0 is outputted to output pins(DO3-DO0).

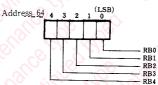

#### (5) Per-line blanking register(RB4-0)

Fig. I 4 Per-line Blanking Register

These bits specify a per-line display state. If one of RB0-RB4 is set to "1", a display of the line corresponding to that bit is suppressed.

When displaying a line, therefore, it is necessary to reset the bit corresponding to that line to "0". The status of RB0-4 is indefinite when power is turned

## (6) Per-column blanking register(CBII-0)

Fig. 15 Per-column Blanking Register

These bits specify a per-column display state. If one of CB0-11 is set to "1", a display of the column corresponding to that bit is suppressed. When displaying a column, therefore, it is necessary to reset the bit corresponding to that column to "0". The status of CB0-11 is indefinite when power is turned on.

#### 6. Data Write

The MN1237A/MN1237AD has two modes for writing data in the memory.

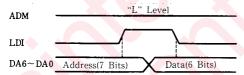

#### 1 Direct address mode

This mode is set when ADM is at the "L" level. When a signal inputted to the LDI terminal changes from "L" to "H", the 7-bit data of DA6-DA0 is latched to the memory address register. When a signal at the LDI terminal changes from "H" to "L", the 6-bit data of DA5-DA0 is written in the memory at the address specified by the memory address register. Fig.16 shows this timing.

Fig. 16 Direct Address Mode Timing

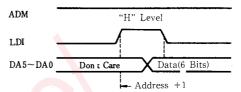

#### (2) Address increment mode

This mode is set when ADM is at the "H" level. When a signal inputted to the LDI terminal changes from "L" to "H", the data already latched in the memory address register is incremented. When a signal at the LDI terminal changes from "H" to "L", the 6-bit data of DA5-DA0 is written in the memory at the address specified by the memory address register which was incremented. Fig.17 shows this timing.

Fig. 17 Address Increment Mode Timing

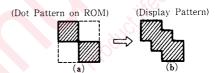

#### 7. Rounding Function

When a character pattern on the ROM is as shown in Fig.18, the rounding function automatically adds 1 dot in the middle of opposite angles to display it. This function allows more natural display than general 5×7-dot display.

Fig. 18 Rounding Function

Fig. 19 Display Example

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- · Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20080805