# P2732A 32K (4K x 8) PRODUCTION EPROM

- 200 ns (P2732A-2) Maximum Access Time . . . HMOS\*-E Technology

- Compatible with High-Speed 8 MHz iAPX 186 . . . Zero WAIT State

- **Two Line Control**

- Compatible with 12 MHz 8051 Family

- Industry Standard Pinout . . . JEDEC Approved

- Low Active Current . . . 100 mA Max.

- inteligent Identifier™ Mode

- Fast 20 ms Programming Time

- TTL Compatible

The Intel P2732A is a 5V-only, Electrically Programmable Read-Only Memory in a plastic package. One time programmable, it has been designed for high volume production environments where a programmable memory is required for flexibility. The standard P2732A access time is 250 ns with speed selection (P2732A-2) available at 200 ns. The access time is compatible with high performance microprocessors such as the 8 MHz iAPX 186. In these systems, the P2732A allows the microprocessor to operate without the addition of WAIT states.

The P2732A is ideal for volume production environments where inventory and lead time risks occur for program codes. Inventoried in the unprogrammed state, the P2732A is programmed quickly and efficiently when the need to change code arises. Costs incurred for new ROM masks or obsoleted ROM inventories are avoided. The tight package dimensional controls, inherent non-erasability, and high reliability of the P2732A make it the ideal component for these production applications.

Using Intel's HMOS\*-E technology, low power consumption combined with high speed data access are achieved. The maximum P2732A active current is 100 mA, while standby is only 35mA. The standby mode is selected by applying a TTL-high signal to the  $\overline{\text{CE}}$  input.

#### PIN NAMES

| A <sub>0</sub> -A <sub>11</sub> | ADDRESSES         |

|---------------------------------|-------------------|

| ĈĒ                              | CHIP ENABLE       |

| OE/V <sub>PP</sub>              | OUTPUT ENABLE/VPP |

| 00-07                           | OUTPUTS           |

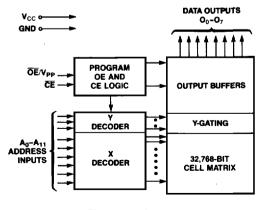

Figure 1. Block Diagram

Figure 2. Pin Configuration

<sup>\*</sup>HMOS is a patented process of Intel Corporation.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias10°C to +80°C                   |

|-------------------------------------------------------|

| Storage Temperature65°C to +125°C                     |

| All Input or Output Voltages with                     |

| Respect to Ground +6V to -0.3V                        |

| Voltage on Pin 22 with Respect                        |

| to Ground +13.5V to −0.3V                             |

| V <sub>PP</sub> Supply Voltage with Respect to Ground |

| During Programming +22V to −0.3V                      |

\*NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### D.C. AND A.C. OPERATING CONDITIONS DURING READ

|                                             | P2732A/A-2/A-3/A-4 |

|---------------------------------------------|--------------------|

| Operating Temperature Range                 | 0°C−70°C           |

| V <sub>CC</sub> Power Supply <sup>1,2</sup> | 5V ± 5%            |

### **READ OPERATION**

## D.C. CHARACTERISTICS

| Cumbal                        | Parameter                         |      | Limits  |                     |       | Conditions                |  |

|-------------------------------|-----------------------------------|------|---------|---------------------|-------|---------------------------|--|

| Symbol                        | Parameter                         | Min. | Typ.[1] | Max.                | Units |                           |  |

| I <sub>IL</sub>               | Input Load Current                |      |         | 10                  | μА    | V <sub>IN</sub> = 5.5V    |  |

| ILO                           | Output Leakage Current            |      |         | 10                  | μΑ    | V <sub>OUT</sub> = 5.5V   |  |

| l <sub>CC1</sub> <sup>2</sup> | V <sub>CC</sub> Current (Standby) |      | 15      | 35                  | mA    | CE = VIH, OE = VIL        |  |

| l <sub>c:c2</sub> 2           | V <sub>CC</sub> Current (Active)  | ·    | 60      | 100                 | mA    | OE = CE = VIL             |  |

| V <sub>IL</sub>               | Input Low Voltage                 | -0.1 |         | 0.8                 | ٧     |                           |  |

| V <sub>IH</sub>               | Input High Voltage                | 2.0  |         | V <sub>CC</sub> + 1 | ٧     |                           |  |

| V <sub>OL</sub>               | Output Low Voltage                |      |         | 0.45                | ٧     | I <sub>OL</sub> = 2.1 mA  |  |

| V <sub>OH</sub>               | Output High Voltage               | 2.4  |         |                     | ٧     | l <sub>OH</sub> = -400 μA |  |

| V <sub>PP</sub> <sup>2</sup>  | V <sub>PP</sub> Read Voltage      | 3.8  |         | V <sub>CC</sub>     | v     | $V_{CC} = 5.0V \pm 0.25V$ |  |

#### A.C. CHARACTERISTICS

|                     |                                                                     | P273 | 2A-2 | P27  | '32A | P27: | 32A-3 | P27: | 32 <b>A</b> -4 |       | Test<br>Conditions†       |  |

|---------------------|---------------------------------------------------------------------|------|------|------|------|------|-------|------|----------------|-------|---------------------------|--|

| Symbol              | Parameter                                                           | Min. | Max. | Min. | Max. | Min. | Max.  | Min. | Max.           | Units |                           |  |

| t <sub>ACC</sub>    | Address to Output Delay                                             |      | 200  |      | 250  |      | 300   |      | 450            | ns    | CE = OE = VIL             |  |

| t <sub>CE</sub>     | CE to Output Delay                                                  |      | 200  |      | 250  |      | 300   |      | 450            | ns    | OE = VIL                  |  |

| t <sub>OE</sub>     | OE to Output Delay                                                  |      | 70   |      | 100  |      | 150   |      | 150            | ns    | CE = VIL                  |  |

| t <sub>DF</sub> [4] | OE High to Output Float                                             | 0    | 60   | 0    | 60   | 0    | 105   | 0    | 130            | ns    | CE = VIL                  |  |

| t <sub>OH</sub>     | Output Hold from Addresses,<br>CE or OE Whichever Occurred<br>First | 0    |      | 0    |      | 0    |       | 0    |                | ns    | CE = OE = V <sub>IL</sub> |  |

#### **†A.C. TEST CONDITIONS**

| Output Load 1 TTL gate and $C_L = 100 \text{ pF}$ |

|---------------------------------------------------|

| Input Rise and Fall Times ≤20 ns                  |

| Input Pulse Levels 0.45V to 2.4V                  |

Timing Measurement Reference Level:

|         |   | _ | _ | <br>_ |  |      | - | - | _ | _ |  | - | -   |     |      |

|---------|---|---|---|-------|--|------|---|---|---|---|--|---|-----|-----|------|

| Inputs  |   |   |   |       |  | <br> |   |   |   |   |  |   | 0.8 | and | 2.0V |

| Outputs | _ |   |   |       |  |      |   |   |   |   |  |   | 0.8 | and | 2 0V |

#### NOTES:

- 1. Typical values are for  $T_A = 25$  °C and nominal supply voltages.

- This parameter is only sampled and is not 100% tested. Output float is defined as the point where data is no longer driven see timing diagram on page 4-18

- 3. OE may be delayed up to tACC-toE after the falling edge of CE without impacting tACC.

- When programming the 2732A, a 0.1µF capacitor is required across OE/Vpp and ground to suppress spurious voltage transients which may damage the device.

4-25

# **CAPACITANCE**<sup>[2]</sup> $(T_A = 25^{\circ}C, F = 1 \text{ MHz})$

| Symbol           | Parameter                                      | Тур. | Max. | Unit | Conditions            |

|------------------|------------------------------------------------|------|------|------|-----------------------|

| C <sub>IN1</sub> | Input Capacitance<br>Except OE/V <sub>PP</sub> | 4    | 6    | pF   | V <sub>IN</sub> =0V   |

| C <sub>IN2</sub> | OE/V <sub>PP</sub> Input<br>Capacitance        | •    | 20   | pF   | V <sub>IN</sub> = 0V  |

| C <sub>OUT</sub> | Output Capacitance                             | 8    | 12   | pF   | V <sub>OUT</sub> = 0V |

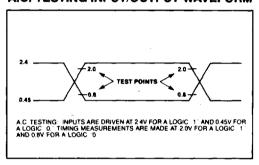

# A.C. TESTING INPUT/OUTPUT WAVEFORM

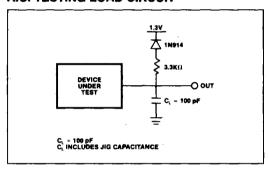

# A.C. TESTING LOAD CIRCUIT

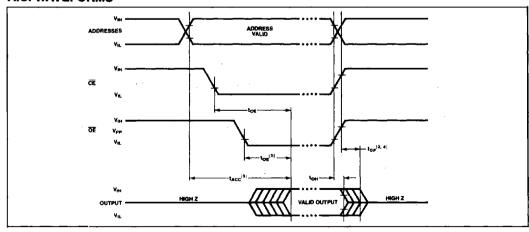

### A.C. WAVEFORMS

- 1. Typical values are for  $T_A = 25^{\circ}C$  and nominal supply voltages.

- 2. This parameter is only sampled and is not 100% tested. Output float is defined as the point where data is no longer driven—see timing diagram on this page.

- ΘE may be delayed up to t<sub>ACC</sub>—t<sub>OE</sub> after the falling edge of <del>CE</del> without impacting t<sub>ACC</sub>.

When programming the P2732A, a 0.1μF capacitor is required across <del>OE</del>/V<sub>PP</sub> and ground to suppress spurious voltage transients which may damage the device.

#### APPLICATIONS INFORMATION

Intel's P2732A is the result of a multi-year effort to make EPROMs more cost effective for production applications. The benefits of a plastic package enable the P2732A to be used for high volume production with lower profile boards and easier production assembly (no cover over UV transparent windows).

The reliability of plastic EPROMs is equivalent to traditional CERDIP packaging. The plastic is rugged and durable making it optimal for auto insertion and auto handling equipment. Design and testing ensures device programmability, data integrity, and impermeability to moisture.

Inte's Plastic EPROMs are designed for total compatibility with their CERDIP packaged predecessors. This encompasses quality, reliability, and programming. All Intel Plastic EPROMs have passed Intel's strict process and product reliability qualifications.

#### **DEVICE OPERATION**

The six modes of operation of the P2732A are listed in Table 1. A single 5V power supply is required in the read mode. All inputs are TTL levels except for OE/V<sub>PP</sub> during programming and 12V on A<sub>9</sub> for the intelligent Identifier™ mode. In the program mode the OE/V<sub>PP</sub> input is pulsed from a TTL level to 21V.

Table 1. Mode Selection

| PINS                               | CE<br>(18)      | OE/V <sub>PP</sub> (20) | Ag<br>(22) | V <sub>CC</sub> (24) | OUTPUTS<br>(9-11,13-17) |  |  |

|------------------------------------|-----------------|-------------------------|------------|----------------------|-------------------------|--|--|

| Read                               | VIL             | VIL                     | х          | Vcc                  | D <sub>OUT</sub>        |  |  |

| Output Disable                     | VIL             | VIH                     | ×          | Vcc                  | High Z                  |  |  |

| Standby                            | VIH             | х                       | Х          | Vcc                  | High Z                  |  |  |

| Program -                          | ViL             | V <sub>PP</sub>         | х          | Vcc                  | D <sub>IN</sub>         |  |  |

| Program Inhibit                    | VIH             | Vpp                     | x          | Vcc                  | High Z                  |  |  |

| Int <sub>9</sub> ligent Identifier | V <sub>IL</sub> | V <sub>IL</sub>         | ٧н         | Vcc                  | Code                    |  |  |

#### NOTES:

1. X can be VIH or VIL

2.  $V_H = 12V \pm 0.5V$

#### Read Mode

The P2732A has two control functions, both of which must be logically active in order to obtain data at the outputs. Chip Enable  $(\overline{CE})$  is the power control and should be used for device selection. Output Enable  $(\overline{OE})$  is the output control and should be used to gather data from the output pins, independent of device selection. Assuming that addresses are stable, address access time  $(t_{ACC})$  is equal to the delay from  $\overline{CE}$  to output  $(t_{CE})$ . Data is available at the outputs after the

falling edge of  $\overline{OE}$ , assuming that  $\overline{CE}$  has been low and addresses have been stable for at least  $t_{ACC}$  -toe.

#### Standby Mode

The P2732A has a standby mode which reduces the maximum active current from 100 mA to 35 mA. The P2732A is placed in the standby mode by applying a TTL-high signal to the  $\overline{CE}$  input. When in standby mode, the outputs are in a high impedance state, independent of the  $\overline{OE}$  input.

#### TWO LINE OUTPUT CONTROL

Because EPROMs are usually used in larger memory arrays, Intel has provided two control lines which accommodate this multiple memory connection. The two control lines allow for:

- a) The lowest possible memory power dissipation, and

- b) complete assurance that output bus contention will not occur.

To use these two control lines most efficiently,  $\overline{CE}$  (pin 18) should be decoded and used as the primary device selecting function, while  $\overline{OE}$  (pin 20) should be made a common connection to all devices in the array and connected to the  $\overline{READ}$  line from the system control bus. This assures that all deselected memory devices are in their low power standby mode and that the output pins are active only when data is desired from a particular memory device.

#### **System Consideration**

The power switching characteristics of HMOS-E EPROMs require careful decoupling of the devices. The supply current, ICC, has three segments that are of interest to the system designer—the standby current level, the active current level, and the transient current peaks that are produced by the falling and rising edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitive loading of the device. The associated transient voltage peaks can be suppressed by complying with Intel's two line control and by use of properly selected decoupling capacitors. It is recommended that a 0.1 µF ceramic capacitor be used on every device between V<sub>CC</sub> and GND. This should be a high frequency capacitor of low inherent inductance and should be placed as close to the device as possible. In addition, a 4.7 µF bulk electrolytic capacitor should be used between V<sub>CC</sub> and GND for every eight devices. The bulk capacitor should be located near where the power supply is connected to the array. The purpose of the bulk capacitor is to overcome the voltage droop caused by the inductive effects of PC board traces.

Application Note AP-72, which is available from Intel's Literature Department, describes microprocessor system implementation of the two-line control function on Intel's EPROMs.

#### **PROGRAMMING**

CAUTION: Exceeding 22V on Pin 20 (OE/V<sub>PP</sub>) will permanently damage the P2732A.

Initially all bits of the P2732A are in the "1" state. Data is introduced by selectively programming "0's" into the bit locations. Although only "0's" will be programmed, both "1's" and "0's" can be present in the data word.

The P2732A is in the programming mode when the OE/V<sub>PP</sub> input is at 21V. It is required that a 0.1 μF capacitor be placed across OE/V<sub>PP</sub> and ground to suppress spurious voltage transients which may damage the device. The data to be programmed is

applied 8 bits in parallel to the data output pins. The levels required for the address and data inputs are TTL.

When the address and data are stable, a 20ms active low, TTL program pulse is applied to the  $\overline{CE}$  input. A program pulse must be applied at each address location to be programmed. You can program any location at any time—either individually, sequentially, or at random. The program pulse has a maximum width of 55ms. The P2732A must not be programmed with a DC signal applied to the  $\overline{CE}$  input.

Programming of multiple P2732As in parallel with the same data can be easily accomplished due to the simplicity of the programming requirements. Like inputs of the paralleled P2732As may be connected together when they are programmed with the same data. A low level TTL pulse applied to the CE input programs the paralleled P2732A.

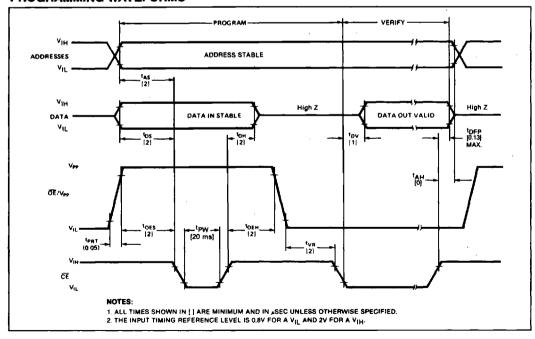

#### **PROGRAMMING WAVEFORMS**

# PROGRAMMING[1]

# D.C. PROGRAMMING CHARACTERISTICS: $T_A = 25 \pm 5^{\circ}\text{C}$ , $V_{CC} = 5V \pm 5\%$ , $V_{PP} = 21V \pm 0.5V$

|                 |                                             |       | Limits | 3                  |       |                                             |  |

|-----------------|---------------------------------------------|-------|--------|--------------------|-------|---------------------------------------------|--|

| Syrnbol         | Parameter                                   | Min.  | Тур.   | Max.               | Units | Test Conditions                             |  |

| Iu              | input Current (All inputs)                  | T     |        | 10                 | μА    | VIN = VIL or VIH                            |  |

| Vol             | Output Low Voltage During Verify            |       |        | 0.45               | V     | I <sub>OL</sub> = 2.1 mA                    |  |

| VOH             | Output High Voltage During Verify           | 2.4   |        |                    | V     | $I_{OH} = -400 \mu\text{A}$                 |  |

| Icc             | V <sub>CC</sub> Supply Current              |       | 85     | 100                | mA    |                                             |  |

| V <sub>IL</sub> | Input Low Level (All Inputs)                | - 0.1 |        | 0.8                | V     |                                             |  |

| VIH             | Input High Level (All Inputs Except OE/Vpp) | 2.0   |        | V <sub>CC</sub> +1 | V     |                                             |  |

| Ірр             | V <sub>PP</sub> Supply Current              |       |        | 30                 | mA    | CE = V <sub>IL</sub> , OE = V <sub>PP</sub> |  |

| V <sub>ID</sub> | Ag inteligent Identifier Voltage            | 11.5  |        | 12.5               | ٧     | -                                           |  |

# A.C. PROGRAMMING CHARACTERISTICS: $T_A = 25 \pm 5^{\circ}\text{C}$ , $V_{CC} = 5\text{V} \pm 5\%$ , $V_{PP} = 21\text{V} \pm 0.5\text{V}$

|                  |                                       |      | Limits |      |       |                    |  |  |

|------------------|---------------------------------------|------|--------|------|-------|--------------------|--|--|

| Symbol           | Parameter                             | Min. | Тур.   | Max. | Units | Test Conditions†   |  |  |

| tas              | Address Setup Time                    | 2    |        |      | μъ    |                    |  |  |

| toes             | OE Setup Time                         | 2    |        |      | μS    |                    |  |  |

| tos              | Data Setup Time                       | 2    |        |      | μS    |                    |  |  |

| t <sub>AH</sub>  | Address Hold Time                     | 0    |        |      | μS    |                    |  |  |

| toeh             | OE Hold Time                          | 2    |        |      | μS    |                    |  |  |

| t <sub>DH</sub>  | Data Hold Time                        | 2    |        |      | μS    |                    |  |  |

| t <sub>DFP</sub> | OE High to Output Not Driven          | 0    |        | 130  | ns    |                    |  |  |

| t <sub>DV</sub>  | Data Valid from CE                    |      |        | 1    | μS    | CE = VIL, OE = VIL |  |  |

| tpw              | CE Pulse Width During Programming     | 20   | 50     | 55   | ms    |                    |  |  |

| tent             | OE Pulse Rise Time During Programming | 50   |        |      | ns    |                    |  |  |

| typ              | V <sub>PP</sub> Recovery Time         | 2    |        |      | μS    |                    |  |  |

#### A.C. TEST CONDITIONS

#### NOTE:

When programming the P2732A, a 0.1μF capacitor is required across OE/V<sub>PP</sub> and ground to suppress spurious voltage transients which may damage the device.

# Program Inhibit

Programming of multiple P2732As in parallel with different data is also easily accomplished. Except for  $\overline{CE}$ , all like inputs (including  $\overline{OE}$ ) of the parallel P2732As may be common. A TTL low level pulse applied to a P2732As  $\overline{CE}$  input with  $\overline{OE}/V_{PP}$  at 21V will program that P2732A. A high level  $\overline{CE}$  input inhibits the other P2732As from being programmed.

#### Verify

A verify (Read) should be performed on the programmed bits to determine that they were correctly programmed. The verify is accomplished with  $\overline{\text{OE}}/\text{V}_{PP}$  and  $\overline{\text{CE}}$  at  $\text{V}_{IL}$ . Data should be verified  $\text{t}_{DV}$  after the falling edge of  $\overline{\text{CE}}$ .

# inteligent Identifier™ Mode

The inteligent Identifier Mode allows the reading out of a binary code from an EPROM that will identify its

manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional in the  $25^{\circ}\text{C}$   $\pm 5^{\circ}\text{C}$  ambient temperature range.

To activate this mode, the programming equipment must force 11.5V to 12.5V on address line A9 (pin 22) of the P2732A. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 (pin 8) from  $V_{IL}$  to  $V_{IH}$ . All other address lines must be held at  $V_{IL}$  during intelligent Identifier Mode.

Byte 0 (A0 =  $V_{IL}$ ) represents the manufacturer code and byte 1(A0 =  $V_{IH}$ ) the device identifier code. For the Intel P2732A, these two identifier bytes are given in Table 2. All identifiers for manufacturer and device codes will possess odd parity, with the MSB (0<sub>7</sub>) defined as the parity bit.

Table 2: P2732A inteligent Identifier™ Bytes

| Pine              | A <sub>8</sub> (8) | O <sub>7</sub><br>(17) | O <sub>6</sub> (16) | O <sub>5</sub> (15) | O <sub>4</sub> (14) | O <sub>3</sub> (13) | O <sub>2</sub> (11) | O <sub>1</sub> (10) | O <sub>0</sub> (9) | Hex<br>Data |

|-------------------|--------------------|------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--------------------|-------------|

| Manufacturer Code | $V_{iL}$           | 1                      | 0                   | 0                   | 0                   | 1                   | 0                   | 0                   | 1                  | 89          |

| Device Code       | V <sub>IH</sub>    | 0                      | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 1                  | 01          |