GS3140

Multi-Rate Adaptive 3G SDI Equalizer

### **Key Features**

- Multi-standard operation at rates between 1Mb/s and 2.97Gb/s

- SMPTE ST 424, SMPTE ST 292 and SMPTE ST 259

compliant

- AES10 (MADI) compatible

- Industry leading cable reach, with automatic cable equalization for different lengths of cable

- Performance optimized for 125Mb/s, 270Mb/s, 1.485Gb/s, and 2.97Gb/s. Typical equalized length of Belden 1694A cable up to:

- 200m at 2.97Gb/s

- 280m at 1.485Gb/s

- 500m at 270Mb/s

- 1.8V core power supply

- Typical power consumption of 84mW when DC-coupled at 1.2V with OUTPUT\_SWING = 0011<sub>b</sub> (see Table 4-2)

- Ultra-low power mode for shorter cable reach applications

- Upstream launch swing compensation from 250mV<sub>ppd</sub> to 1V<sub>ppd</sub> in approximately 50mV<sub>ppd</sub> steps (Default 750mV<sub>ppd</sub>)

- Auto/Manual bypass (useful for low data rates with slow rise/fall times)

- Robust, noise-immune signal detection with squelch threshold adjustment

- Auto/Manual control of SLEEP/MUTE/DISABLE OUTPUT modes

- Data Rate detection and indication

- <MADI, MADI, SD, HD, 3G differentiation</li>

- Digital cable length indication (CLI)

- Differential output supports DC-coupling from 1.2V to 2.5V CML logic and AC-coupling for other logic families

- Programmable/Rate-dependent output de-emphasis level and delay

- Host interface for status and control

- 3kV HBM ESD protection on all pins

- Wide operating temperature range of -40°C to +85°C

- Small footprint QFN–COL package (16-pin, 4mm x 4mm)

- Pb-free and RoHS compliant

- Pin-compatible with the GS6140

### Applications

• SMPTE ST 424, SMPTE ST 292, SMPTE ST 259 and AES10 coaxial cable serial digital interfaces

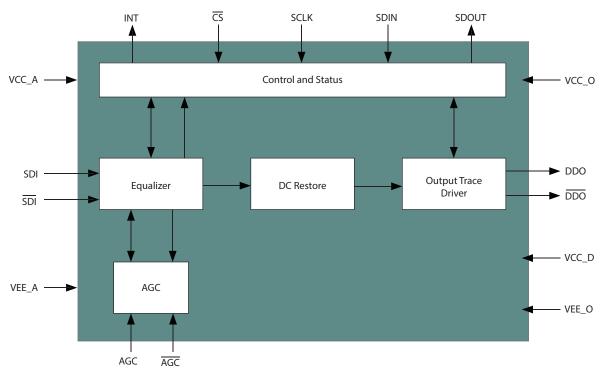

### Description

The GS3140 is a high-speed BiCMOS device designed to equalize and restore signals received over cable.

The device is designed to support SMPTE ST 424, SMPTE ST 292, SMPTE ST 259 and AES10 (MADI), and it is optimized for performance at 125Mb/s, 270Mb/s, 1.485Gb/s, and 2.97Gb/s.

The device supports MADI serial signals at 125Mb/s with peak-to-peak launch amplitude between  $300mV_{ppd}$  and  $600mV_{ppd}$  (with AES10 spec rise and fall times) and  $800mV_{ppd}\pm10\%$  (with SD-SDI rise and fall times).

The GS3140 features DC restoration to compensate for the DC content of SMPTE pathological signals.

Loss of Signal (LOS) is detected when the input carrier is lost or signal amplitude falls below a programmable threshold. This is further processed by a filter programmable up to 1.6s before LOS status is asserted. The device can be programmed to automatically sleep/mute/disable the output on loss of signal.

An interrupt pin (INT) indicates LOS by default, and can be programmed to signal various other statuses.

When the BYPASS control bit is set, the equalizing and DC restore stages are disengaged. This is useful for signals launched at the source with low data rates and/or slow rise and fall times.

The differential output can be DC-coupled to Semtech's reclockers and cable drivers, as well as industry-standard +1.2V, +1.8V and +2.5V CML logic by changing the voltage applied to the VCC\_O pin.

The GS3140 also features programmable output de-emphasis with eight user-selectable operating levels to support long PCB traces at the output of the device. The output swing can be programmed, via the user interface, from approximately 250mV<sub>ppd</sub> to 1V<sub>ppd</sub> in 50mV<sub>ppd</sub> steps. The device comes in a 16-pin, 4mm x 4mm QFN–COL package.

Power consumption of the GS3140 is typically 84mW when DC-coupled to a +1.2V termination voltage with OUTPUT\_SWING =  $0011_b$  (see Table 4-2).

The GS3140 is Pb-free, and the encapsulation compound does not contain halogenated flame retardant.

This component and all homogeneous subcomponents are RoHS compliant.

## **Revision History**

| Version | ECO    | PCN | Date         | Changes and/or Modifications                                  |

|---------|--------|-----|--------------|---------------------------------------------------------------|

| 1       | 025657 | —   | May 2015     | Converted document from Draft Data Sheet to Final Data Sheet. |

| 0       | 024058 | —   | January 2015 | New Document.                                                 |

### Contents

| 1. Pin  | Out                                           | 5  |

|---------|-----------------------------------------------|----|

| 1       | .1 GS3140 Pin Assignment                      | 5  |

| 1       | .2 GS3140 Pin Descriptions                    | 5  |

| 2. Elec | trical Characteristics                        | 7  |

| 2       | .1 Absolute Maximum Ratings                   | 7  |

| 2       | .2 DC Electrical Characteristics              | 7  |

| 2       | .3 AC Electrical Characteristics              | 9  |

| 3. Inpi | ut/Output Circuits                            | 11 |

| 4. Det  | ailed Description                             | 12 |

| 4       | .1 Serial Digital Inputs (SDI/SDI)            | 12 |

|         | 4.1.1 Upstream Launch Swing Compensation      | 12 |

| 4       | .2 Automatic (Adaptive) Cable Equalization    | 12 |

| 4       | .3 Cable Length Indication                    | 13 |

|         | .4 Programmable Squelch Threshold             |    |

| 4       | .5 Loss of Signal (LOS)                       |    |

|         | 4.5.1 Programmable LOS Filter                 | 14 |

|         | .6 Rate Detection                             |    |

|         | .7 Interrupt (INT)/ Status Output             |    |

| 4       | .8 Power Modes                                |    |

|         | 4.8.1 Bypass                                  | 15 |

|         | 4.8.2 Sleep                                   |    |

|         | 4.8.3 Mute                                    | 16 |

|         | 4.8.4 Sleep-Mute                              | 16 |

|         | 4.8.5 Output Disable                          | 16 |

| 4       | .9 Serial Digital Output (DDO/DDO)            | 16 |

|         | 4.9.1 Adjustable Output Swing and De-Emphasis |    |

|         | 4.9.2 Output Common Mode Voltage              |    |

|         | .10 Device Reset                              |    |

| 4       | .11 Gennum Serial Peripheral Interface (GSPI) |    |

|         | 4.11.1 CS Pin                                 | 19 |

|         | 4.11.2 SDIN Pin                               |    |

|         | 4.11.3 SDOUT Pin                              |    |

|         | 4.11.4 SCLK Pin                               |    |

|         | 4.11.5 Command Word Description               | 22 |

www.semtech.com

| 4.11.6 GSPI Transaction Timing          | 24 |

|-----------------------------------------|----|

| 4.11.7 Single Read/Write Access         | 25 |

| 4.11.8 Auto-increment Read/Write Access |    |

| 4.11.9 Default GSPI Operation           | 28 |

| 4.11.10 Setting a Device Unit Address   | 29 |

| 5. Host Interface Register Map          | 30 |

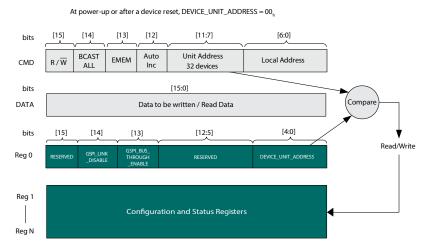

| 6. Application Information              |    |

| 6.1 Typical Application Circuit         | 36 |

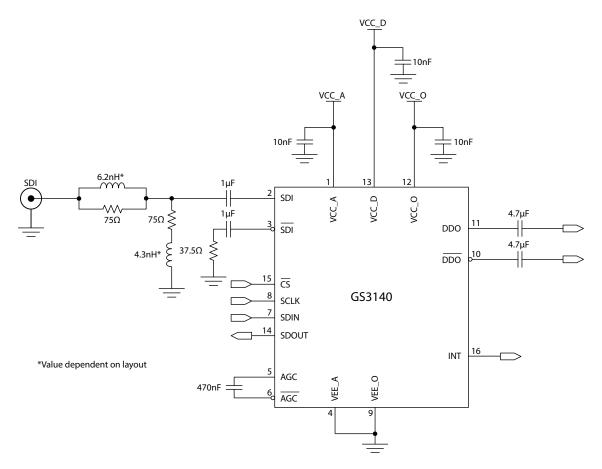

| 7. Package & Ordering Information       |    |

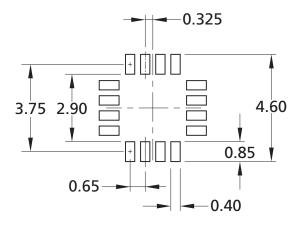

| 7.1 Package Dimensions                  | 37 |

| 7.2 Packaging Data                      |    |

| 7.3 Recommended PCB Footprint           | 38 |

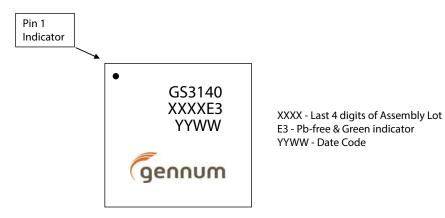

| 7.4 Marking Diagram                     | 39 |

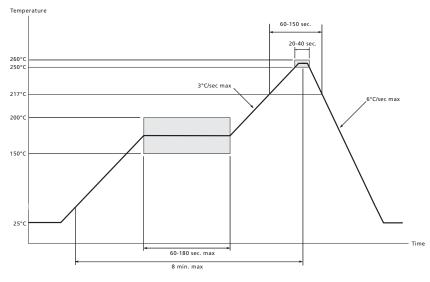

| 7.5 Solder Reflow Profiles              | 39 |

| 7.6 Ordering Information                | 39 |

|                                         |    |

# 1. Pin Out

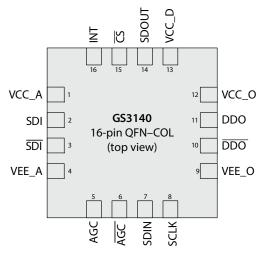

## 1.1 GS3140 Pin Assignment

Figure 1-1: GS3140 Pin Out

## 1.2 GS3140 Pin Descriptions

| Pin Number | Name                   | Туре          | Description                                                                                                          |

|------------|------------------------|---------------|----------------------------------------------------------------------------------------------------------------------|

| 1          | VCC_A                  | Power         | Most positive power supply connection for the input buffer and core.<br>Connect to 1.8V.                             |

| 2, 3       | SDI, <mark>SD</mark> I | Input         | Serial digital differential input.                                                                                   |

| 4          | VEE_A                  | Power         | Most negative power supply connection for the input buffer and core.<br>Connect to GND.                              |

| 5, 6       | AGC, AGC               | Analog I/O    | External Automatic Gain Control capacitor.                                                                           |

| 7          | SDIN                   | Digital Input | Host Interface Serial Data Input.                                                                                    |

| 8          | SCLK                   | Digital Input | Host Interface Serial Clock Input.                                                                                   |

| 9          | VEE_O                  | Power         | Most negative power supply connection for the output buffers, digital<br>IO and digital circuits.<br>Connect to GND. |

| 10, 11     | DDO, DDO               | Output        | Serial digital differential output.                                                                                  |

| 12         | VCC_0                  | Power         | Most positive power supply connection for the output buffer.<br>Connect to 1.2V - 2.5V.                              |

www.semtech.com

| Pin Number | Name          | Туре           | Description                                                                        |

|------------|---------------|----------------|------------------------------------------------------------------------------------|

| 13         | VCC_D         | Power          | Most positive power supply connection for the digital IO and the digital circuits. |

|            |               |                | Connect to 1.8V.                                                                   |

| 14         | SDOUT         | Digital Output | Host Interface Serial Data Output                                                  |

| 15         | <del>CS</del> | Digital Input  | Host Interface Chip Select (active LOW)                                            |

| 16         | INT           | Digital Output | Interrupt, programmable status pin.<br>Default is Loss of Signal (LOS)             |

Table 1-1: GS3140 Pin Descriptions (Continued)

# 2. Electrical Characteristics

## 2.1 Absolute Maximum Ratings

#### Table 2-1: Absolute Maximum Ratings

| Parameter                                   | Value                 |

|---------------------------------------------|-----------------------|

| Supply Voltage - Core (VCC_A and VCC_D)     | -0.5V to +2.1V        |

| Supply Voltage - Output Driver (VCC_O)      | -0.5V to +2.8V        |

| Input ESD Voltage                           | 3kV HBM               |

| Storage Temperature Range (T <sub>s</sub> ) | -50°C to 125°C        |

| Input Voltage Range (any input)             | -0.3 to (VCC_A +0.3)V |

| Solder Reflow Temperature                   | 260°C                 |

**Note:** Absolute Maximum Ratings are those values beyond which damage may occur. Functional operation outside of the ranges shown in the AC/DC electrical characteristics tables is not guaranteed.

## 2.2 DC Electrical Characteristics

#### **Table 2-2: DC Electrical Characteristics**

$V_{CC\_A}, V_{CC\_D}, V_{CC\_O}$  = +1.8V ±5%,  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                         | Symbol                               | Conditions                                                   | Min   | Тур | Max   | Units | Notes              |

|-----------------------------------|--------------------------------------|--------------------------------------------------------------|-------|-----|-------|-------|--------------------|

| Supply Voltage - Core             | V <sub>CC_A</sub> ,V <sub>CC_D</sub> | _                                                            | 1.710 | 1.8 | 1.890 | V     | _                  |

| Supply Voltage - Output<br>Driver | V <sub>CC_0</sub>                    | _                                                            | 1.140 | _   | 2.625 | V     | _                  |

|                                   |                                      | $V_{CC_O} = 1.2V$<br>OUTPUT_SWING = 0011 <sub>b</sub>        | _     | 85  | 135   | mW    | 1, 2               |

|                                   | P <sub>D</sub>                       | $V_{CC_O} = 1.2V$<br>OUTPUT_SWING = 1011 <sub>b</sub>        | _     | 95  | 148   | mW    | 1, 2               |

| Devee                             |                                      | $V_{CC_O} = 1.8V$<br>OUTPUT_SWING = 0011 <sub>b</sub>        | _     | 90  | 143   | mW    | 1, 2               |

| Power                             |                                      | V <sub>CC_O</sub> = 1.8V<br>OUTPUT_SWING = 1011 <sub>b</sub> | _     | 104 | 162   | mW    | 1, 2               |

|                                   |                                      | $V_{CC_O} = 2.5V$<br>OUTPUT_SWING = 0011 <sub>b</sub>        | _     | 96  | 152   | mW    | 1, 2               |

|                                   |                                      | $V_{CC_O} = 2.5V$<br>OUTPUT_SWING = 1011 <sub>b</sub>        | _     | 116 | 178   | mW    | 1, 2               |

| 5S3140<br>Final Data Sheet Rev.1  |                                      | www.semtech.com                                              |       |     |       |       | 7 of 40<br>Semtech |

### Table 2-2: DC Electrical Characteristics (Continued)

| Parameter                             | Symbol                    | Conditions                                                               | Min               | Тур        | Max              | Units | Notes |

|---------------------------------------|---------------------------|--------------------------------------------------------------------------|-------------------|------------|------------------|-------|-------|

| Power Consumption –<br>Bypass Mode    | P <sub>D_BYPASS</sub>     | _                                                                        | _                 | 58         | 88               | mW    | _     |

| Power Consumption –<br>Output Mute    | P <sub>D_MUTE</sub>       | _                                                                        | _                 | 83         | 127              | mW    | _     |

| Power Consumption –<br>Output Disable | P <sub>D_DISABLE</sub>    | _                                                                        | _                 | 70         | 114              | mW    | _     |

| Power Consumption –<br>Sleep-Mute     | P <sub>D_SLEEP_MUTE</sub> | _                                                                        | _                 | 49         | _                | mW    | _     |

| Power Consumption – Sleep             | P <sub>D_SLEEP</sub>      | _                                                                        | _                 | 11         | 27               | mW    | _     |

| Supply Current – Core                 | I <sub>DD_A</sub>         | $V_{CC_A} = 1.8V$                                                        | _                 | 37         | 56               | mA    | 1, 3  |

| Supply Current - Digital              | I <sub>DD_D</sub>         | V <sub>CC_D</sub> = 1.8V                                                 | _                 | 5          | 7.5              | mA    | _     |

| Supply Current - Output               | 1                         | $V_{DD_O} = +1.2V \text{ to } +2.5V$<br>OUTPUT_SWING = 0011 <sub>b</sub> | _                 | 8          | 12               | mA    | 1, 2  |

| Driver                                | I <sub>DD_O</sub>         | $V_{DD_O} = +1.2V \text{ to } +2.5V$<br>OUTPUT_SWING = 1011 <sub>b</sub> | _                 | 16         | 22               | mA    | 1, 2  |

| Serial Input Common<br>Mode Voltage   | V <sub>CMIN</sub>         | _                                                                        | 1.4               | _          | 1.6              | V     | _     |

| Serial Output Common<br>Mode Voltage  | V <sub>CMOUT</sub>        |                                                                          | See Sec           | tion 4.9.2 | 2                |       |       |

| Input Voltage - Digital Pins          | V <sub>IH</sub>           | _                                                                        | 0.65*<br>VDD_DIG  | _          | VDD_DIG          | V     |       |

| (CS, SDIN, SCLK)                      | V <sub>IL</sub>           | _                                                                        | 0                 | _          | 0.35*<br>VDD_DIG | V     | _     |

| Output Voltage - Digital Pins         | V <sub>OH</sub>           | I <sub>OH</sub> = -2mA                                                   | VDD_DIG<br>- 0.45 |            | _                | V     |       |

| (INT, SDOUT)                          | V <sub>OL</sub>           | I <sub>OH</sub> = 2mA                                                    | _                 | _          | 0.45             | V     | _     |

$V_{CC\_A}, V_{CC\_D}, V_{CC\_O}$  = +1.8V ±5%,  $T_A$  = -40°C to +85°C, unless otherwise shown

#### Notes:

1. De-emphasis off.

2. See Table 4-2 for all the output swing settings.

3. With de-emphasis enabled, add a typical 4mA.

## **2.3 AC Electrical Characteristics**

### **Table 2-3: AC Electrical Characteristics**

$V_{CC\_A}, V_{CC\_D}, V_{CC\_O}$  = +1.8V ±5%,  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                      | Symbol            | Conditions                                            | Min | Тур  | Мах  | Units             | Notes   |

|--------------------------------|-------------------|-------------------------------------------------------|-----|------|------|-------------------|---------|

| Serial Input Data Rate         | DR <sub>DDO</sub> | —                                                     | 1   | _    | 2970 | Mb/s              | _       |

|                                |                   | Differential,<br>1.485Gb/s                            | 720 | 800  | 960  | mV <sub>ppd</sub> | _       |

| Input Voltage Swing            | $\Delta V_{SDI}$  | Differential,<br>125Mb/s, 270Mb/s, and<br>2.97Gb/s    | 720 | 800  | 880  | mV <sub>ppd</sub> | _       |

| Input Sensitivity              | —                 | 16 increments of<br>approximately 50mV <sub>ppd</sub> | 250 |      | 1000 | mV <sub>ppd</sub> | 1       |

| Output Voltage Swing           | $\Delta V_{DDO}$  | OUTPUT_SWING = 0100 <sub>b</sub>                      | 345 | 410  | 475  | mV <sub>ppd</sub> | 2       |

| Output Voltage Swing           | Δv <sub>DDO</sub> | OUTPUT_SWING = 1100b                                  | 665 | 800  | 935  | mV <sub>ppd</sub> | 2       |

|                                |                   | 2.97Gb/s<br>Belden 1694A: 0-120m,<br>-20°C to +70°C   |     | 0.2  | 0.25 | UI                | 3, 4, 5 |

|                                | Ърр               | 2.97Gb/s<br>Belden 1694A: 120-180m,<br>-20°C to +70°C | _   | 0.4  | 0.5  | UI                | 3, 4, 5 |

|                                |                   | 2.97Gb/s<br>Belden 1694A: 180-200m,<br>-20°C to +70°C | _   | 0.4  | _    | UI                | 3, 4, 5 |

| Output Jitter at Various Cable |                   | 1.485Gb/s<br>Belden 1694A: 0-180m                     | —   | 0.15 | 0.25 | UI                | —       |

|                                |                   | 1.485Gb/s<br>Belden 1694A: 180-240m                   |     | 0.3  | 0.4  | UI                | _       |

| Lengths and Data Rates         |                   | 1.485Gb/s<br>Belden 1694A: 240-280m                   |     | 0.35 | 0.45 | UI                | _       |

|                                |                   | 270Mb/s<br>Belden 1694A: 0-300m                       | —   | 0.1  | 0.2  | UI                | —       |

|                                |                   | 270Mb/s<br>Belden 1694A: 300-350m                     |     | 0.2  | 0.3  |                   | _       |

|                                |                   | 270Mb/s<br>Belden 1694A: 350-450m                     | —   | 0.3  | 0.4  | UI                | —       |

|                                |                   | 270Mb/s<br>Belden 1694A: 450-500m                     | —   | 0.3  | —    | UI                | —       |

|                                |                   | 125Mb/s<br>Belden 1694A: 0-200m                       | —   | —    | 0.1  | UI                | _       |

| Output Pico/Fall time          |                   | 2.97Gb/s and 1.485Gb/s<br>20% - 80%                   | —   | 45   | 90   | ps                | _       |

| Output Rise/Fall time          |                   | 270Mb/s<br>20% - 80%                                  | —   | 50   | 200  | ps                | _       |

| Mismatch in rise/fall time     |                   | 2.97Gb/s and 1.485Gb/s                                | _   | _    | 30   | ps                |         |

|                                |                   | 270Mb/s                                               | _   | —    | 50   | ps                | _       |

www.semtech.com

### Table 2-3: AC Electrical Characteristics (Continued)

$V_{CC_A}$ ,  $V_{CC_D}$ ,  $V_{CC_O}$  = +1.8V ±5%,  $T_A$  = -40°C to +85°C, unless otherwise shown

| Parameter                                            | Symbol | Conditions             | Min | Тур | Мах | Units | Notes |

|------------------------------------------------------|--------|------------------------|-----|-----|-----|-------|-------|

| Duty Cycle Distortion                                |        | 2.97Gb/s and 1.485Gb/s | _   | _   | 65  | ps    |       |

| Duty Cycle Distortion                                |        | 270Mb/s                | _   | _   | 65  | ps    | _     |

| Input Resistance                                     |        | Single ended           | _   | 3.1 | _   | kΩ    | _     |

| Input Capacitance                                    |        | Single ended           | —   | 1.1 | —   | pF    | —     |

| Output Resistance                                    |        | Single ended           | _   | 50  | _   | Ω     | _     |

| Input Capacitance - Digital<br>Pins (CS, SDIN, SCLK) |        | _                      |     | 0.8 | _   | pF    | _     |

| Output Capacitance - Digital<br>Pins (INT, SDOUT)    |        | _                      | _   | 1.0 | _   | pF    | _     |

| Input Return Loss                                    |        | 1.485GHz to 2.97GHz    | 10  | —   | _   | dB    | 6     |

|                                                      |        | 5MHz to 1.485GHz       | 15  | _   |     | dB    | 6     |

#### Note:

1. For input swing < 720 mV  $_{\rm ppd}$  , the overall cable reach may be reduced.

2. See Table 4-2 for all the output swing settings.

3. For -40°C to -20°C operation at less than 40m of Belden 1694A cable, add 0.1UI to jitter specification.

4. For -40°C to -20°C operation at greater than 40m of Belden 1694A cable, jitter specification does not change.

5. Operation from  $+70^{\circ}$ C to  $+85^{\circ}$ C is not supported.

6. Using Semtech's recommended application circuit and design guides.

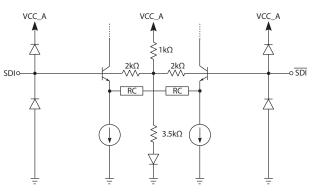

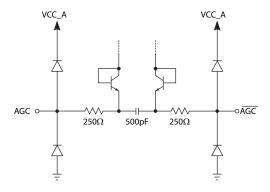

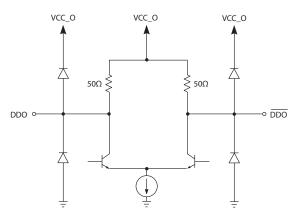

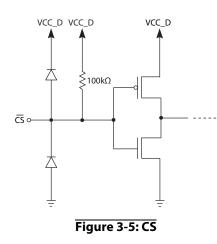

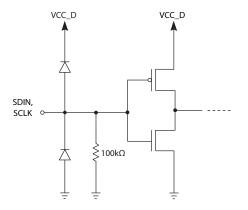

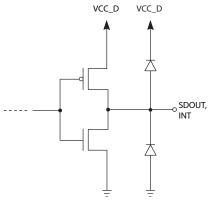

# 3. Input/Output Circuits

Figure 3-1: Serial Data Input

Figure 3-2: AGC, AGC

Figure 3-3: Serial Data Output

Figure 3-4: SDIN and SCLK

Figure 3-6: SDOUT and INT

# 4. Detailed Description

The GS3140 is a high-speed BiCMOS IC designed to equalize serial digital signals.

The GS3140 can equalize 3G SDI, HD-SDI, SD-SDI and AES10 serial digital signals, and will typically equalize up to 200m at 2.97Gb/s, 280m at 1.485Gb/s, 500m at 270Mb/s and 200m at 125Mb/s. When DC coupling the output of a device to a 1.2V CML load, the GS3140 typically consumes 84mW of power with a 400mV<sub>ppd</sub> output swing.

# 4.1 Serial Digital Inputs (SDI/SDI)

The GS3140 has a high-impedance input buffer.

The received serial data signal can be connected to the input pins (SDI/SDI) in either a differential or single-ended configuration.

The input circuit is self-biasing to allow for simple AC-coupling of input signals to the device.

### 4.1.1 Upstream Launch Swing Compensation

The GS3140 has automatic gain control that is based on the assumption that the cable driver in the upstream device is SMPTE compliant and has a launch swing of  $800 \text{mV}_{ppd} \pm 10\%$ .

When the source amplitude is known to be non-SMPTE compliant, a compensation adjustment can be made. The GS3140 can adjust for nominal launch swings between  $250mV_{ppd}$  to  $1000mV_{ppd}$ , in approximately  $50mV_{ppd}$  increments. Upstream launch swing compensation can be adjusted using the LAUNCH\_SWING\_COMPENSATION bits in EQ\_CONF\_REG\_2 register. The default value is  $800mV_{ppd}$  (1011<sub>b</sub>).

## 4.2 Automatic (Adaptive) Cable Equalization

The GS3140 automatically adjusts its gain to equalize and restore signals received over different lengths of coaxial cable having loss characteristics similar to Belden 8281 or 1694A. The device is designed to automatically equalize SMPTE SDI signal rates up to 2.97Gb/s, DVB-ASI signals at 270Mb/s, and MADI signals at 125Mb/s.

The GS3140 has the ability to limit the reach of the device to one of four values through its host interface. The default value is the maximum range. The maximum range of the device is also a function of the detected data rate, so the maximum cable will not exceed the supported reach for that rate.

## 4.3 Cable Length Indication

The GS3140 reports the input signal strength through the CABLE\_LENGTH\_INDICATOR bits in the STATUS\_REG\_0 register, accessible through the device's host interface. The Cable Length Indication (CLI) is a simple, numeric value in the range from  $0_h$  to EF<sub>h</sub>. This number can be approximated as a cable length in meters by applying one of the cable scaling factors shown in Table 4-1 below for some commonly used coaxial cables.

| Cable Type   | CLI Scaling Factor |

|--------------|--------------------|

| Belden 1694A | 2.5                |

| Belden 8281  | 1.77               |

#### **Table 4-1: Cable Length Scaling Factors**

The CLI readout value has a multiplication resolution of 1 between  $0_h$  and  $7F_h$ . In the range from  $80_h$  to  $EF_h$  the measurement resolution of CLI is reduced, and CLI value increments by a multiple of 3.

**Note:** Any additional loss due to other transmission line elements (such as patch panels, barrels, extra connectors, etc.), also translates to an equivalent cable length based on the cable scaling factor.

## 4.4 Programmable Squelch Threshold

The GS3140 features a programmable squelch threshold, set through the device's host interface. It impacts Loss of Signal (LOS) status. As shown in Figure 4-1, squelch only affects the LOS status when bits AUTO\_BYPASS, BYPASS, and SLEEP[1:0] in EQ\_CONF\_REG\_0 are all 0.

The device continually compares the strength of the input signal as set in the CABLE\_LENGTH\_INDICATOR bits in the STATUS\_REG\_0 register to the squelch threshold set by the SQUELCH\_THRESHOLD bits in the EQ\_CONF\_REG\_1 register.

When the value reported by the CABLE\_LENGTH\_INDICATOR bits exceeds the value programmed by the SQUELCH\_THRESHOLD bits by 3 or more, the Loss of Signal (LOS) status bit in the STATUS\_REG\_0 register is set to 1.

When the value reported by the CABLE\_LENGTH\_INDICATOR bits falls below the value programmed by the SQUELCH\_THRESHOLD bits by 3 or more, the Loss of Signal (LOS) status bit in the STATUS\_REG\_0 register is set to 0.

This  $\pm 2$  hysteresis around the SQUELCH\_THRESHOLD setting avoids chattering of the LOS bit status for input signal strengths right around the threshold setting.

By default, the squelch threshold is set to the maximum possible level, and therefore squelch is disabled.

## 4.5 Loss of Signal (LOS)

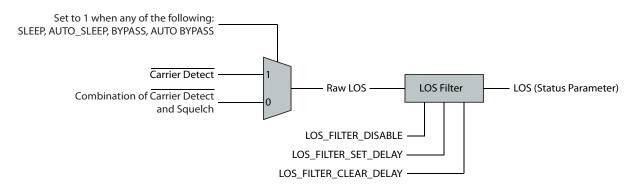

The Loss of Signal (LOS) status indicates whether or not a signal that meets the device's programmed thresholds is present at its input. When LOS is de-asserted (set to 0), a supported input signal has been detected. Figure 4-1 shows how LOS is derived.

The LOS function continuously monitors conditions of the input signal. In Sleep, Auto-Sleep, Bypass or Auto-Bypass modes, this is limited to carrier detection.

When LOS Filter is disabled, LOS will be asserted (set to 1) no less than 10 $\mu$ s and no longer than 40 $\mu$ s after the loss of a valid input signal, and will be de-asserted (set to 0) no more than 5 $\mu$ s after the connection of a valid input signal.

LOS is available via a status bit in STATUS\_REG\_0, and it is also available on the interrupt (INT) status pin, as selected using the INT\_SOURCE\_SELECT bits in INT\_OUT\_CONF\_REG\_0 register accessible through the device's host interface. LOS is the default output from the INT pin.

### 4.5.1 Programmable LOS Filter

The LOS Filter delays notification of the change in raw LOS until the new state persists contiguously for the programmed length of time. This increases stability of LOS signalling.

The LOS Filter assertion and de-assertion delays can be programmed through the GS3140 host interface. By default, the LOS Filter is set to 51.8µs assertion delay and 6.6ms de-assertion delay.

The LOS assertion delay can be set in the range from 0ms to 6.6ms in increments of 25.9µs. The LOS de-assertion delay can be set in the range of 0s to 1.7s in increments of 6.6ms. These parameters are accessible using the LOS\_FILTER\_SET\_DELAY and LOS\_FILTER\_CLEAR\_DELAY bits in LOS\_FILTER\_CONF\_REG\_0

The use of these parameters can be disabled using the LOS\_FILTER\_DISABLE bit in LOS\_FILTER\_CONF\_REG\_1. Figure 4-1 below shows the derivation of the LOS status indication, and how the LOS filter affects the output.

#### Figure 4-1: Factors Affecting the Assertion of the LOS Status Parameter

## 4.6 Rate Detection

The GS3140 will differentiate between 2.97Gb/s, 1.485Gb/s, 270Mb/s, 125Mb/s, and <125Mb/s. The detected data rate is reported using the DETECTED\_INPUT\_RATE bits in STATUS\_REG\_0 accessible through the device's host interface.

Indication of the detected rate is also available on the interrupt (INT) status pin, as selected using the INT\_SOURCE\_SELECT and INT\_CD\_MODE\_SELECT bits in INT\_OUT\_CONF\_REG\_0 accessible through the device's host interface.

## 4.7 Interrupt (INT)/ Status Output

The GS3140's programmable interrupt (INT) pin flags internal states, or changes of state to the host system. The default function of this pin is Loss of Signal (LOS). Other functions are programmed via the device's host interface. The additional functions include:

- Rate change detection

- Detection of a specific data rate or set of rates

These functions are chosen using bits INT\_SOURCE\_SELECT, INT\_CD\_MODE\_SELECT, and DATA\_RATE\_DETECTION in the INT\_OUT\_CONF\_REG\_0 register.

## 4.8 Power Modes

### 4.8.1 Bypass

The GS3140 supports a mode of operation where the equalizer core and DC restoration stages are bypassed. This mode is controlled by the settings of the BYPASS and AUTO\_BYPASS bits in EQ\_CONF\_REG\_0 of the host interface.

No equalization or DC restoration occurs in BYPASS mode. These functions are disabled in order to reduce power consumption of the device for signals that do not require equalization and DC restoration. When the device is in BYPASS, the LOS continues to function based on carrier detect.

In addition to Manual-BYPASS, Auto-BYPASS is also available. When the AUTO\_BYPASS bit in EQ\_CONF\_REG\_0 is set to 1, BYPASS is initiated by detection of an input signal with a data rate below MADI.

### 4.8.2 Sleep

The GS3140 features a SLEEP function that is controlled through the host interface.

When the part is in SLEEP mode, only carrier based Loss of Signal (LOS) detection remains active. All other sections of the part are powered down.

When in SLEEP mode, the part consumes 13mW of total power.

When Auto-SLEEP is selected, it is initiated by the assertion of LOS. Normal operation, Manual-SLEEP, and Auto-SLEEP are controlled using the SLEEP bits in EQ\_CONF\_REG\_0 accessed through the device's host interface.

### 4.8.3 Mute

The GS3140 features a MUTE function, in which the two halves of the output buffer are driven statically to opposing levels. One will be set to the level of  $V_{CC_O}$  and the other will be set to  $V_{CC_O}$  – swing amplitude (swing level set in the OUTPUT\_SWING bits of OUT\_CONF\_REG\_0).

When Auto-MUTE is selected, it is initiated by the assertion of LOS. Manual-MUTE and Auto-MUTE are controlled using the MUTE and AUTO\_OUTPUT\_MUTE bits in OUT\_CONF\_REG\_1 accessed through the device's host interface.

### 4.8.4 Sleep-Mute

By default, output drivers are powered down when the device is in SLEEP mode. However, the GS3140 also features another power saving sleep mode in which the output driver is muted (as described in Section 4.8.3) instead. All the other blocks are configured similar to the description in Section 4.8.2. The purpose of this mode is to output a noise-immune static signal while the chip is sleeping. Similar to SLEEP mode, both manual and automatic features are available.

When MUTE\_OUTPUT\_IN\_SLEEP bit in EQ\_CONF\_REG\_2 is set to 1, the output drivers will remain powered and enter MUTE whenever the device is in SLEEP.

### 4.8.5 Output Disable

The GS3140 features a mode of operation in which the output buffer is disabled to save power, but all other parts of the chip remain active.

This mode of operation consumes more power than SLEEP mode, but less power than normal operation. It facilitates faster return to normal operation than SLEEP mode when required, because all internal stages of the EQ core are already active in this mode.

By default, if the device is not set to any other automatic power mode (Auto-SLEEP, Auto-MUTE, Auto-SLEEP-MUTE), then the assertion of LOS will initiate OUTPUT DISABLE mode. The output buffer will remain disabled until a signal is present.

If there is a signal present, the outputs may still be manually disabled by setting the MANUAL\_OUTPUT\_DISABLE bit in OUT\_CONF\_REG\_1 to 1, accessed through the device's host interface.

# 4.9 Serial Digital Output (DDO/DDO)

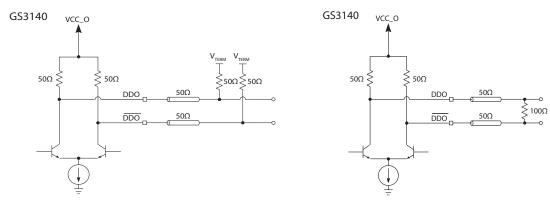

The output driver has a separate voltage supply ( $V_{CC_O}$ ) which operates between 1.2V - 2.5V. The output buffer includes two on-chip 50 $\Omega$  termination resistors.

The output is compatible with industry standard PECL, LVPECL, LVDS, and CML differential receivers when AC coupled using Semtech's recommended application circuit.

### 4.9.1 Adjustable Output Swing and De-Emphasis

The serial digital output swing is user-selectable from approximately  $250 \text{mV}_{ppd}$  to  $1V_{ppd}$  in increments of  $50 \text{mV}_{ppd}$ . For exact values see Table 4-2.

| OUTPUT_SWING      | Min | Тур | Max  | Units |

|-------------------|-----|-----|------|-------|

| 0000 <sub>b</sub> | 190 | 230 | 270  | mV    |

| 0001 <sub>b</sub> | 230 | 275 | 320  | mV    |

| 0010 <sub>b</sub> | 275 | 325 | 375  | mV    |

| 0011 <sub>b</sub> | 310 | 370 | 430  | mV    |

| 0100 <sub>b</sub> | 345 | 410 | 475  | mV    |

| 0101 <sub>b</sub> | 390 | 460 | 530  | mV    |

| 0110 <sub>b</sub> | 435 | 510 | 585  | mV    |

| 0111 <sub>b</sub> | 480 | 560 | 640  | mV    |

| 1000 <sub>b</sub> | 515 | 605 | 695  | mV    |

| 1001 <sub>b</sub> | 555 | 655 | 755  | mV    |

| 1010 <sub>b</sub> | 590 | 705 | 820  | mV    |

| 1011 <sub>b</sub> | 630 | 755 | 880  | mV    |

| 1100 <sub>b</sub> | 665 | 800 | 935  | mV    |

| 1101 <sub>b</sub> | 695 | 840 | 985  | mV    |

| 1110 <sub>b</sub> | 745 | 890 | 1035 | mV    |

| 1111 <sub>b</sub> | 800 | 930 | 1060 | mV    |

Table 4-2: Serial Digital Output Swing

To support driving long PCB traces, the GS3140 differential output buffer includes programmable de-emphasis with 8 operating levels between 0dB - 18.1dB. The de-emphasis delay can also be programmed to either 100ps or 200ps.

A second set of de-emphasis level and delay values, specifically targeted for 2.97Gb/s signals, can be selected either manually using the MANUAL\_DEEMPHASIS\_SELECT bit or automatically using the AUTO\_DEEMPHASIS\_ENABLE bit in OUT\_CONF\_REG\_0 accessible through the device's host interface.

#### Table 4-3: De-emphasis Levels

| De-emphasis Level | Operating Level | Units |

|-------------------|-----------------|-------|

| 000 <sub>b</sub>  | 0               | dB    |

| 001 <sub>b</sub>  | 1.2             | dB    |

| 010 <sub>b</sub>  | 2.5             | dB    |

| 011 <sub>b</sub>  | 4.1             | dB    |

| 100 <sub>b</sub>  | 6.0             | dB    |

| 101 <sub>b</sub>  | 8.5             | dB    |

| 110 <sub>b</sub>  | 12.0            | dB    |

| 111 <sub>b</sub>  | 18.1            | dB    |

### 4.9.2 Output Common Mode Voltage

The output common mode voltage level (V<sub>CMOUT</sub>) is a function of the output voltage swing, the output driver supply voltage (V<sub>CC\_O</sub>) and how the transmission line is terminated. If the outputs are terminated through 50 $\Omega$  resistors to a voltage V<sub>TERM</sub> equal to V<sub>CC\_O</sub>, as shown in Figure 4-2 below, the output common mode voltage is given by the following expression:

$$\mathbf{V}_{\mathbf{CMOUT}} = \mathbf{V}_{\mathbf{CC}_{\mathbf{O}}} - \frac{\Delta \mathbf{V}_{\mathbf{DDO}}}{4}$$

Equation 4-1

If the differential outputs are terminated across a  $100\Omega$  resistor, as shown in Figure 4-3 below, the output common mode voltage is given by the following expression:

Figure 4-2: 50 $\Omega$  Termination to V<sub>TERM</sub>

Figure 4-3: 100 $\Omega$  Parallel Output Termination

www.semtech.com

## 4.10 Device Reset

The GS3140 includes a reset function accessible via the device's host interface, which reverts all internal logic and register values to default.

The device can be reset with a single write of AD<sub>h</sub> to the RESET\_CONTROL bits of RESET\_REG\_0 register, which will assert and de-assert the device reset within the duration of the GSPI write access Data Word.

The device can be placed and held in reset by writing AA<sub>h</sub> to the RESET\_CONTROL bits of RESET\_REG\_0 register. Subsequent writes of DD<sub>h</sub> to the RESET\_CONTROL bits will de-assert device reset.

The current state of user-initiated device reset can be read from the RESET\_CONTROL bits of RESET\_REG\_0 register.

While in reset, host interface accesses to any other register will not be functional and all logic and configuration registers will be in reset state. While in reset serial digital differential output behaviour is undefined.

The digital logic and registers within the device will exit the reset state  $40\mu$ s after device reset is de-asserted.

Note: RESET\_REG\_0 register writes do not support Auto-Increment mode.

## 4.11 Gennum Serial Peripheral Interface (GSPI)

The Gennum Serial Peripheral Interface (GSPI) is comprised of a serial data input signal (SDIN pin), serial data output signal (SDOUT pin), an active-low chip select ( $\overline{CS}$  pin) and a burst clock (SCLK pin).

The GS3140 is a slave device, so the SCLK, SDIN and  $\overline{CS}$  signals must be sourced by the application host processor.

All read and write access to the device is initiated and terminated by the application host processor.

## 4.11.1 CS Pin

The Chip Select pin  $\overline{(CS)}$  is an active-low signal provided by the host processor to the GS3140.

The high-to-low transition of this pin marks the start of serial communication to the GS3140.

The low-to-high transition of this pin marks the end of serial communication to the GS3140.

There is an option for each device to use a separate unique chip select signal from the host processor or for up to 32 devices to be connected to a single chip select when making use of the Unit Address feature.

Only those devices whose Unit Address matches the UNIT ADDRESS in the GSPI Command Word will respond to communication from the host processor (unless the B'CAST ALL bit in the GSPI Command Word is set to 1).

### 4.11.2 SDIN Pin

The SDIN pin is the GSPI serial data input pin of the GS3140.

16-bit Command and Data Words from the host processor or from the SDOUT pin of other devices are shifted into the device on the rising edge of SCLK when the  $\overline{CS}$  pin is low.

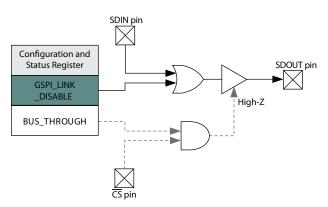

### 4.11.3 SDOUT Pin

The SDOUT pin is the GSPI serial data output of the GS3140.

All data transfers out of the GS3140 to the host processor or to the SDIN pin of other connected devices occur from this pin.

By default at power up or after system reset, the SDOUT pin provides a non-clocked path directly from the SDIN pin, regardless of the  $\overline{CS}$  pin state, except during the GSPI Data Word portion for read operations to the device. This allows multiple devices to be connected in Loop-Through configuration.

For read operations, the SDOUT pin is used to output data read from an internal Configuration and Status Register (CSR) when  $\overline{CS}$  is LOW. Data is shifted out of the device on the falling edge of SCLK, so that it can be read by the host processor or other downstream connected device on the subsequent SCLK rising edge.

### 4.11.3.1 GSPI Link Disable Operation

It is possible to disable the direct SDIN to SDOUT (Loop-Through) connection by writing a value of 1 to the GSPI\_LINK\_DISABLE bit in HOST\_CONF\_REG\_0. When disabled, any data appearing at the SDIN pin will not appear at the SDOUT pin and the SDOUT pin is HIGH.

**Note:** Disabling the Loop-Through operation is temporarily required when initializing the Unit Address for up to 32 connected devices.

The time required to enable/disable the Loop-Through operation from assertion of the register bit is less than the GSPI configuration command delay as defined by the parameter  $t_{cmd\_GSPI\_config}$  (4 SCLK cycles).

### Table 4-4: GSPI\_LINK\_DISABLE Bit Operation

| Bit State | Description                                                             |

|-----------|-------------------------------------------------------------------------|

| 0         | SDIN pin is looped through to the SDOUT pin                             |

| 1         | Data appearing at SDIN does not appear at SDOUT, and SDOUT pin is HIGH. |

Figure 4-4: GSPI\_LINK\_DISABLE Operation

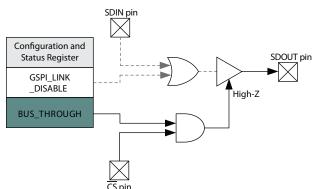

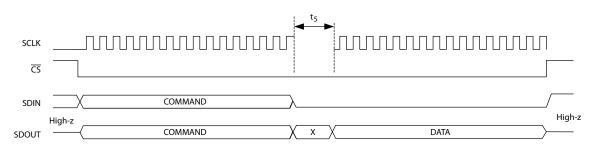

### 4.11.3.2 GSPI Bus-Through Operation

Using GSPI Bus-Through operation, the GS3140 can share a common PCB trace with other GSPI devices for SDOUT output.

When configured for Bus-Through operation, by setting the

GSPI\_BUS\_THROUGH\_ENABLE bit to 1, the SDOUT pin will be high-impedance when the CS pin is HIGH.

When the  $\overline{\text{CS}}$  pin is LOW, the SDOUT pin will be driven and will follow regular read and write operation as described in Section 4.11.3.

Multiple chains of GS3140 devices can share a single SDOUT bus connection to host by configuring the devices for Bus-Through operation. In such configuration, each chain requires a separate Chip Select ( $\overline{CS}$ ).

Topin

Figure 4-5: GSPI\_BUS\_THROUGH\_ENABLE Operation

#### Table 4-5: GSPI\_BUS\_THROUGH\_ENABLE Bit Operation

| Bit State | Description                                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0         | Disables Bus-Through operation                                                                                                      |

| 1         | Enables Bus-Through operation<br>When CS is HIGH, the SDOUT pin will be high impedance.<br>When CS is LOW, the SDOUT pin is driven. |

### 4.11.4 SCLK Pin

The SCLK pin is the GSPI serial data shift clock input to the device, and must be provided by the host processor.

Serial data is clocked into the GS3140 SDIN pin on the rising edge of SCLK. Serial data is clocked out of the device from the SDOUT pin on the falling edge of SCLK (read operation). SCLK is ignored when  $\overline{CS}$  is HIGH.

The maximum interface clock rate is 32MHz.

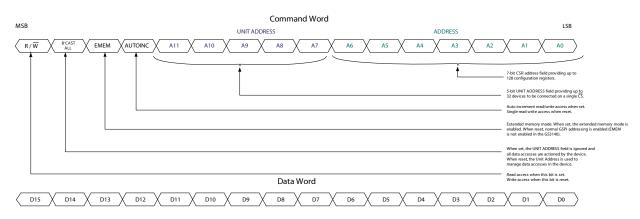

### 4.11.5 Command Word Description

All GSPI accesses are a minimum of 32 bits in length (a 16-bit Command Word followed by a 16-bit Data Word) and the start of each access is indicated by the high-to-low transition of the chip select ( $\overline{\text{CS}}$ ) pin of the GS3140.

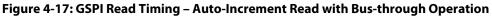

The format of the Command Word and Data Words are shown in Figure 4-6.

Data received immediately following this high-to-low transition will be interpreted as a new Command Word.

#### 4.11.5.1 R/W bit - B15 Command Word

This bit indicates a read or write operation.

When R/W is set to 1, a read operation is indicated, and data is read from the register specified by the ADDRESS field of the Command Word.

When R/W is set to 0, a write operation is indicated, and data specified in the Data Word is written to the register specified by the ADDRESS field of the Command Word.

### 4.11.5.2 B'CAST ALL - B14 Command Word

This bit is used in write operations to configure all devices connected in Loop-Through and Bus-Through configuration with a single command.

When B'CAST ALL is set to 1, the following Data Word (AUTOINC = 0) or Data Words (AUTOINC = 1) are written to the register specified by the ADDRESS field of the Command Word (and subsequent addresses when AUTOINC = 1), regardless of the setting of the UNIT ADDRESS(es).

When B'CAST ALL is set to 0, a normal write operation is indicated. Only those devices that have a Unit Address matching the UNIT ADDRESS field of the Command Word write the Data Word to the register specified by the ADDRESS field of the Command Word. B'CAST ALL must be set to 0 for read operations.

#### 4.11.5.3 EMEM - B13 Command Word

The EMEM bit should be set to 0 when accessing GS3140. Accesses to other devices (Unit Address field in the Command Word does not match the DEVICE\_UNIT\_ADDRESS in HOST\_CONF\_REG\_0) with EMEM bit set to 1 are allowed.

### 4.11.5.4 AUTOINC - B12 Command Word

When AUTOINC is set to 1, Auto-Increment read or write access is enabled.

In Auto Increment Mode, the device automatically increments the register address for each contiguous read or write access, starting from the address defined in the ADDRESS field of the Command Word.

The internal address is incremented for each 16-bit read or write access until a low-to-high transition on the  $\overline{CS}$  pin is detected.

When AUTOINC is set to 0, single read or write access is required.

Auto-Increment write must not be used to update values in HOST\_CONF\_REG\_0.

#### 4.11.5.5 UNIT ADDRESS - B11:B7 Command Word

The 5 bits of the UNIT ADDRESS field of the Command Word are used to select one of 32 devices connected on a single chip select in Loop-Through or Bus-Through configurations.

Read and write accesses are only accepted if the UNIT ADDRESS field matches the programmed DEVICE\_UNIT\_ADDRESS in HOST\_CONF\_REG\_0

By default at power-up or after a device reset, the DEVICE\_UNIT\_ADDRESS is set to 00<sub>h</sub>

#### 4.11.5.6 ADDRESS - B6:B0 Command Word

The 7 bits of the ADDRESS field are used to select one of the register addresses in the device in single read or write access mode, or to set the starting address for read or write accesses in Auto-Increment Mode.

Figure 4-6: Command and Data Word Format

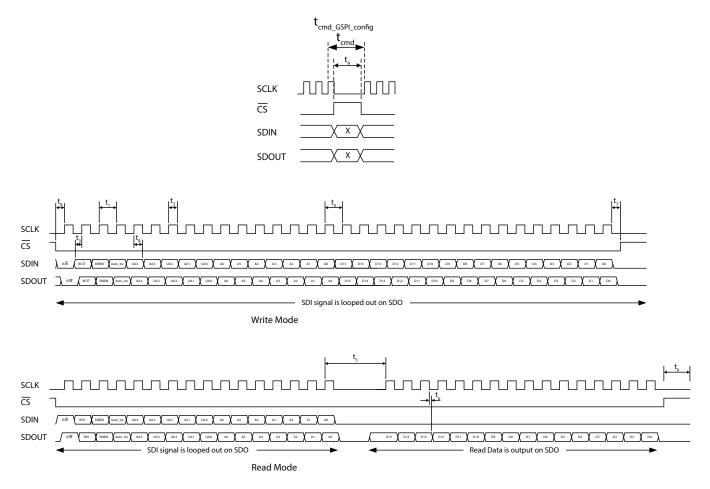

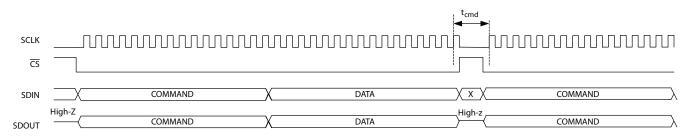

### 4.11.6 GSPI Transaction Timing

Figure 4-7: GSPI External Interface Timing

#### **Table 4-6: GSPI Timing Parameters**

| Parameter                                                 | Symbol                       | Equivalent<br>SCLK Cycles | Min                | Тур | Мах | Units |

|-----------------------------------------------------------|------------------------------|---------------------------|--------------------|-----|-----|-------|

| SCLK frequency                                            |                              |                           | _                  | _   | 32  | MHz   |

| CS low before SCLK rising edge                            | t <sub>0</sub>               |                           | 1.3                | —   | —   | ns    |

| SCLK period                                               | t <sub>1</sub>               |                           | 31.25              | _   |     | ns    |

| SCLK duty cycle                                           | t <sub>2</sub>               |                           | 40                 | 50  | 60  | %     |

| Input data setup time                                     | t <sub>3</sub>               |                           | 1.1                | _   |     | ns    |

| SCLK idle time -write                                     | t <sub>4</sub>               | 1                         | 31.25 <sup>1</sup> | _   |     | ns    |

| SCLK idle time - read                                     | t <sub>5</sub>               | 4                         | 114                | _   | _   | ns    |

| Inter-command delay time                                  | t <sub>cmd</sub>             | 3                         | 85                 |     |     |       |

| Inter-command delay time (after GSPI configuration write) | t <sub>cmd_GSPI_conf</sub> 2 | 4                         | 114                | _   | _   | ns    |

#### Table 4-6: GSPI Timing Parameters (Continued)

| Parameter                                                   | Symbol                                                 | Equivalent<br>SCLK Cycles | Min  | Тур | Мах | Units           |

|-------------------------------------------------------------|--------------------------------------------------------|---------------------------|------|-----|-----|-----------------|

| SDO after SCLK falling edge                                 | t <sub>6</sub>                                         |                           | 1.9  | _   | 7.5 | ns              |

| CS high after final SCLK falling edge                       | t <sub>7</sub>                                         |                           | 0    | _   | _   | ns              |

| Input data hold time                                        | t <sub>8</sub>                                         |                           | 1    | —   | —   | ns              |

| CS high time                                                | t <sub>9</sub>                                         |                           | 46.9 | _   | _   | ns              |

| SDIN to SDOUT combinatorial delay                           |                                                        |                           | _    | _   | 5   | ns              |

| Max. chips daisy chained at max<br>SCLK frequency (32 MHz)  | When host                                              | clocks in SDOUT           | _    | _   | 1   | GS3140<br>chips |

| Max. frequency for 32<br>daisy-chained devices              | data on rising edge of SCLK                            |                           | _    | _   | 2.1 | MHz             |

| Max. chips daisy-chained at max.<br>SCLK frequency (32 Mhz) | When host clocks in SDOUT data on falling edge of SCLK |                           | _    | _   | 3   | GS3140<br>chips |

| Max. frequency for 32<br>daisy-chained devices              |                                                        |                           |      | _   | 2.2 | MHz             |

#### Notes:

1. Parameter is an exact multiple of SCLK periods and scales proportionally

2. t<sub>cmd\_GSPI\_conf</sub> inter-command delay must be used whenever modifying HOST\_CONF\_REG\_0 register at address 0x00

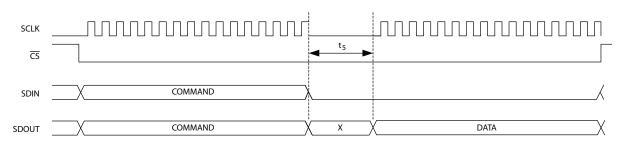

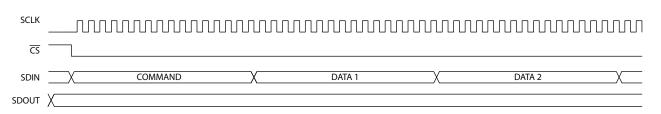

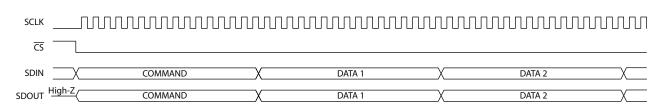

### 4.11.7 Single Read/Write Access

Single read/write access timing for the GSPI interface is shown in Figure 4-8 to Figure 4-12.

When performing a single read or write access, one Data Word is read from/written to the device per access. Each access is a minimum of 32-bits long, consisting of a Command Word and a single Data Word. The read or write cycle begins with a high-to-low transition of the  $\overline{CS}$  pin. The read or write access is terminated by a low-to-high transition of the  $\overline{CS}$  pin.

The maximum interface clock rate is 32MHz and the inter-command delay time indicated in the figures as  $t_{cmd}$ , is a minimum of 3 SCLK clock cycles. After modifying values in HOST\_CONF\_REG\_0, the inter-command delay time,  $t_{cmd_GSPl_config}$ , is a minimum of 4 SCLK clock cycles.

For read access, the time from the last bit of the Command Word to the start of the data output, as defined by  $t_5$ , corresponds to no less than 4 SCLK clock cycles at 32MHz.

Figure 4-8: GSPI Write Timing – Single Write Access with Loop-Through Operation (default)

Figure 4-9: GSPI Write Timing – Single Write Access with GSPI Link-Disable Operation

Figure 4-10: GSPI Write Timing – Single Write Access with Bus-Through Operation

Figure 4-11: GSPI Read Timing – Single Read Access with Loop-Through Operation (default)

www.semtech.com

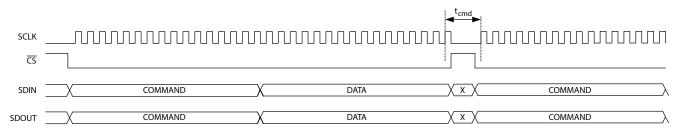

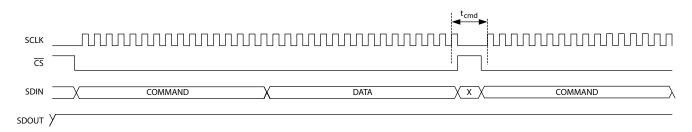

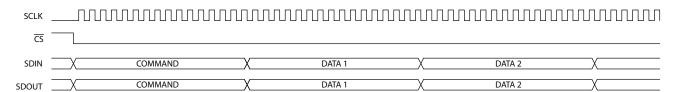

### 4.11.8 Auto-increment Read/Write Access

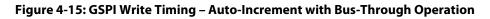

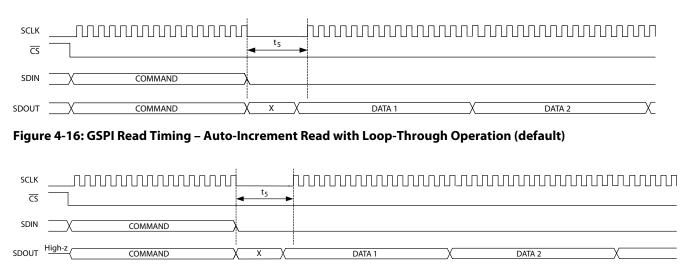

Auto-increment read/write access timing for the GSPI interface is shown in Figure 4-13 to Figure 4-17.

Auto-increment mode is enabled by the setting of the AUTOINC bit of the Command Word.

In this mode, multiple Data Words can be read from/written to the device using only one starting address. Each access is initiated by a high-to-low transition of the  $\overline{CS}$  pin, and consists of a Command Word and one or more Data Words. The internal address is automatically incremented after the first read or write Data Word, and continues to increment until the read or write access is terminated by a low-to-high transition of the  $\overline{CS}$  pin.

**Note:** Writing to HOST\_CONF\_REG\_0 using Auto-increment access is not allowed.

The maximum interface clock rate is 32MHz and the inter-command delay time indicated in the diagram as  $t_{cmd}$ , is a minimum of 3 SCLK clock cycles.

For read access, the time from the last bit of the first Command Word to the start of the data output of the first Data Word as defined by  $t_5$ , will be no less than 4 SCLK cycles at 32MHz. All subsequent read data accesses will not be subject to this delay during an Auto-Increment read.

Figure 4-13: GSPI Write Timing – Auto-Increment with Loop-Through Operation (default)

#### Figure 4-14: GSPI Write Timing – Auto-Increment with GSPI Link Disable Operation

### 4.11.9 Default GSPI Operation

By default at power up or after a device reset, the GS3140 is set for Loop-Through Operation and the internal DEVICE\_UNIT\_ADDRESS field of the device is set to 0.

Figure 4-18 shows a functional block diagram of the Configuration and Status Register (CSR) map in the GS3140.

#### Figure 4-18: Internal Register Map Functional Block Diagram

The steps required for the application host processor to write to the Configuration and Status Registers via the GSPI, are as follows:

- 1. Set Command Word for write access (R/W = 0) and desired Local Address (register address); set Auto Increment; set the Unit Address field in the Command Word to match the configured DEVICE\_UNIT\_ADDRESS which will be zero. Write the Command Word.

- 2. Write the Data Word to be written to the first addressed register.

- 3. Write the Data Word to be written to the next register in Auto Increment mode, etc.

Read access is the same as the above except in step 1 the Command Word is set for read access ( $R/\overline{W} = 1$ ).

**Note:** The UNIT ADDRESS field of the Command Word must always match DEVICE\_UNIT\_ADDRESS for an access to be accepted by the device. Changing DEVICE\_UNIT\_ADDRESS to a value other than 0 is only required if multiple devices are connected to a single chip select (in Loop-Through or Bus-Through configuration).

### 4.11.10 Setting a Device Unit Address

Multiple (up to 32) GS3140 devices can be connected to a common Chip Select ( $\overline{CS}$ ) in Loop-Through or Bus-Through operation.

To ensure that each device selected by a common  $\overline{CS}$  can be separately addressed, a unique Unit Address must be programmed by the host processor at start-up as part of system initialization or following a device reset.

**Note:** By default at power up or after a device reset, the DEVICE\_UNIT\_ADDRESS of each device is set to 0h and the SDIN  $\rightarrow$  SDOUT non-clocked loop-through for each device is enabled.

These are the steps required to set the DEVICE\_UNIT\_ADDRESS of devices in a chain to values other than 0:

- Write to Unit Address 0 selecting HOST\_CONF\_REG\_0 (ADDRESS = 0), with the GSPI\_LINK\_DISABLE bit set to 1 and the DEVICE\_UNIT\_ADDRESS field set to 0. This disables the direct SDIN → SDOUT non-clocked path for all devices on chip select.

- 2. Write to Unit Address 0 selecting HOST\_CONF\_REG\_0 (ADDRESS = 0), with the GSPI\_LINK\_DISABLE bit set to 0 and the DEVICE\_UNIT\_ADDRESS field set to a unique Unit Address. This configures DEVICE\_UNIT\_ADDRESS for the first device in the chain. Each subsequent such write to Unit Address 0 will configure the next device in the chain. If there are 32 devices in a chain, the last (32nd) device in the chain must use DEVICE\_UNIT\_ADDRESS value 0.

- 3. Repeat step 2 using new, unique values for the DEVICE\_UNIT\_ADDRESS field in HOST\_CONF\_REG\_0 until all devices in the chain have been configured with their own unique Unit Address value.

**Note:** t<sub>cmd\_GSPl\_conf</sub> delay must be observed after every write that modifies HOST\_CONFIG\_REG\_0.

All connected devices receive this command (by default the Unit Address of all devices is 0), and the Loop-Through operation will be re-established for all connected devices.

Once configured, each device will only respond to Command Words with a UNIT ADDRESS field matching the DEVICE\_UNIT\_ADDRESS in HOST\_CONF\_REG\_0

**Note:** Although the Loop-Through and Bus-Through configurations are compatible with previous generation GSPI enabled devices (backward compatibility), only devices supporting Unit Addressing can share a chip select. All devices on any single chip select must be connected in a contiguous chain with only the last device's SDOUT connected to the application host processor. Multiple chains configured in Bus-Through mode can have their final SDOUT outputs connected to a single application host processor input.

# 5. Host Interface Register Map

#### Table 5-1: Register Descriptions

| Address        | Register Name   | Parameter Name                 | Bit<br>Slice | R/W | Reset            | Description                                                                                                                                                                      |

|----------------|-----------------|--------------------------------|--------------|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                 | RSVD                           | 15:15        | RW  | 0 <sub>h</sub>   | Reserved. Do not change.                                                                                                                                                         |

|                |                 | GSPI_LINK_DISABLE              | 14:14        | RW  | 0 <sub>h</sub>   | GSPI loop-through disable.                                                                                                                                                       |

| 0 <sub>h</sub> | HOST_CONF_REG_0 | GSPI_BUS_THROUGH_ENABLE        | 13:13        | RW  | 0 <sub>h</sub>   | GSPI bus-through enable.                                                                                                                                                         |

|                |                 | RSVD                           | 12:5         | RW  | 0 <sub>h</sub>   | Reserved. Do not change.                                                                                                                                                         |

|                |                 | DEVICE_UNIT_ADDRESS            | 4:0          | RW  | 0 <sub>h</sub>   | Device address programmed by application.                                                                                                                                        |

|                |                 | RSVD                           | 15:9         | RW  | 0 <sub>h</sub>   | Reserved. Do not change.                                                                                                                                                         |

|                |                 |                                |              |     |                  | Manually specify maximum cable<br>length:<br>00 <sub>b</sub> = 100m                                                                                                              |

|                | EQ_CONF_REG_0   | MAX_CABLE_LENGTH_CONFIG        | 8:7          | RW  | ' 3 <sub>h</sub> | $01_{b} = 200m$<br>$10_{b} = 300m$<br>$11_{b} = 600m$                                                                                                                            |

|                |                 | AUTO_BYPASS                    | 6:6          | RW  | 0 <sub>h</sub>   | Enable automatic assertion of<br>bypass (equivalent to BYPASS=1)<br>when an input signal is detected<br>with a rate below MADI.                                                  |

| 1 <sub>h</sub> |                 | BYPASS                         | 5:5          | RW  | 0 <sub>h</sub>   | Forces the equalizer core and<br>DC-restore into Bypass mode when<br>set to 1. No equalization occurs in<br>this mode.                                                           |

|                |                 | RSVD                           | 4:4          | RW  | 0 <sub>h</sub>   | Reserved. Do not change.                                                                                                                                                         |

|                |                 | CUSTOM_DYN_PWR_MODE            | 3:3          | RW  | 0 <sub>h</sub>   | Enable Dynamic Power Mode.<br>Control bit overrides default when<br>CUSTOM_DYN_PWR_MODE_<br>ENABLE is set to 1.                                                                  |

|                |                 | CUSTOM_DYN_PWR_MODE_<br>ENABLE | 2:2          | RW  | 0 <sub>h</sub>   | When set to 1, overrides the<br>Dynamic Power Mode with value<br>specified by parameter<br>CUSTOM_DYN_PWR_MODE. When<br>set to 0 Dynamic Power Mode will<br>default to disabled. |

|                |                 | SLEEP                          | 1:0          | RW  | 0 <sub>h</sub>   | $00_b = Normal$<br>$01_b = Auto-Sleep$<br>$10_b$ , $11_b = Forced-Sleep$                                                                                                         |

| Address Register Name Pa                 | rameter Name             | Bit<br>Slice | R/W | Reset           | Description                                                                                                                                                                                                                                                                                                  |

|------------------------------------------|--------------------------|--------------|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | RSVD                     | 15:12        | RW  | 0 <sub>h</sub>  | Reserved. Do not change.                                                                                                                                                                                                                                                                                     |

| SDI_DA<br>2 <sub>h</sub> EQ_CONF_REG_1   | TA_RATE_VALUE            | 11:9         | RW  | 0 <sub>h</sub>  | When enabled by<br>FORCE_SDI_DATA_RATE_VALUE.<br>$000_b =$ Force <madi operation<br="" rates=""><math>001_b =</math> Force MADI rates operation<br/><math>010_b =</math> Force SD rates operation<br/><math>011_b =</math> Force HD rates operation<br/><math>100_b =</math> Force 3G rates operation</madi> |

|                                          | _DATA_RATE_VALUE         | 8:8          | RW  | 0 <sub>h</sub>  | Forces the device to operate<br>assuming incoming signal is at rate<br>specified by<br>SDI_DATA_RATE_VALUE.                                                                                                                                                                                                  |

| SQUEL                                    | CH_THRESHOLD             | 7:0          | RW  | FF <sub>h</sub> | Squelch Threshold<br>ED <sub>h</sub> - FF <sub>h</sub> = No Squelch<br>0 <sub>h</sub> - EC <sub>h</sub> = See 4.4 Programmable<br>Squelch Threshold                                                                                                                                                          |

|                                          | RSVD                     | 15:8         | RW  | 0 <sub>h</sub>  | Reserved. Do not change.                                                                                                                                                                                                                                                                                     |

|                                          | NCH_SWING_<br>MPENSATION | 7:4          | RW  | B <sub>h</sub>  | Selects the upstream launch swing<br>compensation as described in<br>Section 4.1.1. Refer to Table 4-2 for<br>output swing values.                                                                                                                                                                           |

| MUTE_C                                   | DUTPUT_IN_SLEEP          | 3:3          | RW  | 0 <sub>h</sub>  | Enables driving outputs in MUTE mode when core is in SLEEP, as explained in Section 4.8.4.                                                                                                                                                                                                                   |

| 3 <sub>h</sub> EQ_CONF_REG_2<br>MADI_AUT | O_SWING_DISABLE          | 2:2          | RW  | 0 <sub>h</sub>  | Disables MADI automatic swing<br>support.<br>if the MADI signal swing is more<br>tightly known, the equalizer jitter<br>and reach performance can be<br>significantly improved by disabling<br>this mode and using the<br>LAUNCH_SWING_COMPENSATION<br>register bits to specify the swing.                   |

|                                          | RSVD                     | 1:0          | RW  | 0 <sub>h</sub>  | Reserved. Do not change.                                                                                                                                                                                                                                                                                     |

| Address        | Register Name  | Parameter Name                | Bit<br>Slice      | R/W | Reset                                                                                              | Description                                                                                                                                                                                                                                                  |                                                                                                                                                            |

|----------------|----------------|-------------------------------|-------------------|-----|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                | RSVD                          | 15:15             | RW  | 0 <sub>h</sub>                                                                                     | Reserved. Do not change.                                                                                                                                                                                                                                     |                                                                                                                                                            |

|                |                | OUTPUT_SWING                  | 14:11             | RW  | B <sub>h</sub>                                                                                     | Sets the output swing level<br>(amplitude) when the feature is<br>enabled. See Section 4.9.1.                                                                                                                                                                |                                                                                                                                                            |

| 4 <sub>h</sub> | OUT_CONF_REG_0 | OUTPUT_SWING_ENABLE           | 10:10             | RW  | v 0 <sub>h</sub>                                                                                   | When set to 1, enables overriding<br>of the default output swing with<br>the value written in the<br>OUTPUT_SWING bits.                                                                                                                                      |                                                                                                                                                            |

|                |                |                               |                   |     | When set to 0, the output swing<br>will default to a setting of<br>OUTPUT_SWING = B <sub>h</sub> . |                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                |                | DEEMPHASIS_DELAY              | 9:9               | RW  | 0 <sub>h</sub>                                                                                     | Set the de-emphasis delay when<br>DEEMPHASIS_ENABLE is set to 1.<br>$0_b = 100ps$<br>$1_b = 200ps$                                                                                                                                                           |                                                                                                                                                            |

| 4 <sub>h</sub> | OUT_CONF_REG_0 | DEEMPHASIS_LEVEL              | 8:6               | RW  | 0 <sub>h</sub>                                                                                     | Set the de-emphasis level when<br>DEEMPHASIS_ENABLE is set to 1.<br>See Table 4-3.                                                                                                                                                                           |                                                                                                                                                            |

|                |                | RSVD                          | 5:2               | RW  | 0 <sub>h</sub>                                                                                     | Reserved. Do not change.                                                                                                                                                                                                                                     |                                                                                                                                                            |

| 4 <sub>h</sub> | OUT_CONF_REG_0 | 4 <sub>h</sub> OUT_CONF_REG_0 | DEEMPHASIS_ENABLE | 1:1 | RW                                                                                                 | 0 <sub>h</sub>                                                                                                                                                                                                                                               | Enable or disable the de-emphasis<br>delay and level set using the<br>DEEMPHASIS_DELAY and<br>DEEMPHASIS_LEVEL bits.<br>$0_{\rm b}$ = De-emphasis disabled |

|                |                |                               |                   |     |                                                                                                    | 1 <sub>b</sub> = De-emphasis enabled                                                                                                                                                                                                                         |                                                                                                                                                            |

|                |                | RSVD                          | 0:0               | RW  | 0 <sub>h</sub>                                                                                     | Reserved. Do not change.                                                                                                                                                                                                                                     |                                                                                                                                                            |

|                |                | RSVD                          | 15:3              | RW  | 0 <sub>h</sub>                                                                                     | Reserved. Do not change.                                                                                                                                                                                                                                     |                                                                                                                                                            |

|                |                | MANUAL_OUTPUT_DISABLE         | 2:2               | RW  | 0 <sub>h</sub>                                                                                     | When set to 1, powers down the output buffer.                                                                                                                                                                                                                |                                                                                                                                                            |

| 5 <sub>h</sub> | OUT_CONF_REG_1 | AUTO_OUTPUT_MUTE              | 1:1               | RW  | 0 <sub>h</sub>                                                                                     | Enable automatic muting of the<br>output buffer (equivalent to<br>setting MUTE = 1) when LOS is<br>asserted (set to 1).                                                                                                                                      |                                                                                                                                                            |