# A6932H1.2

## 2 A ULDO linear regulator for automotive applications

#### Datasheet - production data

### Features

- AEC-Q100 compliant

- 2 V to 14 V input voltage range

- 200 mΩ R<sub>DS(on)</sub> max.

- 200 µA quiescent current at any load

- Excellent load and line regulation

- Adjustable from 1.2 V to 5 V

- 1% voltage regulation accuracy

- Short-circuit protection

- Thermal shutdown

- HSOP-8 package

## Applications

• Dedicated to automotive applications

## Description

The A6932H1.2 ultra low drop output linear regulator operates from 2 V to 14 V and is able to support output current up to 2 A. Designed with an internal 50 m $\Omega$  N-channel MOSFET, it can be used for on-board DC-DC conversions saving in real estate, list of components, low noise generation and power dissipation.

The A6932H1.2 device is available as adjustable version from 1.2 V to 5 V with a voltage regulation accuracy of 1%.

The upper current limit is fixed at 2.5 A to control the current in short-circuit condition within  $\pm$  8%. The current is sensed in the power MOS in order to limit the power dissipation.

The device is also provided with a thermal shutdown that limits the internal temperature at 150 °C with a hysteresis of 20 °C. The A6932H1.2 device provides the enable and the Power Good functions.

### Table 1. Device summary

| Part number | Package | Packaging     |

|-------------|---------|---------------|

| A6932H1.2   | HSOP-8  | Tube          |

| A6932H1.2TR | HSOP-8  | Tape and reel |

DocID025613 Rev 1

1/14

# Contents

| 1 | Pin settings                     |

|---|----------------------------------|

|   | 1.1 Pin connection               |

|   | 1.2 Pin description              |

| 2 | Maximum ratings                  |

|   | 2.1 Absolute maximum ratings 4   |

|   | 2.2 Thermal data                 |

| 3 | Block diagram                    |

| 4 | Electrical characteristics 5     |

| 5 | Typical electrical performance 6 |

| 6 | Application information7         |

|   | 6.1 Application circuit          |

|   | 6.2 Demonstration board layout   |

|   | 6.3 Component part list 8        |

| 7 | Component selection              |

|   | 7.1 Input capacitor              |

|   | 7.2 Output capacitor 9           |

|   | 7.3 Loop stability               |

| 8 | Package information              |

| 9 | Revision history                 |

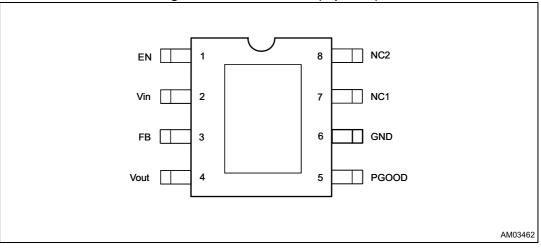

# 1 Pin settings

## **1.1 Pin connection**

### Figure 2. Pin connection (top view)

## 1.2 Pin description

### Table 2. Pin description

| Name | Pin no.   | Description                                                                                                                                                  |  |  |

|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | EN        | Enables the device when connected to Vin and disables it when forced to GND.                                                                                 |  |  |

| 2    | VIN       | Supply voltage. This pin is connected to the drain of the internal N-MOS. Connect this pin to a capacitor larger than 10 $\mu$ F.                            |  |  |

| 3    | FB        | Connecting this pin to a voltage divider it is possible to program the output voltage between 1.2 V and 5 V.                                                 |  |  |

| 4    | VOUT      | Regulated output voltage. This pin is connected to the source of the internal N-MOS. Connect this pin to a capacitor of 10 $\mu\text{F}.$                    |  |  |

| 5    | PGOOD     | Power Good output. The pin is open drain and detects the output voltage. It is forced low if the output voltage is lower than 90% of the programmed voltage. |  |  |

| 6    | GND       | Ground pin                                                                                                                                                   |  |  |

| 7, 8 | NC1 - NC2 | Internally not connected.                                                                                                                                    |  |  |

#### 2 **Maximum ratings**

#### 2.1 Absolute maximum ratings

| Table 3. | Absolute | maximum | ratings |

|----------|----------|---------|---------|

|----------|----------|---------|---------|

| Symbol          | Parameter       | Value              | Unit |

|-----------------|-----------------|--------------------|------|

| V <sub>IN</sub> | VIN and PGOOD   | 14.5               | V    |

|                 | EN, OUT and ADJ | -0.3 to (Vin +0.3) | V    |

#### 2.2 **Thermal data**

### Table 4. Thermal data

| Symbol            | Parameter                                   | Value             | Unit |

|-------------------|---------------------------------------------|-------------------|------|

| R <sub>thJA</sub> | Maximum thermal resistance junction ambient | 34 <sup>(1)</sup> | °C/W |

| T <sub>MAX</sub>  | Maximum junction temperature                | 150               | °C   |

| T <sub>STG</sub>  | Storage temperature range                   | -65 to 150        | °C   |

1. Package mounted on board.

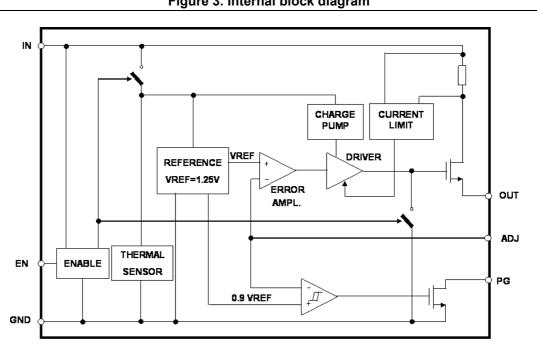

#### **Block diagram** 3

### Figure 3. Internal block diagram

DocID025613 Rev 1

# 4 Electrical characteristics

## Table 5. Electrical characteristics ( $T_a$ = -40 °C to 85 °C, $V_{IN}$ = 5 V unless otherwise specified)

| Symbol              | Parameter                  | Test condition                                                     | Min.  | Тур. | Max.  | Unit |

|---------------------|----------------------------|--------------------------------------------------------------------|-------|------|-------|------|

| V <sub>IN</sub>     | Operating supply voltage   |                                                                    | 2     |      | 14    | V    |

| N/                  | Output voltage             | T <sub>a</sub> = 25 °C                                             | 1.188 | 1.2  | 1.212 | v    |

| V <sub>O</sub>      | Output voltage             |                                                                    | 1.175 |      | 1.212 | v    |

|                     |                            | V <sub>IN</sub> = 2.5 V ± 10%; I <sub>O</sub> = 10 mA              |       |      | 5     | mV   |

|                     | Line regulation            | V <sub>IN</sub> = 3.3 V ± 10%; I <sub>O</sub> = 10 mA              |       |      | 5     | mV   |

|                     |                            | V <sub>IN</sub> = 5 V ± 10%; I <sub>O</sub> = 10 mA                |       |      | 5     | mV   |

|                     | Load regulation            | V <sub>IN</sub> = 3.3 V; 0.1 A < I <sub>O</sub> < 2 A              |       |      | 15    | mV   |

| R <sub>DS(on)</sub> | Drain source ON resistance |                                                                    |       |      | 200   | mΩ   |

|                     | Current limiting           | T <sub>a</sub> = 25 °C                                             | 2.3   | 2.5  | 2.7   | A    |

| locc                |                            |                                                                    |       |      | 2.85  |      |

| lq                  | Quiescent current          |                                                                    |       | 0.2  | 0.4   | mA   |

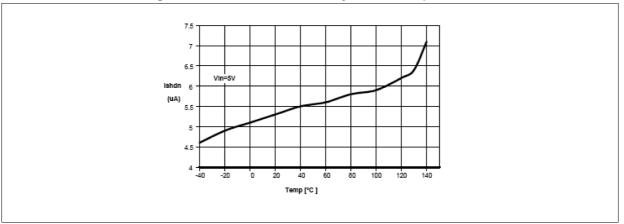

| lsh                 | Ohuddaum aumant            | T <sub>a</sub> = 25 °C                                             |       |      | 25    |      |

| ISH                 | Shutdown current           |                                                                    |       |      | 29    | μA   |

|                     | Ripple rejection           | f = 120 Hz, $I_0$ = 1 A $V_{IN}$ = 5 V,<br>$\Delta V_{IN}$ = 2 Vpp | 60    | 75   |       | dB   |

| Ven                 | EN input threshold         |                                                                    | 0.5   | 0.65 | 0.8   | V    |

|                     | Pgood threshold            | Vo rise                                                            |       | 90   |       | %Vo  |

|                     | Pgood hysteresis           |                                                                    |       | 10   |       | %Vo  |

|                     | Pgood saturation           | lpgood = 1 mA                                                      |       | 0.2  | 0.4   | V    |

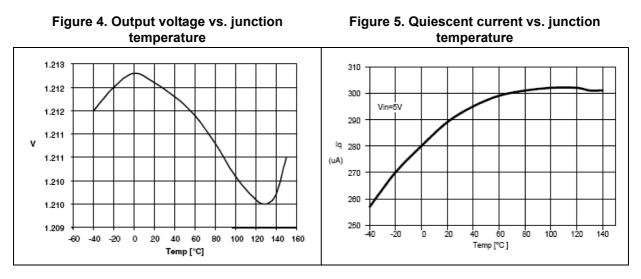

# 5 Typical electrical performance

# 6 Application information

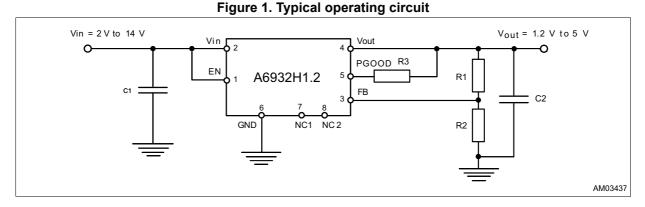

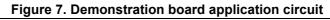

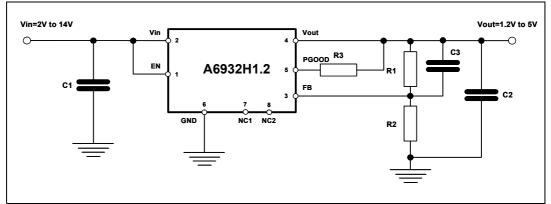

## 6.1 Application circuit

Equation 1

$$V_{OUT} = \frac{1.2}{R_2} \times (R_1 + R_2)$$

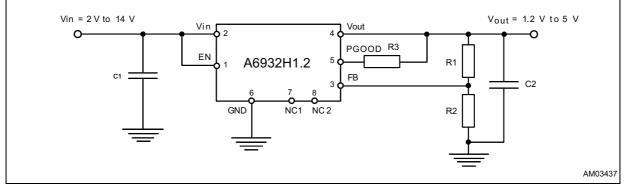

## 6.2 Demonstration board layout

### Figure 8. Demonstration board layout

DocID025613 Rev 1

# 6.3 Component part list

| Reference | Part number       | ber Description Manufacturer |        |

|-----------|-------------------|------------------------------|--------|

| C1        | GRM32ER6C226KE20B | 22 μF, 16 V                  | Murata |

| C2        | GRM32ER6C226KE20B | 22 μF, 16 V                  | Murata |

| R1        |                   | N. M.                        |        |

| R2        |                   | 0 Ω                          |        |

| R3        |                   | 100 KΩ                       |        |

## 7 Component selection

## 7.1 Input capacitor

The input capacitor value depends on a lot of factors such as load transient requirements, input source (battery or DC/DC converter) and its distance from the input cap. Usually a 47  $\mu F$  is enough for any application but a much lower value can be sufficient in many cases.

## 7.2 Output capacitor

The output capacitor choice depends basically on the load transient requirements. Tantalum, Special Polymer, POSCAP and aluminum capacitors are good and offer very low ESR values. Multilayer ceramic caps have the lowest ESR and can be required for particular applications. Nevertheless in several applications they are OK, the loop stability issue has to be considered (see loop stability section).

In *Table 7* is a list of some suggested capacitor manufacturers.

| Manufacturer | Туре     | Cap value (µF) | Rated voltage (V) |

|--------------|----------|----------------|-------------------|

| Murata       | Ceramic  | 1 to 47        | 4 to 16           |

| Panasonic    | Ceramic  | 1 to 47        | 4 to 16           |

| TAIYO YUDEN  | Ceramic  | 1 to 47        | 4 to 16           |

| TDK          | Ceramic  | 1 to 47        | 4 to 16           |

| TOKIN        | Ceramic  | 1 to 47        | 4 to 16           |

| SANYO        | POSCAP   | 1 to 47        | 4 to 16           |

| Panasonic    | SP       | 1 to 47        | 4 to 16           |

| KEMET        | Tantalum | 1 to 47        | 4 to 16           |

## 7.3 Loop stability

The stability of the loop is affected by the zero introduced by the output capacitor. The time constant of the zero is given by:

**Equation 2**

$$T = ESR \times C_{OUT}$$

### **Equation 3**

$$F_{ZERP} = \frac{1}{2\pi \times ESR \times C_{OUT}}$$

This zero helps to increase the phase margin of the loop until the time constant is higher than some hundreds of ns, depending also on the output voltage and current.

So, using very low ESR ceramic capacitors could produce oscillations at the output, in particular when regulating high output voltages (adjustable version).

To solve this issue is sufficient to add a small capacitor (e.g. 1 nF to 10 nF) in parallel to the high side resistor of the external divider, as shown in *Figure 9*.

Figure 9. Compensation network

The thermal resistance junction to ambient of the demonstration board is approximately 34  $^{\circ}\text{C/W}.$

This mean that, considering an ambient temperature of 60  $^{\circ}$ C and, a maximum junction temperature of 150  $^{\circ}$ C, the maximum power that the device can handle is 2.7 W.

This means that the device is able to deliver a DC output current of 2 A only with a very low dropout.

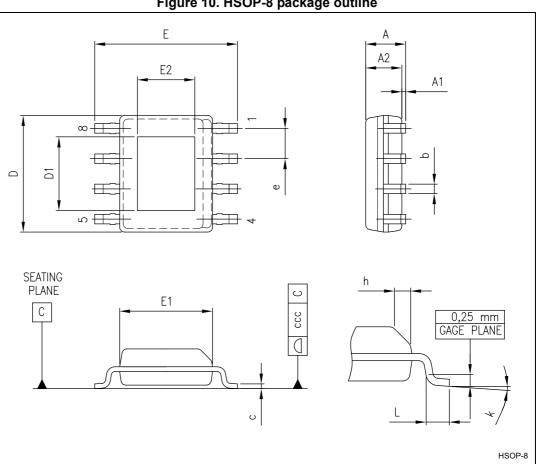

#### **Package information** 8

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

|        | Dimensions (mm) |                       |      |         |

|--------|-----------------|-----------------------|------|---------|

| Symbol | Min.            | Тур.                  | Max. | - Note  |

| А      | 1.43            | 1.55                  | 1.68 |         |

| A1     | 0.03            | 0.08                  | 0.13 |         |

| A2     | 1.40            | 1.47                  | 1.55 |         |

| b      | 0.35            | 0.41                  | 0.49 |         |

| С      | 0.19            | 0.20                  | 0.25 |         |

| D      | 4.80            | 4.93                  | 4.98 | (1)     |

| D1     | A               | ccording to pad size  |      | (2)     |

| E      | 5.84            | 5.99                  | 6.20 |         |

| E1     | 3.81            | 3.94                  | 3.99 | (3)     |

| E2     | A               | According to pad size | •    | (2)     |

| е      |                 | 1.27                  |      |         |

| h      | 0.25            | 0.33                  | 0.41 |         |

| L      | 0.41            | 0.64                  | 0.89 |         |

| k      | 0               | 5                     | 8    | Degrees |

| ссс    |                 |                       | 0.10 |         |

1. Dimension "D" does not include mold flash, protrusions or gate burrs.

2. The size of exposed pad is variable depending of leadframe design pad size. End user should verify "D1" and "E2" dimensions for each device application.

3. Dimension "E1" does not include interlead flash or protrusions. Interlead flash or protrusions shall not exceed 0.25 mm per side.

# 9 Revision history

| Table 9. | Document | revision | history |

|----------|----------|----------|---------|

|----------|----------|----------|---------|

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 29-Nov-2013 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

DocID025613 Rev 1