# PS22924 12V, 2A Fast Transient Response Linear Regulator Preliminary

Data Sheet 292205 issue 1

### **Features**

- V<sub>IN</sub> Range 1.7 12V

- Fixed and adjustable output voltage

- 2A maximum output current

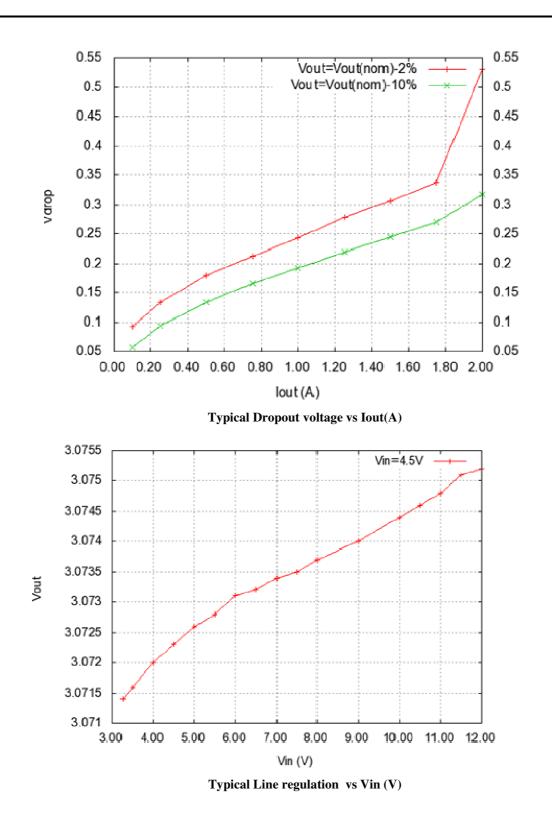

- 350mV typical dropout voltage

- Bypass output for low PSRR and output noise

- Power Good pin with 500µs delay

- Low self noise

- Shutdown mode for longer battery life

- High PSRR typically 60dB at 100Hz

- Stable with a wide range of Ceramic, Tantalum or Electrolytic capacitors

- Current limit protection

- Thermal Shutdown

- -40 ℃ to 125 ℃ temperature range

- Available in SOIC-8 package

## **Applications**

- Set Top Boxes

- Digital Audio systems

- DSP

- POL regulators

- SMPS post regulator

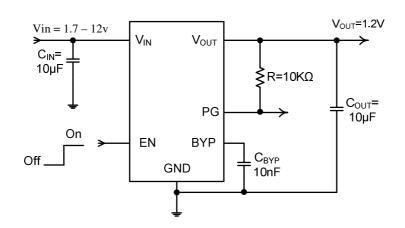

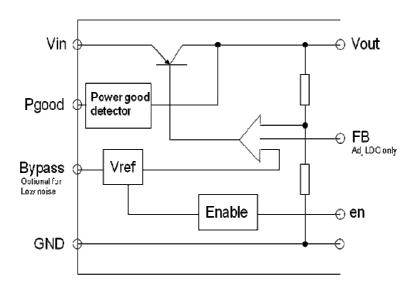

## **Typical Application**

## Description

The PS22924 is a high performance, precision linear regulator with very low dropout voltage and excellent transient response. It is designed to operate with wide input voltage range of 1.7 - 12 Volts making it ideal for two step conversion. The device is capable of supplying 2A of output current with a typical dropout voltage of 350mV. The output Voltage is available in either fixed or adjustable options. For fixed option, the internal resistor network can be set in 100mV increment ranging from 0.5 to 5.0 volts.

The product includes an Enable pin for electrical on/off of the regulator. Forcing the Enable pin to logic low shuts down the LDO and reduces the supply current below 1 $\mu$ A. The PS22924 features fast transient response and low self output noise. Connecting a capacitor form ByPass to GND further enhances the PSRR and the output noise.

An open collector power good flag with 500µs delay is available for systems requiring supply monitoring and sequencing of other supplies. The regulator features the full suite of protection with a combination of current limit and thermal overload protection.

The PS22924 is available in a thermally enhanced SOIC-8 EDP packages, and it is rated for -40  $^\circ\!C$  to +125  $^\circ\!C$  junction temperature range.

Plessey Semiconductors Ltd, Tamerton Road, Roborough, Plymouth, UK PL6 7BQ

Data Sheet 292205 issue 1

Tel: +44 (0)1752 693000

Fax: +44 (0)1752 693200

Web: www.plesseysemiconductors.com

email: sales@plesseysemi.com;

October 12, 2010

Veb: www.plesseysemiconductors.com

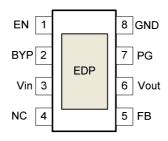

## **Pin Description**

| Symbol           | Pin<br>Number | Description                                                                                                                                                                                                                                                                                                                                                                     |  |

|------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EN               | 1             | Enable pin. It controls the electrical on/off of the device. When connected to logic low, the device shuts off and consumes $1\mu A$ of current. Logic high will resume normal operation.                                                                                                                                                                                       |  |

| ByPass           | 2             | Bypass pin. Connect an external capacitor from BYP to ground to bypass the noise generated by the internal bandgap. This improves power supply rejection ratio and output noise. A minimum capacitor of 220pF is recommended.                                                                                                                                                   |  |

| V <sub>IN</sub>  | 3             | Input supply pin. Connect a 10µF capacitor between this pin and ground.                                                                                                                                                                                                                                                                                                         |  |

| NC               | 4             | No connect.                                                                                                                                                                                                                                                                                                                                                                     |  |

| FB               | 5             | Feedback Voltage. For preset Vout devices an on-chip resistor network of two resistors is used to set-up the output voltage. In this case FB needs to be connected externally to Vout. For adjustable Vout devices the centre of an external resistive chain needs to be connected to this FB pin.                                                                              |  |

| V <sub>OUT</sub> | 6             | Regulated output Voltage. Connect a 10µF capacitor from this pin to ground.                                                                                                                                                                                                                                                                                                     |  |

| PG               | 7             | Power good. It is an open collector, active high output that indicates the status of the output voltage. When output voltage ( $V_{OUT}$ ) exceeds the PG trip threshold, the PG pin goes in to a hi impedance state. When the device is out of regulation or shutdown, the PG pin is pulled low. $10K\Omega$ to $1M\Omega$ resistor should be connected from PG to $V_{OUT}$ . |  |

| GND              | 8             | Ground connection.                                                                                                                                                                                                                                                                                                                                                              |  |

|                  | EDP           | Expose pad. Connected to PCB ground plane for good thermal dissipation.                                                                                                                                                                                                                                                                                                         |  |

NB: N/A = Not available in the shown package type

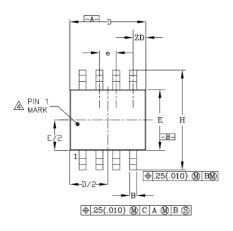

## **Pin Configuration**

## SOIC-8 (Top View)

## Absolute Maximum Ratings<sup>(1)</sup>

| Maximum Input Supply Voltage | 0.8 to 15V |

|------------------------------|------------|

| Enable Voltage               | 0.8 to 15V |

| Power Good                   | 0.8 to 15V |

| Feedback Voltage             |            |

| ByPass Voltage               | -0.8 to 5V |

#### **Recommended Operating Conditions**

Input Voltage...... 1.7 to 12V

## **ELECTRICAL CHARACTERISTICS**

| Enable input Voltage               | OV to V <sub>IN</sub> |

|------------------------------------|-----------------------|

| Junction Operating Temperature40°C | C to 125°C            |

### Thermal Information (2)

| SOIC-8 <sup>1</sup> $\theta_{IA}$ |       |

|-----------------------------------|-------|

| Storage Temperature Range         |       |

| Lead Temperature                  | 260°C |

| Junction Temperature              |       |

Unless otherwise noted:  $V_{IN}$ =5.0V;  $V_O$ =3.3V;  $C_{IN}$ = $C_{OUT}$ =22 $\mu$ F; -40°C to  $T_{J(MAX.)}$ = 125°C; Typical values are  $T_A$ = 25°C

| Parameter                    | Symbol                                                                                    | Conditions                               |                         | Min.  | Typ. | Max.                            | Units  |

|------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------|-------------------------|-------|------|---------------------------------|--------|

| Output Valtaga Danga         | Fixed option; 100mV increm                                                                |                                          | ncrement                | 0.5   |      | 5.0                             | V      |

| Output Voltage Range         | Vo                                                                                        | Adjustable                               |                         | 0.5   |      | V <sub>0</sub> +V <sub>D0</sub> |        |

| Output Voltage Tolerance     |                                                                                           | 1                                        |                         |       | TBD  |                                 | %      |

| Feedback Voltage             | V <sub>FB</sub>                                                                           |                                          |                         | 0.494 | 0.50 | 0.506                           | V      |

| Maximum Output Current       | Io                                                                                        |                                          |                         | 2     |      |                                 | А      |

| Shutdown current             | I <sub>SHD</sub>                                                                          | V <sub>EN</sub> =GND                     |                         |       | 0.1  | 1.0                             | μΑ     |

| Current Limit                | I <sub>LIM</sub>                                                                          |                                          |                         | 2.2   |      | 3.2                             | А      |

| Supply Current               | IQ                                                                                        | I <sub>OUT</sub> =2A                     |                         |       |      | TBD                             | mA     |

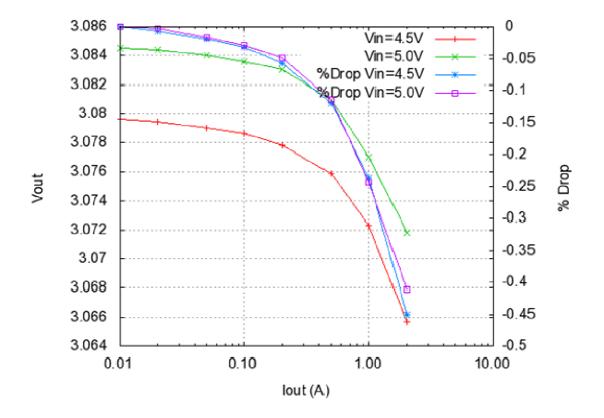

| Load Regulation <sup>3</sup> |                                                                                           | $I_{OUT} = 0.1 \text{mA} - 2\text{A}$    |                         | -1.0  |      | 1.0                             | %      |

| Line Regulation              |                                                                                           | $V_{IN}$ = Vo+1V to 12V; $I_{OUT}$ =10mA |                         | -0.5  |      | 0.5                             | %      |

|                              |                                                                                           | $I_{OUT} = 1A$                           |                         |       |      | TBD                             |        |

| Dropout Voltage              | V <sub>DO</sub>                                                                           | I <sub>OUT</sub> = 1.5A                  |                         |       |      | TBD                             | mV     |

|                              |                                                                                           | I <sub>OUT</sub> = 2A                    |                         |       |      | TBD                             |        |

| Enable Threshold Low         | V <sub>EN(L)</sub>                                                                        |                                          |                         |       |      | 0.8                             | V      |

| Enable Threshold High        | V <sub>EN(H)</sub>                                                                        |                                          |                         | 1.4   |      |                                 | V      |

| Input Enable Low Current     | I <sub>EN(L)</sub>                                                                        | $V_{\rm EN} = 0V$                        |                         |       | 0.01 | 2.0                             | μA     |

| Input Enable High Current    | I <sub>EN(H)</sub>                                                                        | V <sub>EN</sub> =2V                      |                         |       | 5.0  | 8.0                             | μΑ     |

| Dinula Deiretian Detie       |                                                                                           | I 50m A                                  | Freq=100Hz              |       | 62   |                                 | dB     |

| Ripple Rejection Ratio       |                                                                                           | I <sub>O</sub> =50mA                     | Freq=10KHz              |       | 60   |                                 | uБ     |

| Output Naisa                 | $e_n \qquad \begin{array}{c} BW; 10Hz - 100H \\ Io=100mA \\ C_{OUT}= 10\mu F \end{array}$ | BW; 10Hz – 100KHz                        | C <sub>BYP</sub> = Open |       | TBD  |                                 | nV/√Hz |

| Output Noise                 |                                                                                           |                                          | C <sub>BYP</sub> =100nF |       | TBD  |                                 |        |

| Power good low threshold     | V <sub>OL_PG</sub>                                                                        | I <sub>PG</sub> =200µA                   |                         |       |      | 400                             | mV     |

| Power good delay             | V <sub>PG_delay</sub>                                                                     |                                          |                         |       | 500  |                                 | μs     |

| Thermal Shutdown             | T <sub>SD</sub>                                                                           |                                          |                         |       | 140  |                                 | °C     |

| Thermal Shutdown Hys.        | Fhermal Shutdown Hys. T <sub>SD_HYS</sub>                                                 |                                          |                         |       | 15   |                                 | °C     |

#### Notes:

- 1. Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Measured on approximately 1" square of 1oz copper.

- 2. The PS22924 is guaranteed to meet performance specifications over the -40°C to +125°C junction operating temperature range and is assured by design, characterization, and correlation with statistical process control.

- 3. Load regulation is measured using pulse techniques with duty cycle <5%.

Plessey Semiconductors Ltd, Tamerton Road, Roborough, Plymouth, UK PL6 7BQ

Data Sheet 292205 issue 1

Tel: +44 (0)1752 693000

Fax: +44 (0)1752 693200

Web: www.plesseysemiconductors.com

email: sales@plesseysemi.com; October 12, 2010

Web: www.plesseysemiconductors.com

Typical Load regulation vs Iout(A)

Plessey Semiconductors Ltd, Tamerton Road, Roborough, Plymouth, UK PL6 7BQ

Data Sheet 292205 issue 1

Tel: +44 (0)1752 693000

Fax: +44 (0)1752 693200

Web: www.plesseysemiconductors.com

email: sales@plesseysemi.com; October 12, 2010

Web: www.plesseysemiconductors.com

#### **APPLICATION HINT**

#### **Input Capacitor** (C<sub>IN</sub>)

Input capacitor may be required when the device is not near the source power supply or when supplied by a battery. This capacitor will reduce the circuit's sensitivity when powered from complex source impedance and significantly enhance the output transient response. The input bypass should be mounted with the short possible track directly across the regulator's input and ground terminals. A  $10\mu$ F ceramic capacitor should be adequate for most applications.

#### **Output Capacitor** (C<sub>OUT</sub>)

The output capacitor provides not only stability to the regulator, but also, enhances the load transient response. A minimum capacitance of  $10\mu$ F is required. When selecting a ceramic capacitor, only X5R and X7R dielectric types should be used. Other types such as Z5U and Y5F have such severe loss of capacitance due to effects of temperature variation and applied voltage, they may provide as little as 20% of rated capacitance in many typical applications.

Always consult capacitor manufacturer's data curves before selecting a capacitor. High-quality ceramic capacitors can be obtained from Taiyo-Yuden, AVX, and Murata. Higher values of the output capacitance can be used to enhance loop stability and transient response.

#### **Output Voltage**

The adjustable output voltage option allows the user to select an output voltage by using an external resistor divider. PS22924 uses a 0.5V reference voltage at the positive terminal of the error amplifier. To set the output voltage a programming resistor from the feedback pin (FB) to ground must be selected. A  $10k\Omega$  resistor is a good selection for a programming resistor R2. A higher value may result in an excessively sensitive feedback node while a lower value will draw more current and degrade the light load efficiency. The equation for selecting the voltage specific resistor is:

$$V_o = \left(1 + \frac{R1}{R2}\right) * V_{FI}$$

For the fixed output devices, R1 and R2 are included within the device.

#### **ByPass Capacitor**

Connecting a capacitor between the BYP pin and ground can significantly reduce output noise. Values can range from 0pF to 100nF, depending on the sensitivity to output noise in the application. The start up speed of the PS22294 is inversely proportional to the size of the bypass capacitor. Applications requiring a slow ramp-up of output voltage should consider larger values of bypass capacitance. Likewise, if rapid turn on is necessary, consider omitting CBYP.

#### Enable/Shutdown

The enable (EN) pin is active high and is compatible with standard digital signalling levels. When  $V_{EN}$  below 0.8V, it turns the regulator off while VEN above 1.4V turns the regulator on. If not used, EN can be connected to the input Voltage. If EN is connected to  $V_{IN}$ , it should be connected as close as possible to the largest capacitance on the input to prevent voltage droops on that line from triggering the enable circuit.

#### **Thermal consideration**

The PS22294 is designed to provide 2A of continuous current in a very small package. Maximum power dissipation can be calculated based on the output current and the voltage drop across the part. To determine the maximum power dissipation of the package, use the junction-to-ambient thermal resistance of the device and the following basic equation:

$$P_{D(\max)} = \left(\frac{T_{J(\max)} - T_A}{\theta_{JA}}\right)$$

Where  $T_{J(max)}$  is the maximum junction temperature of the die,  $T_A$  is the ambient operating temperature, and  $\theta_{JA}$  is layout dependent. The actual power dissipation of the regulator circuit can be determined using the equation:

$$P_{\rm D} = (V_{\rm IN} - V_{\rm OUT}) * I_{\rm OUT} + V_{\rm IN} * I_{\rm SUI}$$

Plessey Semiconductors Ltd, Tamerton Road, Roborough, Plymouth, UK PL6 7BQ

Data Sheet 292205 issue 1

Tel: +44 (0)1752 693000

Fax: +44 (0)1752 693200

Web: www.plesseysemiconductors.com

email: sales@plesseysemi.com;

October 12, 2010

Veb: www.plesseysemiconductors.com

Substituting PD(max) for PD and solving for the operating conditions that are critical to the application will give the maximum operating conditions for the regulator.

The thermal resistance of the SO8-EDP is 36 (°C/W) junction to Ambient, and 5.5 (°C/W) junction to case.

## **Ordering Information**

| Device        | Operating Junction<br>Temp. | Package | Output voltage |

|---------------|-----------------------------|---------|----------------|

| PS22924C1S4A3 | -40°C to +125°C             | SOIC-8  | Adjustable     |

| PS22924TMS4A3 | -40°C to +125°C             | SOIC-8  | 2.5v           |

| PS22924TUS4A3 | -40°C to +125°C             | SOIC-8  | 3.3v           |

N.B For other values of output voltage please contact your local Plessey Semiconductors sales representative

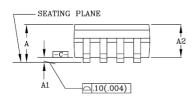

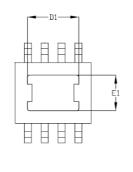

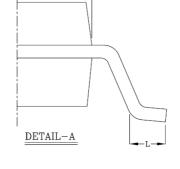

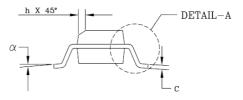

## **Outline Drawing and Landing Pattern (SOIC-8)**

| JL     | SOIC-8LD    |      |  |  |

|--------|-------------|------|--|--|

| SYMBOL | MILLIMETERS |      |  |  |

|        | MIN         | MAX  |  |  |

| A1     | 0.10        | 0.25 |  |  |

| В      | 0.36        | 0.46 |  |  |

| С      | 0.19        | 0.25 |  |  |

| D      | 4.80        | 4.98 |  |  |

| D1     | 3.20        | 3.40 |  |  |

| Е      | 3.81        | 3.99 |  |  |

| E1     | 2.19        | 2.39 |  |  |

| е      | 1.27 BSC    |      |  |  |

| Н      | 5.80        | 6.20 |  |  |

| h      | 0.25        | 0.50 |  |  |

| L      | 0.41        | 1.27 |  |  |

| A      | 1.52        | 1.72 |  |  |

| α      | 0°          | 8°   |  |  |

| ZD     | 0.53        | REF  |  |  |

| A2     | 1.37        | 1.57 |  |  |

#### For further information about this and other products, please visit: www.plesseysemiconductors.com

#### Legal Notice

Product information provided by Plessey Semiconductors Limited ("Plessey") in this document is believed to be correct and accurate. Plessey reserves the right to change/ correct the specifications and other data or information relating to products without notice but Plessey accepts no liability for errors that may appear in this document, howsoever occurring, or liability arising from the use or application of any information or data provided herein. Neither the supply of such information, nor the purchase or use of products conveys any licence or permission under patent, copyright, trademark or other intellectual property right of Plessey or third parties.

Products sold by Plessey are subject to its standard Terms and Conditions of Sale that are available on request. No warranty is given that products do not infringe the intellectual property rights of third parties, and furthermore, the use of products in certain ways or in combination with Plessey, or non-Plessey furnished equipments/components may infringe intellectual property rights of Plessey.

The purpose of this document is to provide information only and it may not be used, applied or reproduced (in whole or in part) for any purpose nor be taken as a representation relating to the products in question. No warranty or guarantee express or implied is made concerning the capability, performance or suitability of any product, and information concerning possible applications or methods of use is provided for guidance only and not as a recommendation. The user is solely responsible for determining the performance and suitability of the product in any application and checking that any specification or data it seeks to rely on has not been superseded.

Products are intended for normal commercial applications. For applications requiring unusual environmental requirements, extended temperature range, or high reliability capability (e.g. military, or medical applications), special processing/testing/conditions of sale may be available on application to Plessey.