PRELIMINARY

# DIGITAL COLOR SPACE CONVERTER

## FEATURES

- RGB to YCbCr and YCbCr to RGB conversions

- CyMaYe to YCbCr and YCbCr to CyMaYe conversions

- Bidirectional data buses for convenient interfacing

- Pixel rates up to 30 megapixels per second

- Supports 4:2:2 decimation and interpolation modes, with optional filtering

- Supports 4:1:1 decimation and interpolation with filtering

- CCIR601 and full range data scaling options

- Bidirectional shift registers for sync pulse delay matching

- Compatible with Zoran's ZR36050 JPEG Image Compression Processor and ZR36015 Raster to Block Converter

- 100-Pin PQFP package

- Low power CMOS, 5V

# APPLICATIONS

Image processing

- Image capture and display

- Image compression

# **GENERAL DESCRIPTION**

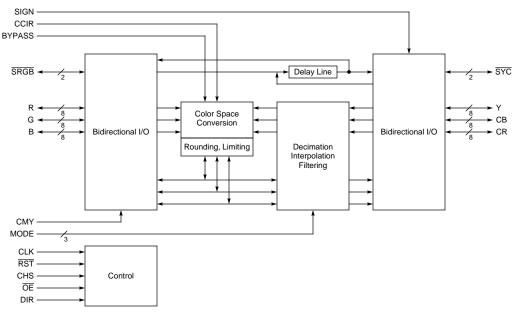

The ZR36011 Digital Color Space Convertor performs forward or inverse conversions between RGB and YCbCr color spaces. It is intended for use as a building block in systems that require this function. The direction of the conversion (RGB to YCbCr or YCbCr to RGB), and all other operating mode options, are determined by the states of control inputs. The 24-bit RGB and YCbCr data buses are bidirectional, making for straightforward interfacing when the direction of signal flow is reversible, as in a video compression and expansion module. Conversion between CyMaYe (Cyan, Magenta, Yellow) and YCbCr color spaces is also supported. An additional conversion stage, between RGB and CyMaYe color spaces, is inserted in this case, thus redefining the R, G, B pins as Cy, Ma, Ye.

The color space conversion coefficients are fixed. One of two sets of coefficients can be selected: one suitable for component

signal ranges conforming to CCIR Recommendation 601, the other for components occupying the full 8 bit numeric range.

Decimation and interpolation of the color difference signals is supported. The available modes are 4:4:4 (undecimated), 4:2:2 and 4:1:1. Filtering is optional in the 4:2:2 mode, and is always performed in the 4:1:1 mode. Other operating modes allow simple two-to-one compression to be performed by an additional decimation of the Y, Cb and Cr data, as well as the corresponding decompression by interpolation.

A two-bit bidirectional shift register, with the same number of stages (eight) as the computation pipeline, is provided. This can be used as a delay line for synchronization signals, to keep them synchronized with the data.

#### Figure 1. ZR36011 Block Diagram

## Table 1. Signal Description

| Name                  | Туре  | Description                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>       | Power | +5 volt power. All V <sub>CC</sub> pins must be connected to +5 volts.                                                                                                                                                                                                                                                                                            |

| V <sub>SS</sub>       | Power | Power supply ground. All V <sub>SS</sub> pins must be connected to ground.                                                                                                                                                                                                                                                                                        |

| CLK                   | Input | System clock input. Input data and sync signals are latched on the rising edge of CLK, and output data and sync signals change state following the rising edge of CLK.                                                                                                                                                                                            |

| RST                   | Input | Reset, active low. Must be kept low for at least two clock cycles to reset the device. When active, all stages of the sync delay lines are initialized to the high state, and the delay line output (SRGB if DIR is high, or SYC if DIR is low) is high.                                                                                                          |

| R(7-0)                | I/O   | Red component data if CMY is low, or Cyan if CMY is high. 8 bits unsigned. R is an input if DIR is low, and an output if DIR is high.                                                                                                                                                                                                                             |

| G(7-0)                | I/O   | Green component data if CMY is low, or Magenta if CMY is high. 8 bits unsigned. G is an input if DIR is low, and an output if DIR is high.                                                                                                                                                                                                                        |

| B(7-0)                | I/O   | Blue component data if CMY is low, or Yellow if CMY is high. 8 bits unsigned. B is an input if DIR is low, and an output if DIR is high.                                                                                                                                                                                                                          |

| SRGB(1-0)<br>SYC(1-0) | I/O   | Sync delay line inputs and outputs. If DIR is low, SRGB is the input and SYC is the output, and vice versa if DIR is high. Input level changes appear at the output with a delay of 8 clock cycles. Since the delay line output is initialized to high by RST, these signals are considered active low.                                                           |

| Y(7-0)                | I/O   | Luminance component data. 8 bits unsigned. Y is an output if DIR is low, and input if DIR is high.                                                                                                                                                                                                                                                                |

| CB(7-0)               | I/O   | Blue color difference (Cb) component data. 8 bits unsigned if SIGN is low, or 8 bits two's complement if SIGN is high. CB is an output if DIR is low, and input if DIR is high. In 4:2:2 and 4:1:1 modes, CB is unused (if outputs, all CB pins are high).                                                                                                        |

| CR(7-0)               | I/O   | Red color difference (Cr) component data. 8 bits unsigned if SIGN is low, or 8 bits two's complement if SIGN is high. CR is an output if DIR is low, and input if DIR is high. In 4:2:2 and 4:1:1 modes, Cb and Cr data are multiplexed on CR.                                                                                                                    |

| DIR                   | Input | Direction control. If DIR is low, RGB (or CyMaYe) to YCbCr conversion is performed. If DIR is high, YCbCr to RGB (or CyMaYe) conversion is performed.                                                                                                                                                                                                             |

| СМҮ                   | Input | CyMaYe color space control. If CMY is low, conversion between RGB and YCbCr color spaces is performed. If CMY is high, the R, G and B inputs or outputs are complemented, with the result that conversion between CyMaYe and YCbCr color spaces is performed.                                                                                                     |

| CCIR                  | Input | Signal level control. If CCIR is low, input and output data may occupy the full 8 bit signal level range. If CCIR is high, input and output data signal levels conform to CCIR Recommendation 601-2.                                                                                                                                                              |

| CHS                   | Input | Chrominance multiplex synchronization signal. The rising edge of this signal is used to synchronize an internal toggle that controls the multiplexing of the Cb and Cr component data on the CB pins, in the operating modes with decimated chrominance. In operating modes with decimated luminance, it determines the temporal alignment of the decimated data. |

| SIGN                  | Input | Chrominance numerical representation control. The Cb and Cr data is unsigned if SIGN is low, and two's comple-<br>ment if SIGN is high.                                                                                                                                                                                                                           |

| ŌĒ                    | Input | Output enable. When low, all outputs are enabled. When high, all outputs are disabled (floating). OE also disables the internal clock of the device when it is high, thus freezing all internal processing.                                                                                                                                                       |

## Table 1. Signal Description (Continued)

| Name      | Туре  | Description                                                                                                                                                      |                  |                 |                                                                                                                                                |  |  |  |

|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MODE(2-0) | Input | Component decimation mode control. The decimation and interpolation modes are selected using MODE as shown follows:<br>Decimation Mode Selection (0=low, 1=high) |                  |                 |                                                                                                                                                |  |  |  |

|           |       | MODE2                                                                                                                                                            | MODE1            | MODE0           | Description                                                                                                                                    |  |  |  |

|           |       | 0                                                                                                                                                                | 0                | 0               | 4:4:4, no decimation or interpolation                                                                                                          |  |  |  |

|           |       | 0                                                                                                                                                                | 0                | 1               | 4:2:2 chrominance decimation or interpolation without filtering                                                                                |  |  |  |

|           |       | 0                                                                                                                                                                | 1                | 0               | 4:2:2 chrominance decimation or interpolation with filtering                                                                                   |  |  |  |

|           |       | 0                                                                                                                                                                | 1                | 1               | 4:1:1 chrominance decimation or interpolation                                                                                                  |  |  |  |

|           |       | 1                                                                                                                                                                | 0                | 0               | Not used                                                                                                                                       |  |  |  |

|           |       | 1                                                                                                                                                                | 0                | 1               | Not used                                                                                                                                       |  |  |  |

|           |       | 1                                                                                                                                                                | 1                | 0               | 4:4:4, with 2 to 1 decimation or interpolation of all three YCbCr components                                                                   |  |  |  |

|           |       | 1                                                                                                                                                                | 1                | 1               | 4:2:2, with 2 to 1 additional decimation or interpolation of all three YCbCr components                                                        |  |  |  |

| BYPASS    | Input |                                                                                                                                                                  | elections and co | ontrol inputs a | n, the color space conversion computation is bypassed, but all deci-<br>re still operational. The data pipeline delay of 8 clock cycles is not |  |  |  |

## FUNCTIONAL OVERVIEW

## COLOR SPACE CONVERSION

#### RGB <-> YCbCr

The Color Space Conversion block (see Figure 1) performs conversion between RGB and YCbCr color spaces, with built in conversion coefficients. One of two data scaling and limiting modes can be selected by means of the CCIR control input, one (with CCIR low) intended for data occupying the full 8 bit signal level range, the other (with CCIR high) intended for data occupying the range of values specified by CCIR Recommendation 601-2. The conversions are performed as follows:

#### Forward direction, DIR = low:

With CCIR low (8 bit full range data):

Y = 0.299R + 0.587G + 0.114B Cr = 0.713(R-Y) Cb = 0.564(B-Y)

With CCIR high (data conforming to CCIR):

Y = 0.299R + 0.587G + 0.114B Cr = 0.729(R-Y) Cb = 0.577(B-Y)

Inverse direction, DIR = high:

With CCIR low (8 bit full range data):

R = Y + 1.402Cr

G = Y - 0.714Cr - 0.344Cb

With CCIR high (data conforming to CCIR):

R = Y + 1.37Cr

G = Y - 0.698Cr - 0.336Cb

B = Y + 1.73Cb

Internally, the color space conversion coefficients are represented with a precision of 12 bits.

#### RGB <-> CyMaYe

When the CMY control input is high, the 8 bit R, G and B data are logically complemented in the I/O block, thus performing an additional conversion between the internal R, G, B and external Cy, Ma, Ye. This is equivalent to the following conversion formula:

Cy = 255 - R Ma = 255 - G Ye = 255 - B

#### NUMERICAL REPRESENTATION

The results of the color space conversion are rounded to produce 8 bit results, and limited to prevent wrap-around. When CCIR is high, R, G, B, and Y occupy 220 levels, and CR and CB occupy 225 levels. Input data outside the allowed range of levels is internally limited, and output data is limited to the allowed range. When CCIR is low, inputs can occupy the full 8 bit range, and outputs are limited to this range.

CR and CB can have either two's complement or offset binary representations, as selected by the SIGN control input. R, G, B and Y always have unsigned magnitude representation.

Tables 2 and 3 show, for CCIR low and CCIR high, respectively, the equivalent decimal number represented by each hexadecimal value of the data inputs and outputs.

#### Table 2. Numerical Representation, CCIR = low

|                      | Decimal Equivalent       |                               |                                      |  |  |  |

|----------------------|--------------------------|-------------------------------|--------------------------------------|--|--|--|

|                      |                          | CR, CB                        |                                      |  |  |  |

| Hexadecimal<br>Value | R, G, B, Y<br>(Unsigned) | Offset Binary<br>(SIGN = low) | Two's<br>Compliment<br>(SIGN = high) |  |  |  |

| FF                   | 255                      | 127                           | -1                                   |  |  |  |

| FE                   | 254                      | 126                           | -2                                   |  |  |  |

|                      |                          |                               |                                      |  |  |  |

| 81                   | 129                      | 1                             | -127                                 |  |  |  |

| 80                   | 128                      | 0                             | -128                                 |  |  |  |

| 7F                   | 127                      | -1                            | 127                                  |  |  |  |

|                      |                          |                               |                                      |  |  |  |

| 01                   | 1                        | -127                          | 1                                    |  |  |  |

| 00                   | 0                        | -128                          | 0                                    |  |  |  |

#### Table 3. Numerical Representation, CCIR = high

|                      | Decimal Equivalent       |                               |                                     |  |  |  |  |

|----------------------|--------------------------|-------------------------------|-------------------------------------|--|--|--|--|

|                      |                          | CR, CB                        |                                     |  |  |  |  |

| Hexadecimal<br>Value | R, G, B, Y<br>(Unsigned) | Offset Binary<br>(SIGN = low) | Two's<br>Compliment<br>(SIGN = high |  |  |  |  |

| FF                   | 235                      | 112                           | -1                                  |  |  |  |  |

| FE                   | 235                      | 112                           | -2                                  |  |  |  |  |

|                      |                          |                               |                                     |  |  |  |  |

| F1                   | 235                      | 112                           | -15                                 |  |  |  |  |

| F0                   | 235                      | 112                           | -16                                 |  |  |  |  |

#### Table 3. Numerical Representation, CCIR = high (Continued)

|                      | Decimal Equivalent       |                               |                                     |  |  |  |  |

|----------------------|--------------------------|-------------------------------|-------------------------------------|--|--|--|--|

|                      |                          | CR, CB                        |                                     |  |  |  |  |

| Hexadecimal<br>Value | R, G, B, Y<br>(Unsigned) | Offset Binary<br>(SIGN = Iow) | Two's<br>Compliment<br>(SIGN = high |  |  |  |  |

| EF                   | 235                      | 111                           | -17                                 |  |  |  |  |

| EE                   | 235                      | 110                           | -18                                 |  |  |  |  |

| ED                   | 235                      | 109                           | -19                                 |  |  |  |  |

| EC                   | 235                      | 108                           | -20                                 |  |  |  |  |

| EB                   | 235                      | 107                           | -21                                 |  |  |  |  |

| EA                   | 234                      | 106                           | -22                                 |  |  |  |  |

|                      |                          |                               |                                     |  |  |  |  |

| 91                   | 145                      | 17                            | -111                                |  |  |  |  |

| 90                   | 144                      | 16                            | -112                                |  |  |  |  |

| 8F                   | 143                      | 15                            | -112                                |  |  |  |  |

|                      |                          |                               |                                     |  |  |  |  |

| 81                   | 129                      | 1                             | -112                                |  |  |  |  |

| 80                   | 128                      | 0                             | -112                                |  |  |  |  |

| 7F                   | 127                      | -1                            | 112                                 |  |  |  |  |

|                      |                          |                               |                                     |  |  |  |  |

| 71                   | 113                      | -15                           | 112                                 |  |  |  |  |

| 70                   | 112                      | -16                           | 112                                 |  |  |  |  |

| 69                   | 111                      | -17                           | 111                                 |  |  |  |  |

|                      |                          |                               |                                     |  |  |  |  |

| 11                   | 17                       | -111                          | 17                                  |  |  |  |  |

| 10                   | 16                       | -112                          | 16                                  |  |  |  |  |

| 0F                   | 16                       | -112                          | 15                                  |  |  |  |  |

|                      |                          |                               |                                     |  |  |  |  |

| 01                   | 16                       | -112                          | 1                                   |  |  |  |  |

| 00                   | 16                       | -112                          | 0                                   |  |  |  |  |

## **CONVERSION BYPASS**

When the BYPASS control input is high, the color space conversion block (Figure 1), and consequently the RGB <-> YCbCr color space conversion computation, is bypassed. All the other functional blocks, and all control inputs, continue to operate normally. Thus, when BYPASS is high, the device can be utilized as a data format convertor, for example:

■ With CMY high, and MODE(2-0) = 000, as a RGB to CyMaYe convertor

- With MODE(2-0) = 010, to perform conversions between 4:4:4 and 4:2:2 formats

- With MODE(2-0) = 110, to perform 2:1 decimation and interpolation of all three components

## INPUT TO OUTPUT LATENCY

The output data has a latency or pipeline delay of eight clock cycles. This latency is constant, in all modes of operation, regardless of the direction of conversion, decimation or interpolation setting, or whether the color space conversion is bypassed or not.

## DELAY LINE

The delay line consists of an eight stage shift register with a two bit wide data path. Its delay is equal to the latency of the data outputs. Thus, it is useful as a matching delay line for horizontal and vertical video synchronization signals, to keep them in synchronization with the data flowing through the device.

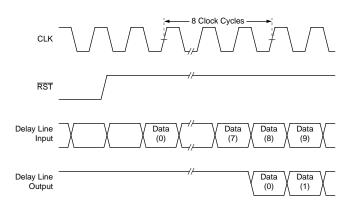

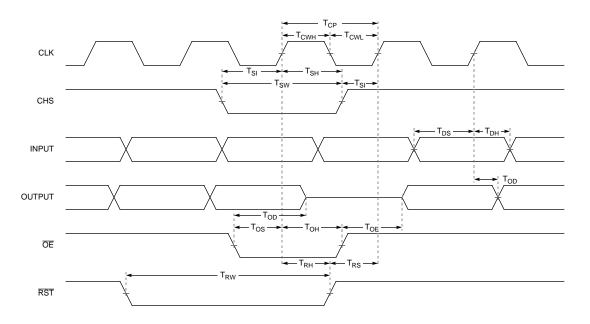

The  $\overline{\text{RST}}$  input resets all stages of the delay line to the high state, and consequently the output ( $\overline{\text{SYC}}$  or  $\overline{\text{SRGB}}$  depending on the state of DIR) is also high when reset is active. The delay line is therefore suitable for active low synchronization signals. The input at  $\overline{\text{SYC}}$  or  $\overline{\text{SRGB}}$  is effectively ignored when RST is active, and is clocked into the delay line starting from the second rising edge of CLK following the deactivation of  $\overline{\text{RST}}$ , as shown in Figure 2.

Figure 2. Delay Line Reset Timing

## **OUTPUT ENABLE AND PIPELINE FREEZE**

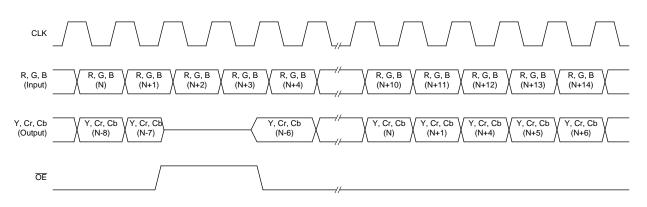

The  $\overline{OE}$  input simultaneously controls the enabling of all output pins (color components and delay line), and the freezing of the computational pipeline. When  $\overline{OE}$  is low, the output pins are enabled, and data is clocked through the pipeline. When  $\overline{OE}$ goes high, the outputs go into a high impedance state, and the clock is disabled internally starting at the second rising edge of CLK following the rising edge of  $\overline{OE}$ , thus freezing all operations in their current state, including the color space conversion computation, decimation and interpolation, and the delay line. Input data is ignored while the clock is disabled. The clock is enabled again starting at the second rising edge of CLK following the falling edge of  $\overline{OE}$ . Note that since OE enables and disables the internal clock, it is a synchronous input and must have sufficient setup and hold time. See Figure 3 for an example of the operation of  $\overline{OE}$ .

## **DECIMATION AND INTERPOLATION MODES**

The three MODE control pins select the operating mode of the decimation and interpolation function block, as shown in Table 1. Decimation is performed in forward color space conversion (DIR = low), and interpolation is performed in inverse color space conversion (DIR = high).

Whenever decimation or interpolation of the luminance and/or chrominance data is performed (all modes with the exception of MODE = 000), each data sample on the Y, CB, CR pins occupies more than one clock cycle, or the chrominance data is multiplexed on the CR pins, or both (multiplexed chrominance samples that occupy more than one clock cycle each). The CHS input signal must be used, as shown in the timing diagrams for each of the modes, to synchronize the operation of the device to the data on the Y, CR, CB pins. The second rising edge of CLK following the rising edge of CHS always samples the first input data point. CHS is used to initialize the state of the internal mechanism that subsequently maintains the synchronization.

#### MODE = 000

In this mode no decimation or interpolation is performed. YCbCr pixels are 24 bits wide; the CR pins carry the Cr data and the CB pins carry the Cb data. A timing diagram for forward conversion is shown in Figure 3; inverse conversion in this mode has identical timing, except that the functions of the R, G, B pins are exchanged with those of the Y, CR, CB pins. The operation of the  $\overline{OE}$  signal is also depicted in Figure 3. CHS is not used in this mode of operation.

## MODE = 001

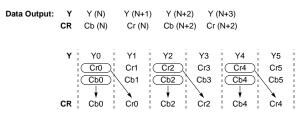

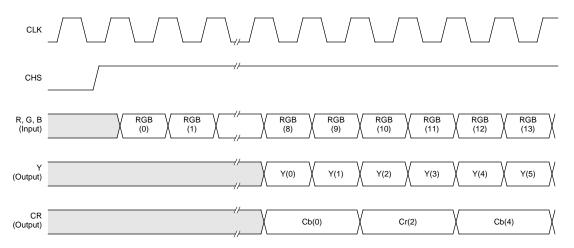

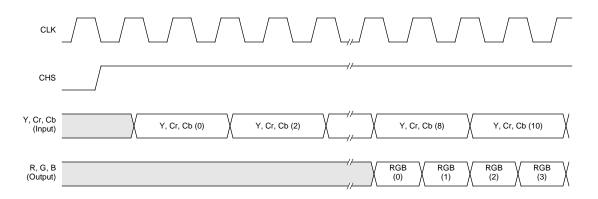

In this mode, YCbCr data is in 4:2:2 format. The CB pins are not used; Cb and Cr data are multiplexed on the CR pins. The Cb and Cr samples are co-sited with the Y sample that is simulta-

neous with the Cb sample. Cb and Cr are decimated in forward conversion by dropping the unused samples, and interpolated in inverse conversion by replication. No filtering is performed in either direction. Figures 4 and 5, respectively, illustrate how the decimation and interpolation are performed.

Figure 4. Illustration of Decimation Method, MODE = 001

| Data Input:          | Y<br>CR | Y (N)<br>Cb (N)           | Y (N+1)<br>Cr (N)           | Y (N+2)<br>Cb (N+2)             | Y (N+3)<br>Cr (N+2)                                | Y (N+4)<br>Cb (N+4) |

|----------------------|---------|---------------------------|-----------------------------|---------------------------------|----------------------------------------------------|---------------------|

| Interpolator Output: |         | Y (N)<br>Cr (N)<br>Cb (N) | Y (N+1)<br>Cr (N)<br>Cb (N) | Y (N+2)<br>Cr (N+2)<br>Cb (N+2) | Y (N+3)<br>Cr (N+2)<br>Cb (N+2)                    |                     |

|                      | Y<br>CR | Сьо                       | Y1<br>Cr0<br>Cr0<br>Cb0     | Cb2<br>Cr2                      | Y3 Y4<br>Cr2 Ct<br>↓<br>Cr2 Cr<br>Cr2 Cr<br>Cb2 Ct | 4 Cr4<br>4 Cr4      |

## Figure 5. Illustration of Interpolation Method, MODE = 001

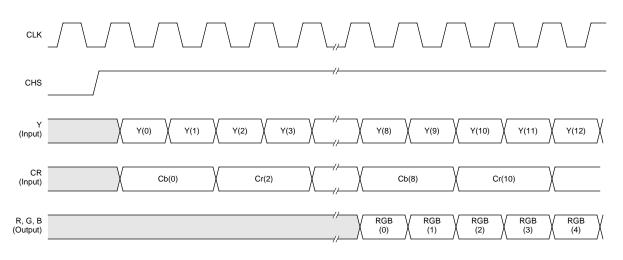

CHS determines the validity of input data and synchronizes the multiplexing of Cr and Cb on the CR pins. As shown in Figure 6 for forward conversion, and Figure 7 for inverse conversion, the second rising edge of CLK following the rising edge of CHS latches the first valid input data sample and determines the multiplex order.

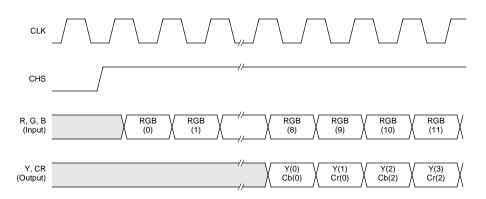

Figure 6. RGB to YCbCr Timing, MODE = 001

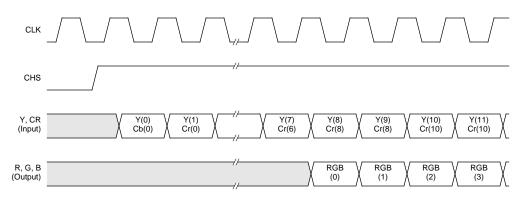

Figure 7. YCbCr to RGB Timing, MODE = 001

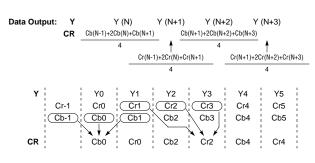

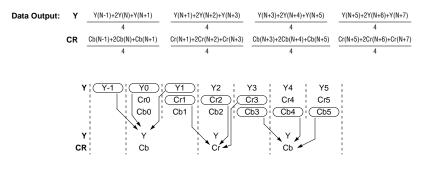

#### MODE = 010

This mode is similar to MODE = 001, with the addition of a filtering stage in decimation and interpolation. A three tap decimation filter is used, and the interpolation is performed by averaging adjacent samples. This is illustrated in Figures 8 and 9, respectively. The signal timing in MODE = 010 is as shown in Figures 6 and 7.

| Data Input:          | Y<br>CR | Y (N)<br>Cb (N)         | Y (N+1)<br>Cr (N)                                            |                         | Y (N+2)<br>Cb (N+2)             | Y (N+3)<br>Cr (N+2)           |                                                         |

|----------------------|---------|-------------------------|--------------------------------------------------------------|-------------------------|---------------------------------|-------------------------------|---------------------------------------------------------|

| Interpolator Output: |         | Y (N)<br>Cr (N)         | Y (N+1)<br>Cr(N)+Cr(N+                                       |                         | Y (N+2)<br>Cr (N+2)             | Y (N+3)<br>Cr(N+2)+Cr(N+<br>2 | 4)                                                      |

|                      |         | Cb (N)                  | Cb(N)+Cb(N+                                                  | -2)                     | Cb (N+2)                        | 2                             | +4)                                                     |

|                      | Y<br>CR | Y0<br>Cb0<br>Cr0<br>Cb0 | Y1<br>Cr0<br>2<br><u>Cr0+Cr2</u><br>2<br><u>Cb0+Cb2</u><br>2 | Y2<br>Cb2<br>Cr2<br>Cb2 | 2 Cr2<br>2 Cr2+Cr4<br>2 Cr2+Cr4 |                               | Y5<br>Cr4<br><u>Cr4+Cr6</u><br>2<br><u>Cb4+Cb6</u><br>2 |

Figure 9. Illustration of Interpolation Method, MODE = 001

#### MODE = 011

In this mode, YCbCr data is in 4:1:1 format, with one sample each of Cb and Cr for every four samples of Y. Cb and Cr are multiplexed on the CR pins, valid for two clock cycles each.The CB pins are not used. Decimation in forward conversion, and interpolation in inverse conversion, are performed as illustrated in Figures 10 and 11.

| Data Output: | Y  | Y (N)            | Y (N+1)          | Y (N+2)          | Y (N+3)          | Y (N+4)     | Y (N+5)          |

|--------------|----|------------------|------------------|------------------|------------------|-------------|------------------|

|              | CR | Cb(N-1)+20       | Cb(N)+Cb(N+1)    | Cr(N+1)+2Cr(     | N+2)+Cr(N+3)     | Cb(N+3)+2Cb | (N+4)+Cb(N+5)    |

|              |    | 4                |                  |                  | 4                | 4           |                  |

|              | Y  | Y0<br>Cr0<br>Cb0 | Y1<br>Cr1<br>Cb1 | Y2<br>Cr2<br>Cb2 | Y3<br>Cr3<br>Cb3 |             | Y5<br>Cr5<br>Cb5 |

|              | CR | Cb               |                  | Cr               |                  | Cb          |                  |

Figure 10. Illustration of Decimation Method, MODE = 011

| Data           | a Input: Y<br>CR | . ,             | Y (N+1)<br>b (N)      | . ,    | Y (N+3)<br>N+2) | Y (N+4)<br>Cb (     | Y (N+5)<br>N+4)     |  |

|----------------|------------------|-----------------|-----------------------|--------|-----------------|---------------------|---------------------|--|

| Interpolator ( | Dutput:          | Y (N)<br>Cr(N-3 | Y (N+1)<br>2)+Cr(N+2) | . ,    | Y (N+3)<br>N+2) | Y (N+4)<br>Cr(N+2)- | Y (N+5)<br>+Cr(N+6) |  |

|                |                  |                 | 2                     |        | Cb(N)+Cb(N+4)   |                     | 2                   |  |

|                |                  | C               | Cb (N)                |        | 2               |                     | Cb (N+4)            |  |

| Y              | Y0               | Y1              | Y2 Y                  | 3 ¦ Y4 | Y5              | Y6                  | Y7                  |  |

| CR             | Cb0              |                 | Cr2                   |        | Cb4             |                     | Cr6                 |  |

|                |                  |                 | Cr2                   | -      | Cr2+Cr6         | · ` ` `             | Y<br>Cr6            |  |

|                |                  | İ               | <u>Cb0+Cb4</u><br>2   |        | Cb4             | <u>Cb4</u>          | 4+Cb8<br>2          |  |

Figure 11. Illustration of Interpolation Method, MODE = 011

CHS determines the validity of input data and synchronizes the multiplexing of Cr and Cb on the CR pins. As shown in Figure 12 for forward conversion, and Figure 13 for inverse conversion, the second rising edge of CLK following the rising edge of CHS latches the first valid input data sample and determines the multiplex order.

Figure 12. RGB to YCbCr Timing, MODE = 011

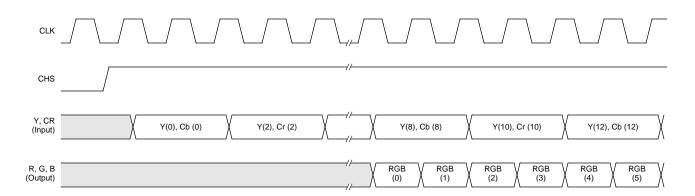

Figure 13. YCbCr to RGB Timing, MODE = 011

ı

#### **MODE = 110**

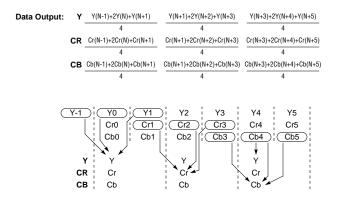

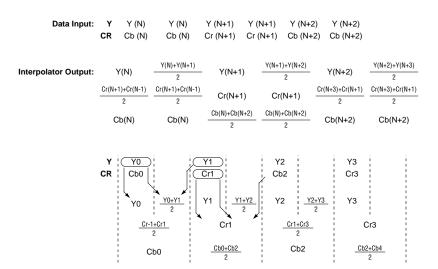

In this mode, the YCbCr format is 4:4:4, but the YCbCr pixel rate is one half the RGB pixel rate. The CR pins carry the Cr data and the CB pins carry the Cb data. In forward conversion, the YCbCr data is 2:1 decimated through a three tap filter, as illustrated in Figure 14. In inverse conversion, the input YCbCr data is interpolated by averaging two adjacent samples, as illustrated in Figure 15.

Figure 14. Illustration of Decimation, MODE = 110

| Data Input:          | Y            | Y (N  | ) Y (N                                   | ) Y (N-          | +1) Y(N                                  | √+1) `           | Y (N+2)                  | Y (N+2)          |  |

|----------------------|--------------|-------|------------------------------------------|------------------|------------------------------------------|------------------|--------------------------|------------------|--|

|                      | CR           | Cr (N | ) Cr (N                                  | l) Cr (N         | +1) Cr (1                                | N+1) (           | Cr (N+2)                 | Cr (N+2)         |  |

|                      | СВ           | Cb (N | I) Cr (N                                 | l) Cb (N         | +1) Cb (I                                | N+1) C           | Cb (N+2)                 | Cb (N+2)         |  |

|                      |              | (     | / - (                                    | ,                | ,                                        | , -              | ,                        |                  |  |

|                      |              |       |                                          |                  |                                          |                  |                          |                  |  |

|                      |              | Y(N   | l)+Y(N+1)                                |                  | Y(N+1)+Y(N                               | +2)              | (1) (1)                  | Y(N+2)+Y(N+3)    |  |

| Interpolator Output: | Y(N          | ) —   | 2                                        | Y(N+1)           | 2                                        | — Y              | ′(N+2)                   | 2                |  |

|                      |              | Cr(M  | I)+Cr(N+1)                               |                  | Cr(N+1)+Cr(N                             | (+2)             | (                        | Cr(N+2)+Cr(N+3)  |  |

|                      | Cr(N         | ) —   | 2                                        | Cr(N+1)          | 2                                        | — C              | r(N+2)                   | 2                |  |

|                      |              | Ch/M  | L)+Cb(N+1)                               |                  | Cb(N+1)+Cb(I                             | NI - 2)          |                          | b(N+2)+Cb(N+3)   |  |

|                      | Cb(N         | ) —   | 2                                        | Cb(N+1)          | 2                                        | — Ct             | o(N+2)                   |                  |  |

|                      |              |       | 2                                        |                  | 2                                        |                  |                          | 2                |  |

|                      |              |       |                                          |                  |                                          |                  |                          |                  |  |

| Y                    | ¦(Y          | 0)¦   | 1                                        | <u>Y1</u> ;      | 1                                        | Y2               | 1                        | Y3               |  |

|                      |              |       |                                          |                  |                                          |                  |                          |                  |  |

| CR                   | ¦  C         | r0    | fle                                      | (Cr1)            | i.                                       | Cr2              | )¦                       | Cr3              |  |

|                      | 11           | - 1 i |                                          |                  |                                          |                  | )¦                       |                  |  |

| CR<br>CB             |              | - 1 i | , ∠Ł                                     | Cb1              |                                          | Cb2              |                          | Cb3              |  |

|                      | CI           | - 1 i | <u>Y0+Y1</u>                             | Cb1              | <u>Y1+Y2</u>                             |                  | )<br>  <u>Y2+Y3</u>      | Cb3              |  |

|                      | CI           | b0 \  | , ∠Ł                                     | Cb1              | <u>Y1+Y2</u>                             | Cb2              | )<br><u>Y2+Y3</u><br>2   | Cb3              |  |

|                      | CI           | 0     | <u>Y0+Y1</u><br>2<br><u>Cr0+Cr1</u>      | Cb1              | <u>Y1+Y2</u><br>2<br><u>Cr1+Cr2</u>      | Cb2              | 2<br>Cr2+Cr3             | Cb3<br>Y3        |  |

|                      | CI           | 0     | <u>Y0+Y1</u>                             | Cb1<br>Y1        | <u>Y1+Y2</u>                             | Cb2<br>Y2        | 2                        | Cb3<br>Y3        |  |

|                      | CI<br>Y<br>C | r0    | <u>Y0+Y1</u><br>2<br><u>Cr0+Cr1</u>      | Cb1<br>Y1<br>Cr1 | <u>Y1+Y2</u><br>2<br><u>Cr1+Cr2</u>      | Cb2<br>Y2        | 2<br>Cr2+Cr3             | Cb3<br>Y3<br>Cr3 |  |

|                      | CI           | r0    | <u>Y0+Y1</u><br>2<br><u>Cr0+Cr1</u><br>2 | Cb1<br>Y1<br>Cr1 | <u>Y1+Y2</u><br>2<br><u>Cr1+Cr2</u><br>2 | Cb2<br>Y2<br>Cr2 | 2<br><u>Cr2+Cr3</u><br>2 | Cb3<br>Y3<br>Cr3 |  |

Figure 15. Illustration of Interpolation, MODE = 110

CHS determines the validity of input data and synchronizes the half-clock-rate data transitions on the Y, CR and CB pins. As shown in Figure 16 for forward conversion, and Figure 17 for inverse conversion, the second rising edge of CLK following the rising edge of CHS latches the first valid input data sample.

Figure 16. RGB to YCbCr Timing, MODE = 110

Figure 17. YCbCr to RGB Timing, MODE = 110

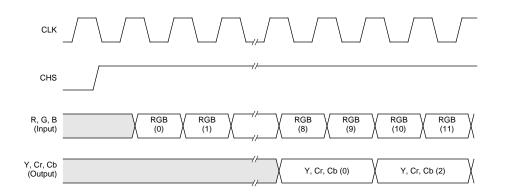

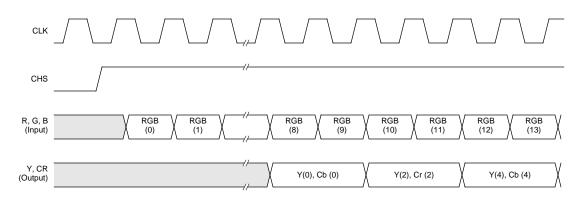

## MODE = 111

In this mode, YCbCr data is in 4:2:2 format, with Cb and Cr multiplexed on the CR pins, and the data rate of Y, Cb and Cr is reduced by an additional factor of two. The decimation method for forward conversion is illustrated in Figure 17, and the interpolation method for inverse conversion in Figure 18.

Figure 18. Illustration of Decimation, MODE = 111

Figure 19. Illustration of Interpolation, MODE = 111

CHS determines the validity of input data and synchronizes the half-clock-rate data transitions on the Y, CR pins, and the multiplexing of Cb and Cr. As shown in Figure 20 for forward conversion, and Figure 21 for inverse conversion, the second rising edge of CLK following the rising edge of CHS latches the first valid input data sample.

Figure 20. RGB to YCbCr Timing, MODE = 111

# PRELIMINARY

# ABSOLUTE MAXIMUM RATINGS

| Storage Temperature      | 65°C to +150°C                |

|--------------------------|-------------------------------|

| Supply Voltage to Ground | 0.3V to +7.0V                 |

| DC Output Voltage        | 0.3V to V <sub>CC</sub> +0.3V |

| DC Input Voltage         | 0.3V to V <sub>CC</sub> +0.3V |

| DC Input Current         | 10mA to +10mA                 |

NOTE: Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGE**

| Temperature    | $\dots 0^{\circ}C \le T_A \le +70^{\circ}C$                            |

|----------------|------------------------------------------------------------------------|

| Supply Voltage | $\dots \dots 4.75 \text{V} \le \text{V}_{\text{CC}} \le 5.25 \text{V}$ |

# **DC CHARACTERISTICS**

| Symbol          | Parameter              | Min | Тур | Max | Units | Test Conditions                                                                  |

|-----------------|------------------------|-----|-----|-----|-------|----------------------------------------------------------------------------------|

| V <sub>IL</sub> | Input Low Voltage      |     |     | 0.8 | V     |                                                                                  |

| V <sub>IH</sub> | Input High Voltage     | 2.0 |     |     | V     |                                                                                  |

| V <sub>OL</sub> | Output Low Voltage     |     |     | 0.4 | V     | I <sub>OL</sub> = 2mA                                                            |

| V <sub>OH</sub> | Output High Voltage    | 2.4 |     |     | V     | I <sub>OH</sub> = -400μA                                                         |

| I <sub>CC</sub> | Power Supply Current   |     | 90  |     | mA    | V <sub>CC</sub> = 5.0 V, C <sub>L</sub> = 20pF,<br>T <sub>A</sub> = 25°C, 30 MHz |

| ILI             | Input Leakage Current  |     |     | ±10 | μA    | $V_{IN} = V_{CC} \text{ or } V_{SS}$                                             |

| I <sub>OZ</sub> | Output Leakage Current |     |     | ±10 | μA    | V <sub>OUT</sub> = V <sub>CC</sub> or V <sub>SS</sub> ,<br>output disabled       |

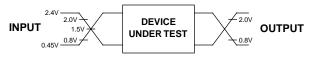

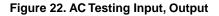

During AC testing, inputs are driven at 0.4V and 2.4V levels. Unless othrewise specified, switching times are measured from the 1.5V level of DCLK to the 0.8V or 2.0V levels at the input/output.

Figure 23. Normal AC Test Load

# **AC CHARACTERISTICS**

| Symbol           | Parameter              | Min               | Max | Units | Test Conditions |

|------------------|------------------------|-------------------|-----|-------|-----------------|

| T <sub>CP</sub>  | Clock period           | 33                |     | ns    |                 |

| T <sub>CWH</sub> | Clock high width       | 10                |     | ns    |                 |

| T <sub>CWL</sub> | Clock low width        | 10                |     | ns    |                 |

| T <sub>DS</sub>  | Input data setup time  | 7                 |     | ns    |                 |

| T <sub>DH</sub>  | Input data hold time   | 1                 |     | ns    |                 |

| T <sub>DD</sub>  | Output data delay time | 4                 | 18  | ns    | $C_L = 50 pF$   |

| T <sub>OD</sub>  | Output disable time    | 3                 |     | ns    |                 |

| T <sub>OE</sub>  | Output enable time     |                   | 13  | ns    |                 |

| T <sub>OS</sub>  | OE setup time          | 5                 |     | ns    |                 |

| Т <sub>ОН</sub>  | OE hold time           | 1                 |     | ns    |                 |

| T <sub>SW</sub>  | CHS pulse width        | T <sub>CP</sub>   |     |       |                 |

| T <sub>SI</sub>  | CHS setup time         | 3                 |     | ns    |                 |

| T <sub>SH</sub>  | CHS hold time          | 0                 |     | ns    |                 |

| T <sub>RW</sub>  | RST pulse width        | 2*T <sub>CP</sub> |     |       |                 |

| T <sub>RS</sub>  | RST setup time         | 5                 |     | ns    |                 |

| T <sub>RH</sub>  | RST hold time          | 1                 |     | ns    |                 |

Figure 24. Input Timing Requirements and Output Switching Characteristics

# PACKAGE INFORMATION

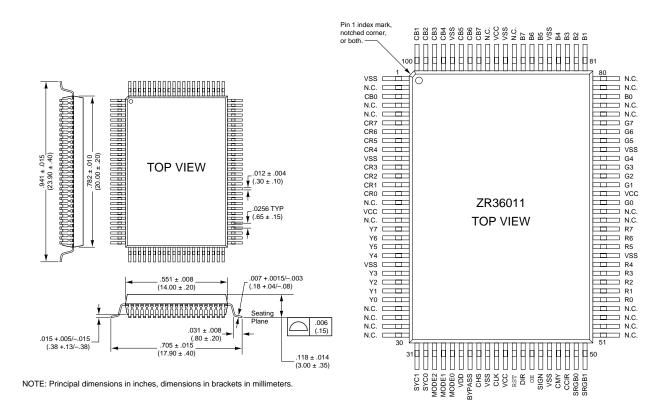

# **100-Pin Flat Pack Pin Assignment**

| Pin | Pin  | _    | Pin | Pin    | _    | Pin | Pin   |      | Pin | Pin  | _    | Pin | Pin  | _    |

|-----|------|------|-----|--------|------|-----|-------|------|-----|------|------|-----|------|------|

| No  | Name | Туре | No  | Name   | Туре | No  | Name  | Туре | No  | Name | Туре | No  | Name | Туре |

| 1   | VSS  | Р    | 21  | Y4     | В    | 41  | VCC   | Р    | 61  | R5   | В    | 81  | B1   | В    |

| 2   | N.C. | -    | 22  | VSS    | P    | 42  | RST   | 1    | 62  | R6   | В    | 82  | B2   | В    |

| 3   | CB0  | В    | 23  | Y3     | В    | 43  | DIR   |      | 63  | R7   | В    | 83  | B3   | В    |

| 4   | N.C. | -    | 24  | Y2     | B    | 44  | ŌĒ    |      | 64  | N.C. | -    | 84  | B4   | В    |

| 5   | N.C. | -    | 25  | Y1     | В    | 45  | SIGN  | 1    | 65  | N.C. | -    | 85  | VSS  | P    |

| 6   | CR7  | В    | 26  | YO     | В    | 46  | VSS   | Р    | 66  | G0   | В    | 86  | B5   | В    |

| 7   | CR6  | В    | 27  | N.C.   | -    | 47  | CMY   |      | 67  | VCC  | P    | 87  | B6   | В    |

| 8   | CR5  | В    | 28  | N.C.   | -    | 48  | CCIR  | 1    | 68  | G1   | В    | 88  | B7   | В    |

| 9   | CR4  | В    | 29  | N.C.   | -    | 49  | SRGB0 | В    | 69  | G2   | В    | 89  | N.C. | -    |

| 10  | VSS  | P    | 30  | N.C.   | -    | 50  | SRGB1 | В    | 70  | G3   | В    | 90  | VSS  | P    |

| 11  | CR3  | В    | 31  | SYC1   | В    | 51  | N.C.  | -    | 71  | G4   | В    | 91  | VCC  | P    |

| 12  | CR2  | В    | 32  | SYC0   | В    | 52  | N.C.  | -    | 72  | VSS  | Р    | 92  | N.C. | -    |

| 13  | CR1  | В    | 33  | MODE2  |      | 53  | N.C.  | -    | 73  | G5   | В    | 93  | CB7  | В    |

| 14  | CR0  | В    | 34  | MODE1  |      | 54  | N.C.  | -    | 74  | G6   | В    | 94  | CB6  | В    |

| 15  | N.C. | -    | 35  | MODE0  | 1    | 55  | R0    | В    | 75  | G7   | В    | 95  | CB5  | В    |

| 16  | VCC  | P    | 36  | VCC    | P    | 56  | R1    | В    | 76  | N.C. | -    | 96  | VSS  | P    |

| 17  | N.C. | -    | 37  | BYPASS | 1    | 57  | R2    | В    | 77  | N.C. | -    | 97  | CB4  | В    |

| 18  | Y7   | В    | 38  | CHS    | 1    | 58  | R3    | В    | 78  | B0   | В    | 98  | CB3  | В    |

| 19  | Y6   | В    | 39  | VSS    | P    | 59  | R4    | В    | 79  | N.C. | -    | 99  | CB2  | В    |

| 20  | Y5   | В    | 40  | CLK    | 1    | 60  | VSS   | Р    | 80  | N.C. | -    | 100 | CB1  | В    |

P = Power, I = Input, B = Bidirectional

Figure 25. ZR36011 Plastic Quad Flat Pack

Notes:

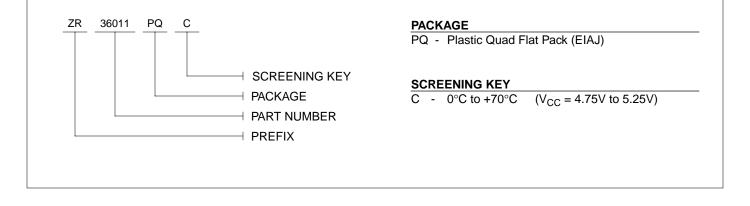

## **ORDERING INFORMATION**

# SALES OFFICES

- U.S. Headquarters Zoran Corporation 1705 Wyatt Drive Santa Clara, CA 95054 USA Telephone: 408-986-1314 FAX: 408-986-1240

- Israel Design Center Zoran Microelectronics, Ltd. Advanced Technology Center P.O. Box 2495 Haifa, 31024 Israel Telephone: 972-4-551-551 FAX: 972-4-551-550

- Japan Operations

Zoran Corporation

1-5-3 Ebisu Kogetsu Bldg.

4th Floor

Shibuya-Ku, Tokyo Japan

Telephone: 81-3-3448-1980

FAX: 81-3-3448-1690

The material in this data sheet is for information only. Zoran Corporation assumes no responsibility for errors or omissions and reserves the right to change, without notice, product specifications, operating characteristics, packaging, etc. Zoran

Corporation assumes no liability for damage resulting from the use of information contained in this document.