# REPETITIVE AVALANCHE AND dv/dt RATED HEXFET®TRANSISTORS THRU-HOLE (TO-39)

# IRLF120 100V, N-CHANNEL

### **Product Summary**

| Part Number | BVDSS | RDS(on)      | ΙD   |  |

|-------------|-------|--------------|------|--|

| IRLF120     | 100V  | $0.35\Omega$ | 5.3A |  |

The Logic Level 'L' series of power MOSFETs are designed to be operated with level logic gate-to-source voltage of 5V. In addition to the well established characteristics of HEXFETs<sup>®</sup>, they have the added advantage of providing low drive requirements to interface power loads to logic level IC's and microprocessors.

Fields of applications include: high speed power applications such as switching regulators, switching converters, motor drivers, solenoid and relay drivers and drivers for high power bipolar switching transistors requiring high speed and low gatedrive voltage.

The HEXFET technology is the key to International Rectifier's advanced line of logic level power MOSFET transistors. The efficient geometry and unique processing of the HEXFET achieve very low on-state resistance combined with high transconductance and great device ruggedness.

#### Features:

- Repetitive Avalanche Ratings

- Dynamic dv/dt Rating

- Low Drive Requirements

- Execellent Temperature Stability

- Fast Switching Speeds

- Ease of Paralleling

- Hermetically Sealed

- Light Weight

## **Absolute Maximum Ratings**

|                                        | Parameter                       |                                           | Units |  |

|----------------------------------------|---------------------------------|-------------------------------------------|-------|--|

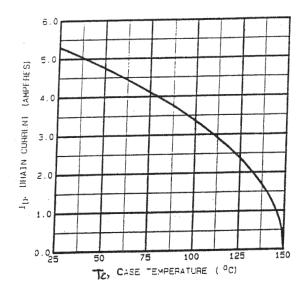

| ID @ VGS = 5.0V, TC = 25°C             | Continuous Drain Current        | 5.3                                       |       |  |

| ID @ VGS = 5.0V, TC = 100°C            | Continuous Drain Current        | 3.4                                       | Α     |  |

| IDM                                    | Pulsed Drain Current ①          | 21                                        |       |  |

| P <sub>D</sub> @ T <sub>C</sub> = 25°C | Max. Power Dissipation          | 20                                        | W     |  |

|                                        | Linear Derating Factor          | 0.16                                      | W/°C  |  |

| VGS                                    | Gate-to-Source Voltage          | ±10                                       | V     |  |

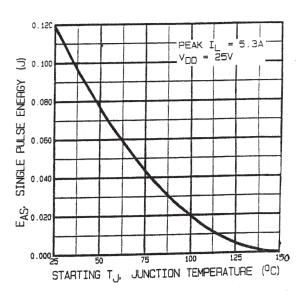

| EAS                                    | Single Pulse Avalanche Energy 2 | 120                                       | mJ    |  |

| IAR                                    | Avalanche Current ①             | 5.3                                       | Α     |  |

| EAR                                    | Repetitive Avalanche Energy ①   | 2.0                                       | mJ    |  |

| dv/dt                                  | Peak Diode Recovery dv/dt 3     | 5.5                                       | V/ns  |  |

| TJ                                     | Operating Junction              | -55 to 150                                |       |  |

| TSTG Storage Temperature Range         |                                 |                                           | °C    |  |

|                                        | Lead Temperature                | 300 (0.063 in. (1.6mm) from case for 10s) |       |  |

|                                        | Weight                          | 0.98 (typical)                            | g     |  |

For footnotes refer to the last page

## Electrical Characteristics @ Tj = 25°C (Unless Otherwise Specified)

|                                |                                              |     |      |      | •     |                                                                                                      |

|--------------------------------|----------------------------------------------|-----|------|------|-------|------------------------------------------------------------------------------------------------------|

|                                | Parameter                                    | Min | Тур  | Max  | Units | <b>Test Conditions</b>                                                                               |

| BVDSS                          | Drain-to-Source Breakdown Voltage            | 100 | _    | _    | V     | VGS = 0V, ID = 250μA                                                                                 |

| ΔBVDSS/ΔTJ                     | Temperature Coefficient of Breakdown Voltage | _   | 0.13 | _    | V/°C  | Reference to 25°C, ID = 250μA                                                                        |

| RDS(on)                        | Static Drain-to-Source On-State              | _   | _    | 0.35 |       | VGS = 5.0V, ID = 3.4A ④                                                                              |

|                                | Resistance                                   | _   | _    | 0.42 | Ω     | $V_{GS} = 4.0V, I_{D} = 2.7A \oplus$                                                                 |

| VGS(th)                        | Gate Threshold Voltage                       | 1.0 | _    | 2.0  | V     | V <sub>DS</sub> = V <sub>GS</sub> , I <sub>D</sub> = 250μA                                           |

| 9fs                            | Forward Transconductance                     | 3.1 | _    | _    | S     | V <sub>DS</sub> = 50V, I <sub>DS</sub> = 3.4A ④                                                      |

| IDSS                           | Zero Gate Voltage Drain Current              |     | _    | 250  |       | V <sub>DS</sub> = 100V, V <sub>GS</sub> = 0V                                                         |

|                                |                                              | _   | _    | 1000 | μΑ    | V <sub>DS</sub> = 80V                                                                                |

|                                |                                              |     |      |      |       | VGS = 0V, TJ = 125°C                                                                                 |

| IGSS                           | Gate-to-Source Leakage Forward               | _   | _    | 100  |       | VGS = 10V                                                                                            |

| IGSS                           | Gate-to-Source Leakage Reverse               | _   | _    | -100 | nA    | VGS = -10V                                                                                           |

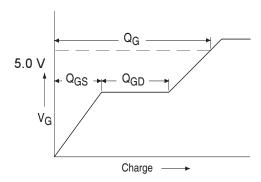

| Qg                             | Total Gate Charge                            | _   | _    | 13   |       | Vgs = 5.0V, ID = 5.3A                                                                                |

| Qgs                            | Gate-to-Source Charge                        |     | _    | 2.4  | nC    | V <sub>DS</sub> = 80V                                                                                |

| Q <sub>gd</sub>                | Gate-to-Drain ('Miller') Charge              | _   | _    | 7.1  |       |                                                                                                      |

| td(on)                         | Turn-On Delay Time                           | _   | _    | 13   |       | $V_{DD} = 50V, I_{D} = 5.3A,$                                                                        |

| tr                             | Rise Time                                    |     | _    | 73   |       | $V_{GS} = 5.0V$ , $R_{G} = 18\Omega$                                                                 |

| <sup>t</sup> d(off)            | Turn-Off Delay Time                          | _   | _    | 41   | ns    |                                                                                                      |

| tf                             | Fall Time                                    |     | _    | 27   |       |                                                                                                      |

| L <sub>S+</sub> L <sub>D</sub> | Total Inductance                             | _   | 7.0  | _    | nH    | Measured from drain lead (6mm/<br>0.25in. from package) to source lead<br>(6mm/0.25in. from package) |

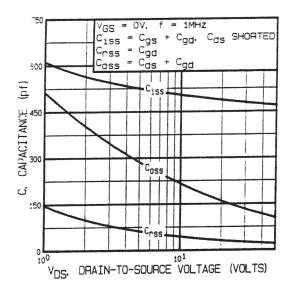

| Ciss                           | Input Capacitance                            |     | 480  |      |       | VGS = 0V, VDS = 25V                                                                                  |

| Coss                           | Output Capacitance                           | _   | 150  | _    | pF    | f = 1.0MHz                                                                                           |

| C <sub>rss</sub>               | Reverse Transfer Capacitance                 | _   | 30   | _    |       |                                                                                                      |

# Source-Drain Diode Ratings and Characteristics

|     | Parameter                              |                                                                                             | Min | Тур | Max | Units | Test Conditions                                      |

|-----|----------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------------------------------------------------|

| Is  | Continuous Source Current (Body Diode) |                                                                                             | _   | _   | 5.3 | А     |                                                      |

| ISM | Pulse Source Current (Body Diode) ①    |                                                                                             | _   | _   | 21  |       |                                                      |

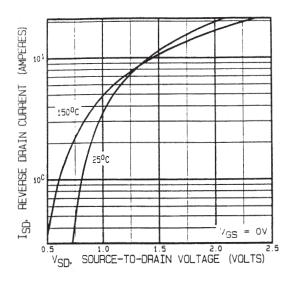

| VSD | Diode Forward Voltage                  |                                                                                             | _   | _   | 2.5 | V     | $T_j = 25^{\circ}C$ , $I_S = 5.3A$ , $V_{GS} = 0V$ ④ |

| trr | Reverse Recovery Time                  |                                                                                             | _   | _   | 220 | ns    | $T_j$ = 25°C, I <sub>F</sub> = 5.3A, di/dt ≤ 100A/μs |

| QRR | Reverse Recovery Charge                |                                                                                             | _   | _   | 1.1 | μC    | V <sub>DD</sub> ≤ 50V ④                              |

| ton | Forward Turn-On Time                   | Intrinsic turn-on time is negligible. Turn-on speed is substantially controlled by LS + LD. |     |     |     |       |                                                      |

## **Thermal Resistance**

|                    | Parameter           | Min | Тур | Max  | Units | Test Conditions       |

|--------------------|---------------------|-----|-----|------|-------|-----------------------|

| RthJC              | Junction-to-Case    | _   | _   | 6.25 | °C/W  |                       |

| R <sub>th</sub> JA | Junction-to-Ambient | _   | _   | 175  | C/ VV | Typical socket mount. |

Note: Corresponding Spice and Saber models are available on International Rectifier website.

For footnotes, refer to the last page

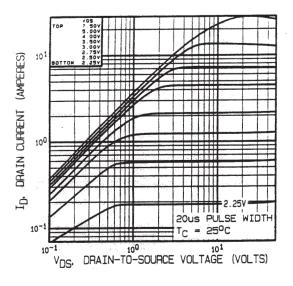

Fig 1. Typical Output Characteristics

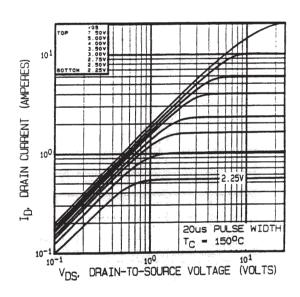

Fig 2. Typical Output Characteristics

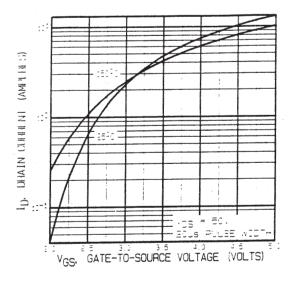

Fig 3. Typical Transfer Characteristics

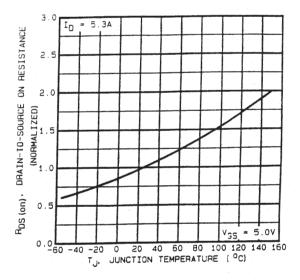

**Fig 4.** Normalized On-Resistance Vs. Temperature

**Fig 5.** Typical Capacitance Vs. Drain-to-Source Voltage

**Fig 6.** Typical Gate Charge Vs. Gate-to-Source Voltage

**Fig 7.** Typical Source-Drain Diode Forward Voltage

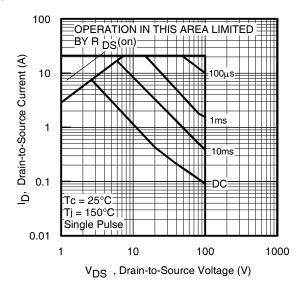

Fig 8. Maximum Safe Operating Area

**Fig 9.** Maximum Drain Current Vs. Case Temperature

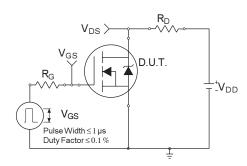

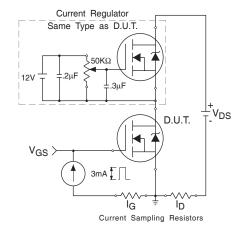

Fig 10a. Switching Time Test Circuit

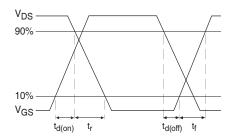

Fig 10b. Switching Time Waveforms

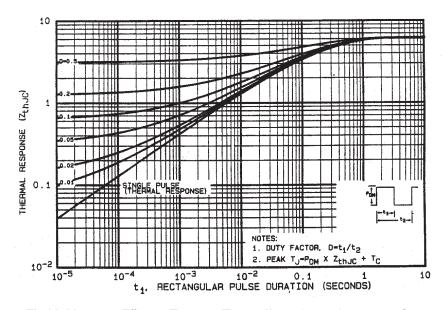

Fig 11. Maximum Effective Transient Thermal Impedance, Junction-to-Case

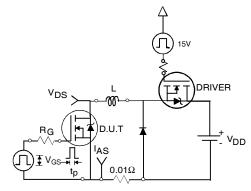

Fig 12a. Unclamped Inductive Test Circuit

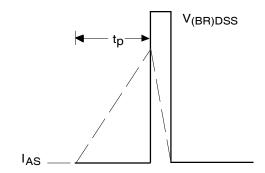

Fig 12b. Unclamped Inductive Waveforms

Fig 13a. Basic Gate Charge Waveform

**Fig 12c.** Maximum Avalanche Energy Vs. Drain Current

Fig 13b. Gate Charge Test Circuit

### Footnotes:

- ① Repetitive Rating; Pulse width limited by maximum junction temperature.

- $^{\circ}$  V<sub>DD</sub> = 25 V, Starting T<sub>J</sub> = 25°C, L= 6.1mH Peak I<sub>AS</sub> = 5.3A, V<sub>GS</sub> =5.0V, R<sub>G</sub>= 25 $\Omega$

- 3 ISD ≤ 5.3A, di/dt ≤ 110A/μs, VDD≤ 100V, TJ ≤ 150°C Suggested RG =18 Ω

- 4 Pulse width  $\leq 300 \,\mu s$ ; Duty Cycle  $\leq 2\%$

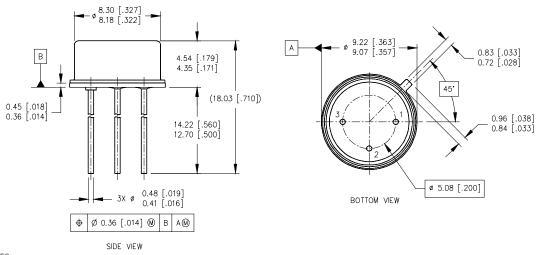

# Case Outline and Dimensions —TO-205AF (TO-39)

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME 14.5M-1994.

- 2. DIMENSIONS ARE SHOWN IN MILLIMETERS [INCHES].

- 3. CONTROLLING DIMENSION: INCH.

- 4. CONFORMS TO JEDEC OUTLINE TO-205AF (TO-39).

#### **LEGEND**

- 1- SOURCE

- 2- GATE

- 3- DRAIN

# International TOR Rectifier

IR WORLD HEADQUARTERS: 101 N. Sepulveda Blvd., El Segundo, California 90245, USA Tel: (310) 252-7105 IR LEOMINSTER: 205 Crawford St., Leominster, Massachusetts 01453, USA Tel: (978) 534-5776

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information. Data and specifications subject to change without notice. 09/2014