**Data Sheet**

# **Complete AV Front End**

# **ADV7850**

#### **FEATURES**

Main features 4-port HDMI Xpressview receiver 170 MHz video and graphics digitizer **Complete 3D comb video decoder** Stereo audio codec High speed serial output (TMDS) **HDMI** support **3D TV support** Audio return channel (ARC) Extended colorimetry, including sYCC601, Adobe RGB, Adobe YCC 601, and xvYCC extended gamut color 4:1 HDMI 297 MHz receiver Fast switching of HDMI ports (Xpressview) 3D TV video format support HDCP 1.4 support with internal HDCP keys Adaptive HDMI equalizer Full HDCP repeater support S/PDIF interface for 4 single-mode ARC outputs Up to 36-bit Deep Color support **Complete HDMI audio support** Audio extraction available Support for up to 16 VSIs (including THX Media Director<sup>™</sup>) High speed serial output (TMDS 297 MHz) Full transmitter support including encryption Can operate in a transceiver configuration Audio insertion available Video and graphics digitizer Digitizes RGB graphics up to 1600 × 1200 at 60 Hz (UXGA) SD, ED, and HD TV support up to 1080p at 60 Hz Low refresh rates (24 Hz/25 Hz/30 Hz) support for 720p/1080p 13-channel analog video input channels with 2 outputs 3D comb video decoder Full NTSC/PAL/SECAM color standards support Adaptive 3D comb filter video decoder Advanced time-base correction (TBC) with frame synchronization for SD formats **Complete SCART support Advanced VBI data slicer IF** compensation filters

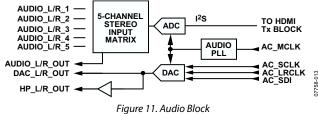

#### Audio codec

24-bit, 48 kHz stereo codec

5-channel stereo analog input mux with a stereo output General

Internal EDID RAM for HDMI and graphics

Dual STDI (standard identification) function support for dual input detection

Simultaneous analog processing and HDMI monitoring for fast input switching

#### **APPLICATIONS**

HDTVs, set-top boxes, AV receivers, projectors, video matrix switchers

#### FUNCTIONAL BLOCK DIAGRAM

#### DDR2 SDRAM CVBS × 2/YC SCART RGB CVBS ADC CVBS SDP HS/VS/DE SCART G CVBS ADC CVBS СІК 3D COMB SCART B YC YC ADC DATA SCART SCART R YPbPr ADC номі GRAPHICS RGB СР Y/G HS/VS/DE YPbPr 25p/625p AUDIO L/R Pb/B CLK 720p/1080i MUX 1080p/ DATA Pb/R UXGA AUDIO L/R z RGB AUDIO ADC AUDIO L/R I<sup>2</sup>S INTERFACE DAC HP L/R HDMI 1 36 TMDS l<sup>2</sup>S DDC DEEP COLOR HDMI Rx HDMI 2 S/PDIF TMDS DDC DSD/DST MCLK HDMI 3 TMDS HBR DDC MCLK SCLK HDMI 4 TMDS FAST SWITCH SCLK DDC HDCP KEYS ARC S/PDIE ARC 5V HDMI + VGA 5V EDID SPI INTERFACE ADV7850 REG 7758-EDID EPROM Figure 1.

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### TABLE OF CONTENTS

| Features 1                                    |

|-----------------------------------------------|

| Applications1                                 |

| Functional Block Diagram 1                    |

| Revision History 2                            |

| General Description                           |

| Detailed Functional Block Diagram 4           |

| Specifications                                |

| Electrical Characteristics                    |

| Power Specifications                          |

| Analog Specifications7                        |

| Video Specifications                          |

| Timing Characteristics10                      |

| Timing Diagrams11                             |

| Absolute Maximum Ratings13                    |

| Package Thermal Performance13                 |

| ESD Caution13                                 |

| Pin Configuration and Function Descriptions14 |

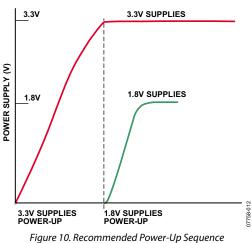

| Power Supply Sequencing                       |

### Analog Audio MUX Functionality ...... 28

### **REVISION HISTORY**

5/12—Revision 0: Initial Version

### **GENERAL DESCRIPTION**

The ADV7850 is a high quality, single chip, multiformat video decoder graphics digitizer with an integrated 4:1 multiplexed HDMI<sup>\*</sup> receiver.

This multiformat 3D comb filter decoder supports the conversion of PAL, NTSC, and SECAM standards in the form of a composite or an S-Video input signal into a HDMI output stream. SCART and overlay functionality are enabled by the ability of the ADV7850 to process CVBS and standard definition RGB signals simultaneously.

The ADV7850 contains one main component processor (CP) that processes YPrPb and RGB component formats, including RGB graphics. The ADV7850 can operate in quad HDMI and analog input mode, thus allowing for fast switching between the analog video inputs and HDMI.

The ADV7850 supports the decoding of a component RGB/ YPrPb video signal into a HDMI output stream. The support for component video includes 525i, 625i, 525p, 625p, 720p, 1080i, 1080p, and 1250i standards, as well as many other SMPTE and HD standards.

The ADV7850 supports graphics digitization. The ADV7850 is capable of digitizing RGB graphics signals from VGA to UXGA rates and converting them into an HDMI output stream. Internal EDID RAM is available for one graphics port.

The ADV7850 incorporates a quad input HDMI-compatible receiver that supports all HDTV formats up to 3D 1080p 60 Hz and 2160P 24 Hz.

The ADV7850 supports full HDCP decryption with internal key storage. The ADV7850 features HDCP authentication on all ports simultaneously. The feature allows fast switching between HDMI ports. Sync measurements and status monitoring are also available for all HDMI ports. Each HDMI port has dedicated 5 V detect and hot plug assert pins. The HDMI receiver also includes an integrated equalizer that ensures robust operation of the interface with cable lengths up to 30 meters. The HDMI receiver has advanced audio functionality, such as a mute flag, that prevents audible extraneous noise in the audio output.

In addition, the HDMI receiver incorporates internal EDID support, which can be made available in full power, powerdown, and power-off modes. An internal regulator supplies external EDID memory from the HDMI 5 V signal in poweroff mode.

The ADV7850 incorporates Xpressview<sup>™</sup> fast switching on all HDMI input ports. Using the Analog Devices, Inc., hardwarebased HDCP engine that minimizes software overhead, Xpressview technology allows fast switching between any two HDMI input ports in less than 1 second.

The ADV7850 offers a flexible audio output port for the audio data decoded from the HDMI stream. HDMI audio formats, including super audio CD (SACD) via DSD, DST, and HBR are supported.

The ADV7850 also features the single mode audio return channel (ARC) feature. ARC simplifies cabling by combining upstream audio capability in a conventional HDMI cable.

The stereo audio ADC converts analog audio inputs and provides the data to the back end via the HDMI interface. The stereo audio DAC receives I<sup>2</sup>S data from the back end and converts it to analog audio output. The audio output is available as both high impedance and a driven output, which is suitable for driving headphones directly.

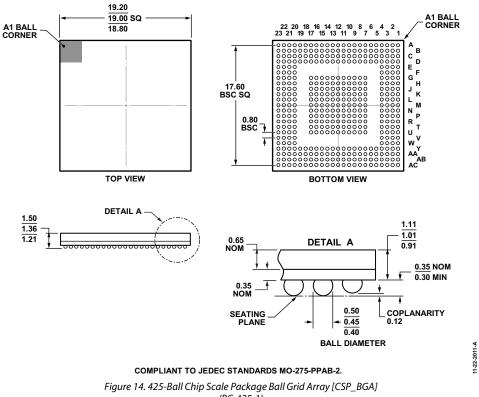

Fabricated in an advanced CMOS process, the ADV7850 is provided in a 19 mm  $\times$  19 mm, 425-ball, CSP\_BGA, surfacemount, RoHS-compliant package, and is specified over the  $-20^{\circ}$ C to  $+70^{\circ}$ C temperature range.

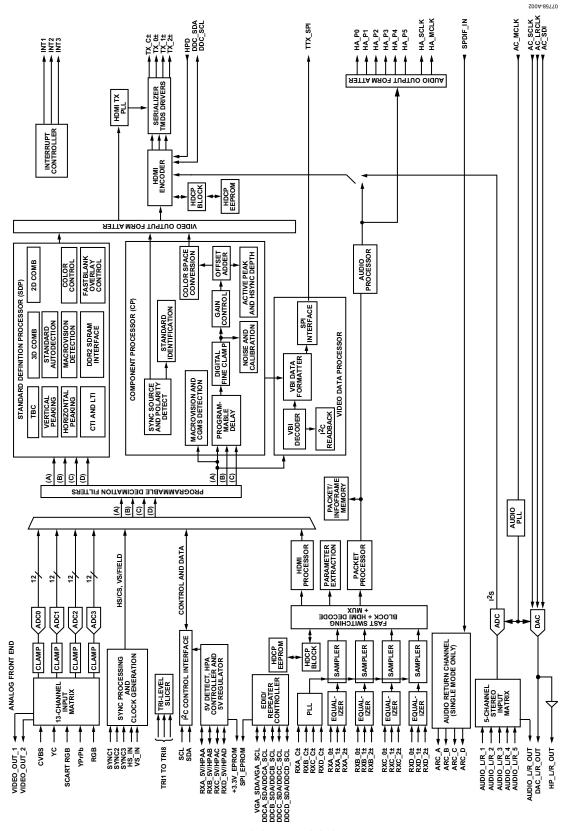

### DETAILED FUNCTIONAL BLOCK DIAGRAM

Figure 2. Detailed Functional Block Diagram

### **SPECIFICATIONS**

AVDD =  $1.8 V \pm 5\%$ , VDD to GND =  $1.8 V \pm 5\%$ , PVDD =  $1.8 V \pm 5\%$ , TX\_AVDD =  $1.8 V \pm 5\%$ , TX\_PVDD =  $1.8 V \pm 5\%$ , SAVDD =  $1.8 V \pm 5\%$ , SDVDD =  $1.8 V \pm 5\%$ , CVDD =  $1.8 V \pm 5\%$ , DVDDIO =  $3.3 V \pm 5\%$ , TX\_VDD33 =  $3.3 V \pm 5\%$ , TVDD =  $3.3 V \pm 5\%$ , AC\_AVDD =  $3.3 V \pm 5\%$ . T<sub>MIN</sub> to T<sub>MAX</sub> =  $-20^{\circ}$ C to  $+70^{\circ}$ C, unless otherwise noted.

### **ELECTRICAL CHARACTERISTICS**

Table 1.

| Parameter                                  | Symbol            | Test Conditions/Comments                                                                                                           | Min | Тур          | Max | Unit |

|--------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|-----|------|

| STATIC PERFORMANCE                         |                   |                                                                                                                                    |     |              |     |      |

| Resolution (Each ADC)                      | N                 |                                                                                                                                    |     |              | 12  | Bits |

| Integral Nonlinearity                      | INL               | 27 MHz (at a 12-bit level)                                                                                                         |     | -3.0 to +8.0 |     | LSB  |

|                                            |                   | 54 MHz (at a 12-bit level)                                                                                                         |     | -3.0 to +8.0 |     | LSB  |

|                                            |                   | 74.25 MHz (at a 12-bit level)                                                                                                      |     | -4.0 to +7.0 |     | LSB  |

|                                            |                   | 108 MHz (at a 11-bit level)                                                                                                        |     | -3.5 to +8.0 |     | LSB  |

|                                            |                   | 170 MHz (at a 9-bit level)                                                                                                         |     | -0.7 to +1.8 |     | LSB  |

| Differential Nonlinearity                  | DNL               | 27 MHz (at a 12-bit level)                                                                                                         |     | -0.7 to +0.8 |     | LSB  |

|                                            |                   | 54 MHz (at a 12-bit level)                                                                                                         |     | -0.7 to +0.8 |     | LSB  |

|                                            |                   | 75 MHz (at a 12-bit level)                                                                                                         |     | -0.7 to +0.8 |     | LSB  |

|                                            |                   | 108 MHz (at a 11-bit level)                                                                                                        |     | -0.7 to +0.8 |     | LSB  |

|                                            |                   | 170 MHz (at a 9-bit level)                                                                                                         |     | -0.6 to +0.5 |     | LSB  |

| DIGITAL INPUTS                             |                   |                                                                                                                                    |     |              |     |      |

| Input High Voltage                         | V <sub>IH</sub>   | XTALN and XTALP pins                                                                                                               | 1.2 |              |     | V    |

| Input Low Voltage                          | VIL               | XTALN and XTALP pins                                                                                                               |     |              | 0.4 | V    |

|                                            | V <sub>IH</sub>   | Other digital inputs                                                                                                               | 2   |              |     | V    |

|                                            | VIL               | Other digital inputs                                                                                                               |     |              | 0.8 | V    |

| Input Capacitance                          | C <sub>IN</sub>   |                                                                                                                                    |     |              | 10  | pF   |

| HDMI                                       |                   |                                                                                                                                    |     |              |     |      |

| TMDS Differential Pin Capacitance          |                   |                                                                                                                                    |     | 0.3          |     | pF   |

| DIGITAL INPUTS (5 V TOLERANT) <sup>1</sup> |                   |                                                                                                                                    |     |              |     |      |

| Input High Voltage                         | VIH               |                                                                                                                                    | 3.0 |              |     | V    |

| Input Low Voltage                          | V                 |                                                                                                                                    |     |              | 0.8 | V    |

| Input Current                              | I <sub>IN</sub>   |                                                                                                                                    | -82 |              | +82 | μA   |

| DIGITAL OUTPUTS                            |                   |                                                                                                                                    |     |              |     |      |

| Output High Voltage                        | V <sub>OH</sub>   |                                                                                                                                    | 2.4 |              |     | V    |

| Output Low Voltage                         | V <sub>oL</sub>   |                                                                                                                                    |     |              | 0.4 | V    |

| High Impedance Leakage Current             | I <sub>LEAK</sub> | DDC_SCL, DDCA_SDA, DDCB_SCL,<br>DDCB_SDA, DDCC_SCL,<br>DDCC_SDA, DDCD_SCL,<br>DDCD_SDA, VGA_SCL, VGA_SDA,<br>SPDIF_IN, SHARED_EDID |     | 30           |     | μA   |

|                                            | I <sub>LEAK</sub> | RXA_5V, RXB_5V, RXC_5V, RXD_5V<br>and VGA_5V                                                                                       |     | 20           |     | μA   |

|                                            | ILEAK             | All other digital pins                                                                                                             |     | 10           |     | μA   |

| Output Capacitance                         | C <sub>OUT</sub>  |                                                                                                                                    |     |              | 20  | pF   |

<sup>1</sup> The following pins are 5 V tolerant: HS\_IN1/TRI7, HS\_IN2/TRI5, VS\_IN1/TRI8, VS\_IN2/TRI6, DDCA\_SCL, DDCA\_SDA, DDCB\_SCL, DDCB\_SDA, DDCC\_SCL, DDCC\_SDA, DDCD\_SCL, DDCD\_SDA, VGA\_SCL, VGA\_SDA, TX\_DDC\_SCL, TX\_DDC\_SDA, RXA\_5V, RXB\_5V, RXC\_5V, RXD\_5V, and VGA\_5V.

### **POWER SPECIFICATIONS**

#### Table 2.

| Parameter                              | Symbol                | Min  | Тур | Max  | Unit | Test Conditions/Comments |

|----------------------------------------|-----------------------|------|-----|------|------|--------------------------|

| POWER REQUIREMENTS                     |                       |      |     |      |      |                          |

| Digital Core Power Supply              | VDD                   | 1.75 | 1.8 | 1.85 | V    |                          |

| Digital I/O Power Supply               | DVDDIO                | 3.14 | 3.3 | 3.46 | V    |                          |

| Memory Interface Analog Power Supply   | SAVDD                 | 1.71 | 1.8 | 1.89 | V    |                          |

| Memory Interface Digital Power Supply  | SDVDD                 | 1.71 | 1.8 | 1.89 | V    |                          |

| DPLL Power Supply                      | PVDD                  | 1.71 | 1.8 | 1.89 | V    |                          |

| Video Analog Power Supply              | AVDD                  | 1.71 | 1.8 | 1.89 | V    |                          |

| Terminator Power Supply                | TVDD                  | 3.14 | 3.3 | 3.46 | V    |                          |

| Comparator Power Supply                | CVDD                  | 1.71 | 1.8 | 1.89 | V    |                          |

| Audio Block Supply                     | AC_AVDD               | 3.14 | 3.3 | 3.46 | V    |                          |

| HDMI Tx Analog Power Supply            | TX_AVDD               | 1.71 | 1.8 | 1.89 | V    |                          |

| HDMI Tx Digital Power Supply           | TX_PVDD               | 1.71 | 1.8 | 1.89 | V    |                          |

| HDMI Tx PLL Regulator Power Supply     | TX_VDD33              | 3.14 | 3.3 | 3.46 | V    |                          |

| CURRENT CONSUMPTION <sup>1, 2, 3</sup> |                       |      |     |      |      |                          |

| Digital Core Supply Current            | I <sub>VDD</sub>      |      | 400 | 440  | mA   |                          |

| Digital I/O Supply Current             | I <sub>DVDDIO</sub>   |      | 3   | 4    | mA   |                          |

| DPLL Supply Current                    | I <sub>PVDD</sub>     |      | 36  | 45   | mA   |                          |

| Video Analog Supply Current            | I <sub>AVDD</sub>     |      | 270 | 290  | mA   |                          |

| Memory Interface Analog Power Supply   | I <sub>SAVDD</sub>    |      | 4   | 5    | mA   |                          |

| Memory Interface Digital Power Supply  | I <sub>SDVDD</sub>    |      | 15  | 18   | mA   |                          |

| Comparator Supply Current              | I <sub>CVDD</sub>     |      | 300 | 350  | mA   |                          |

| Audio Block Supply Current             | I <sub>AC_AVDD</sub>  |      | 80  | 84   | mA   |                          |

| HDMI Tx Analog Supply Current          | I <sub>TX_AVDD</sub>  |      | 20  | 25   | mA   |                          |

| HDMI Tx Digital Supply Current         | I <sub>TX_PVDD</sub>  |      | 43  | 50   | mA   |                          |

| HDMI Tx PLL Regulator Supply Current   | I <sub>TX_VDD33</sub> |      | 2   | 5    | mA   |                          |

| Terminator Supply Current <sup>4</sup> | I <sub>TVDD</sub>     |      | 80  | 85   | mA   | One port connected       |

|                                        | 1000                  |      | 280 | 290  | mA   | Four ports connected     |

| Power-Down Currents⁵                   | IVDD                  |      | 1   |      | mA   |                          |

|                                        | I <sub>DVDDIO</sub>   |      | 1.5 |      | mA   |                          |

|                                        | I <sub>PVDD</sub>     |      | 0.5 |      | mA   |                          |

|                                        | I <sub>AVDD</sub>     |      | 0.5 |      | mA   |                          |

|                                        | I <sub>SAVDD</sub>    |      | 0.5 |      | mA   |                          |

|                                        | I <sub>SDVDD</sub>    |      | 0.5 |      | mA   |                          |

|                                        | I <sub>TVDD</sub>     |      | 0.5 |      | mA   |                          |

|                                        |                       |      | 0.5 |      | mA   |                          |

|                                        | I <sub>AC AVDD</sub>  |      | 1   |      | mA   |                          |

|                                        | I <sub>TX_AVDD</sub>  |      | 2.5 |      | mA   |                          |

|                                        | I <sub>TX_PVDD</sub>  |      | 0.5 |      | mA   |                          |

|                                        | I <sub>TX_VDD33</sub> |      | 0.5 |      | mA   |                          |

| Power-Up Time                          | t <sub>PWRUP</sub>    |      | 25  |      | ms   |                          |

<sup>1</sup> All maximum current values are guaranteed by characterization to assist in power supply design.

<sup>2</sup> Typical current consumption values are recorded with nominal voltage supply levels, SMPTE bar video pattern, and at room temperature.

<sup>3</sup> Maximum current consumption values are recorded with maximum rated voltage supply levels, MoireX video pattern, and at maximum rated temperature.

<sup>4</sup> Termination power supply includes TVDD current consumed off chip.

<sup>5</sup> Power-down mode entered by setting the I<sup>2</sup>C Bit POWER\_DOWN high.

### ANALOG SPECIFICATIONS

| Parameter                                                       | Test Conditions/Comments                            | Min | Тур         | Max  | Unit   |

|-----------------------------------------------------------------|-----------------------------------------------------|-----|-------------|------|--------|

| CLAMP CIRCUITRY <sup>1</sup>                                    |                                                     |     |             |      |        |

| Input Impedance                                                 | Clamps switched off                                 |     | 10          |      | MΩ     |

| Analog (AIN1 to AIN12)                                          |                                                     |     |             |      |        |

| ADC Midscale (CML)                                              |                                                     |     | 0.91        |      | v      |

| ADC Full-Scale Level                                            |                                                     |     | CML + 0.55  |      | v      |

| ADC Zero-Scale Level                                            |                                                     |     | CML – 0.55  |      | V      |

| ADC Dynamic Range                                               |                                                     |     | 1.1         |      | v      |

| Clamp Level (When Locked)                                       | Component input, Y signal                           |     | CML – 0.12  |      | v      |

|                                                                 | Component input, Pr signal                          |     | CML         |      | V      |

|                                                                 | Component input, Pb signal                          |     | CML         |      | V      |

|                                                                 | PC RGB input (R, G, B signals)                      |     | CML – 0.12  |      | v      |

|                                                                 | CVBS input                                          |     | CML – 0.205 |      | v      |

|                                                                 | SCART RGB input (R, G, B signals)                   |     | CML – 0.205 |      | v      |

|                                                                 | S-Video input (Y signal)                            |     | CML – 0.205 |      | v      |

|                                                                 | S-Video input (C signal)                            |     | CML         |      | v      |

| Large Clamp Source Current                                      | SDP only                                            |     | 0.3         |      | mA     |

| Large Clamp Sink Current                                        | SDP only                                            |     | 0.4         |      | mA     |

| Fine Clamp Source Current                                       | SDP only                                            |     | 9.4         |      | μΑ     |

| Fine Clamp Sink Current                                         | SDP only                                            |     | 8           |      | μΑ     |

|                                                                 |                                                     |     | 0           |      | μ      |

| Number of Channels                                              | Stereo pair                                         |     | 1           |      | Channe |

| Full-Scale Input Level                                          |                                                     |     | 50          |      | μA rms |

| Resolution                                                      |                                                     | 24  |             | Bits |        |

| Dynamic Range (Stereo Channel)                                  |                                                     |     | 24          |      | DILS   |

|                                                                 | 60 dBES with respect to full scale                  |     | 90          |      | dB     |

| A-Weighted                                                      | -60 dBFS with respect to full-scale<br>analog input |     | 90          |      | uв     |

| Total Harmonic Distortion + Noise (Stereo Channel)              | -3 dBFS with respect to full-scale                  | -85 |             | dB   |        |

|                                                                 | analog input                                        |     | 00          |      | ab l   |

| Gain Mismatch                                                   | Left- and right-channel gain<br>mismatch            |     | 0.2         |      | dB     |

| Crosstalk (Left to Right, Right to Left)                        |                                                     |     | -90         |      | dB     |

| Gain Error                                                      | Input signal = 2.8 V rms                            |     | -1.1        |      | dB     |

| Power Supply Rejection                                          | 1 kHz, 300 mV p-p signal at AVDD                    |     | -89         |      | dB     |

| AUDIO ADC DIGITAL DECIMATOR FILTER CHARACTERISTICS <sup>2</sup> | At 48 kHz, guaranteed by design                     |     |             |      |        |

| Pass Band                                                       | ······································              |     | 22.5        |      | kHz    |

| Pass-Band Ripple                                                |                                                     |     | ±0.0002     |      | dB     |

| Stop Band                                                       |                                                     |     | 26.5        |      | kHz    |

| Stop-Band Attenuation                                           |                                                     |     | 100         |      | dB     |

| Group Delay                                                     |                                                     |     | 1040        |      | μs     |

| AUDIO DAC SECTION <sup>2</sup>                                  |                                                     |     |             |      |        |

| Number of Auxiliary Output Channels                             | Stereo pair                                         |     | 1           |      | Channe |

| Resolution                                                      |                                                     |     | 24          |      | Bits   |

| Full-Scale Analog Output                                        |                                                     |     | 1.0         |      | Vrms   |

| Dynamic Range                                                   |                                                     |     | 1.0         |      | VIIIIS |

| A-Weighted                                                      | –60 dBFS with respect to full-<br>scale code input  |     | 93          |      | dB     |

| Total Harmonic Distortion + Noise                               | -3 dBFS with respect to full-scale code input       |     | -89         |      | dB     |

| Parameter                                                              | <b>Test Conditions/Comments</b>                    | Min Typ | Мах | Unit    |

|------------------------------------------------------------------------|----------------------------------------------------|---------|-----|---------|

| Crosstalk (Left to Right, Right to Left)                               |                                                    | -104    |     | dB      |

| Interchannel Gain Mismatch                                             | Left- and right-channel gain<br>mismatch           | 0.1     |     | dB      |

| Gain Error                                                             | 1 V rms output                                     | 0.525   |     | dB      |

| Power Supply Rejection                                                 | 1 kHz, 300 mV p-p signal at AVDD                   | -101    |     | dB      |

| AUDIO DAC DIGITAL INTERPOLATION FILTER<br>CHARACTERISTICS <sup>2</sup> | At 48 kHz, guaranteed by design                    |         |     |         |

| Pass Band                                                              |                                                    | 21.769  |     | kHz     |

| Pass-Band Ripple                                                       |                                                    | ±0.01   |     | dB      |

| Transition Band                                                        |                                                    | 23.95   |     | kHz     |

| Stop Band                                                              |                                                    | 26.122  |     | kHz     |

| Stop-Band Attenuation                                                  |                                                    | 75      |     | dB      |

| Group Delay                                                            |                                                    | 580     |     | μs      |

| HEADPHONE AMPLIFIER <sup>2</sup>                                       | Measured at headphone output with 32 $\Omega$ load |         |     |         |

| Number of Channels                                                     | Stereo pair                                        | 1       |     | Channel |

| Dynamic Range                                                          |                                                    |         |     |         |

| A-Weighted                                                             | –60 dBFS with respect to full-<br>scale code input | 92      |     | dB      |

| Total Harmonic Distortion + Noise                                      | –3 dBFS with respect to full-scale code input      | -86     |     | dB      |

| Interchannel Gain Mismatch                                             |                                                    | 0.1     |     | dB      |

| Power Supply Rejection                                                 | 1 kHz, 300 mV p-p signal at AVDD                   | -82     |     | dB      |

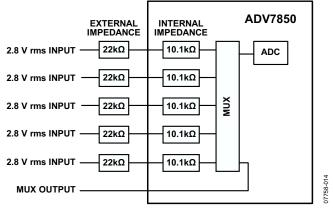

| ANALOG AUDIO MUX <sup>2</sup>                                          |                                                    |         |     |         |

| Number of Input Channels                                               | Stereo pair                                        | 5       |     | Channel |

| Number of Output Channels                                              | Stereo pair                                        | 1       |     | Channel |

| Gain Mismatch Between Left and Right Channels                          |                                                    | ±5      |     | %       |

| REFERENCE SECTION                                                      |                                                    |         |     |         |

| Absolute Voltage V <sub>RFF</sub>                                      |                                                    | 1.5     |     | V       |

$^{\rm 1}$  Specified for external clamp capacitor of 100 nF.  $^{\rm 2}$  Guaranteed by lab characterization.

### **VIDEO SPECIFICATIONS**

#### Table 4.

| Parameter                                   | Symbol          | Test Conditions/Comments         | Min | Тур  | Max | Unit    |

|---------------------------------------------|-----------------|----------------------------------|-----|------|-----|---------|

| NONLINEAR SPECIFICATIONS <sup>1</sup>       |                 |                                  |     |      |     | 1       |

| Differential Phase                          | DP              | CVBS input (modulated five-step) |     | 0.5  |     | Degrees |

| Differential Gain                           | DG              | CVBS input (modulated five-step) |     | 0.6  |     | %       |

| Luma Nonlinearity                           | LNL             | CVBS input (modulated five-step) |     | 0.9  |     | %       |

| NOISE SPECIFICATIONS <sup>1</sup>           |                 | Measured at 27 MHz LLC           |     |      |     |         |

| SNR Unweighted                              |                 | Luma ramp                        |     | 59   |     | dB      |

| SNR Unweighted                              |                 | Luma flat field                  |     | 60   |     | dB      |

| Analog Front-End Crosstalk                  |                 |                                  |     | 60   |     | dB      |

| LOCK TIME SPECIFICATIONS (SDP) <sup>2</sup> |                 |                                  |     |      |     |         |

| Horizontal Lock Range                       |                 |                                  |     | ±5   |     | %       |

| Vertical Lock Range                         |                 |                                  | 40  |      | 70  | Hz      |

| Subcarrier Lock Range                       | f <sub>sc</sub> |                                  |     | ±0.8 |     | kHz     |

| Color Lock-In Time                          |                 |                                  |     | 60   |     | Lines   |

| Sync Depth Range                            |                 |                                  | 20  |      | 200 | %       |

| Color Burst Range                           |                 |                                  | 1   |      | 200 | %       |

| Vertical Lock Time                          |                 |                                  |     | 300  |     | ms      |

| Horizontal Lock Time                        |                 |                                  |     | 100  |     | Lines   |

| CHROMA SPECIFICATIONS (SDP) <sup>1</sup>    |                 |                                  |     |      |     |         |

| Chroma Amplitude Error                      |                 |                                  |     | 0.9  |     | %       |

| Chroma Phase Error                          |                 |                                  |     | 0.3  |     | Degrees |

| Chroma Luma Intermodulation                 |                 |                                  |     | 0.6  |     | %       |

<sup>1</sup> Guaranteed by lab characterization. <sup>2</sup> Guaranteed by design.

### **TIMING CHARACTERISTICS**

### Data, SPI, and I<sup>2</sup>C Timing Characteristics

Table 5.

| Parameter                                     | Symbol                            | <b>Test Conditions/Comments</b>               | Min      | Тур  | Мах    | Unit         |

|-----------------------------------------------|-----------------------------------|-----------------------------------------------|----------|------|--------|--------------|

| CLOCK AND CRYSTAL                             |                                   |                                               |          |      |        |              |

| Crystal Frequency                             |                                   |                                               |          | 27   |        | MHz          |

| Crystal Frequency Stability                   |                                   |                                               |          |      | ±50    | ppm          |

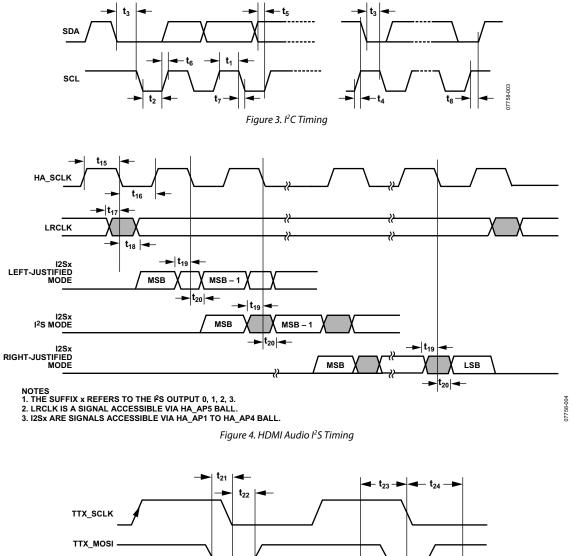

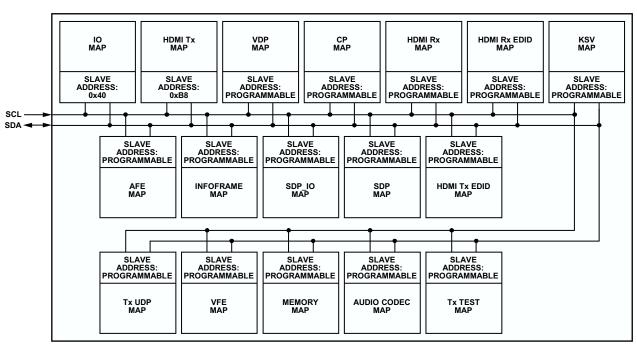

| I <sup>2</sup> C PORT <sup>1</sup>            |                                   | See Figure 3                                  |          |      |        |              |

| SCL Frequency                                 |                                   |                                               |          |      | 400    | kHz          |

| SCL Minimum Pulse Width High                  | t <sub>1</sub>                    |                                               | 600      |      |        | ns           |

| SCL Minimum Pulse Width Low                   | t <sub>2</sub>                    |                                               | 1.3      |      |        | μs           |

| Start Condition Hold Time                     | t <sub>3</sub>                    |                                               | 600      |      |        | ns           |

| Start Condition Setup Time                    | t <sub>4</sub>                    |                                               | 600      |      |        | ns           |

| SDA Setup Time                                | t <sub>5</sub>                    |                                               | 100      |      |        | ns           |

| SCL and SDA Rise Time                         | t <sub>6</sub>                    |                                               |          |      | 1000   | ns           |

| SCL and SDA Fall Time                         | t <sub>7</sub>                    |                                               |          |      | 300    | ns           |

| Stop Condition Setup Time                     | t <sub>8</sub>                    |                                               | 0.6      |      |        | μs           |

| RESET FEATURE                                 |                                   |                                               |          |      |        |              |

| Reset Pulse Width                             |                                   |                                               | 5        |      |        | ms           |

| HDMI AUDIO I <sup>2</sup> S PORT, MASTER MODE |                                   | See Figure 4                                  |          |      |        |              |

| HA_SCLK Mark-Space Ratio                      | t15:t16                           |                                               | 45:55    |      | 45:55  | % duty cycle |

| LRCLK <sup>2</sup> Data Transition Time       | t <sub>17</sub>                   | End of valid data to negative<br>HA_SCLK edge |          |      | 2      | ns           |

| LRCLK <sup>2</sup> Data Transition Time       | t <sub>18</sub>                   | Negative HA_SCLK edge to start of valid data  |          |      | 2      | ns           |

| I2Sx <sup>3</sup> Data Transition Time        | t19                               | End of valid data to negative<br>HA_SCLK edge |          |      | 2      | ns           |

| I2Sx <sup>3</sup> Data Transition Time        | t <sub>20</sub>                   | Negative HA_SCLK edge to start of valid data  |          |      | 2      | ns           |

| AUDIO CODEC MASTER CLOCK                      |                                   |                                               |          |      |        |              |

| AC_MCLK Frequency Range                       | <b>f</b> <sub>MCLK</sub>          |                                               | 4.096    |      | 24.576 | MHz          |

| AC_MCLK Frequency                             | <b>f</b> <sub>MCLK</sub>          |                                               | 128 × fs |      |        | Hz           |

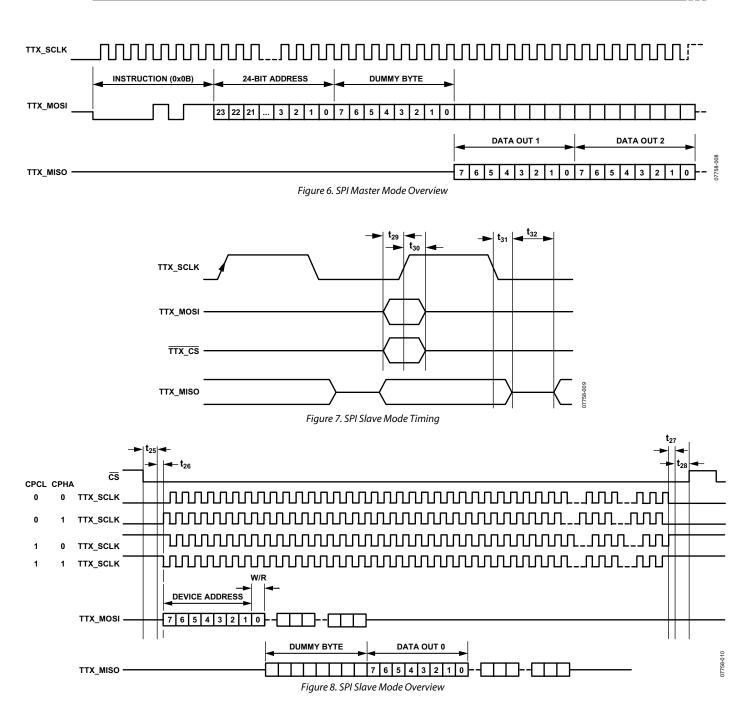

| SPI READ AND WRITE OPERATIONS <sup>1</sup>    |                                   | See Figure 5, Figure 7, and Figure 8          |          |      |        |              |

| SCLK Frequency                                |                                   |                                               |          | 13.5 |        | MHz          |

| Master Mode                                   |                                   |                                               |          |      |        |              |

| TTX_SCLK Falling Edge to<br>CS/TTX_MOSI Valid | t <sub>21</sub> , t <sub>22</sub> |                                               | 3.0      |      | 4.1    | ns           |

| TTX_MISO Setup Time                           | t <sub>23</sub>                   |                                               |          | 15.3 |        | ns           |

| TTX_MISO Hold Time                            | t <sub>24</sub>                   |                                               |          | 2.1  |        | ns           |

| Slave Mode                                    | -2.                               |                                               |          |      |        |              |

| CS Falling Edge to TTX_SCLK<br>Rising Edge    | t25, t26                          |                                               | 4.0      |      |        | ns           |

| TTX_SCLK Falling Edge to $\overline{CS}$      | t <sub>27</sub> , t <sub>28</sub> |                                               | 4.0      |      |        | ns           |

| Rising Edge                                   |                                   |                                               |          |      |        |              |

| TTX_MOSI Setup Time                           | t <sub>29</sub>                   |                                               |          | 1.8  |        | ns           |

| TTX_MOSI Hold Time                            | t <sub>30</sub>                   |                                               |          | 2.7  |        | ns           |

| TTX_SCLK Falling Edge to<br>CS/MOSI Valid     | t <sub>31</sub> , t <sub>32</sub> |                                               | 7.3      |      | 15.5   | ns           |

<sup>1</sup> Guaranteed by design.

<sup>2</sup> LRCLK is a signal accessible via HA\_AP5.

<sup>3</sup> I2Sx are signals accessible via Ball HA\_AP1 to Ball HA\_AP4.

#### **TIMING DIAGRAMS**

Figure 5. SPI Master Mode Timing

TTX\_CS

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

| 1 4010 01                                                                        |                            |

|----------------------------------------------------------------------------------|----------------------------|

| Parameter                                                                        | Rating                     |

| AVDD to GND                                                                      | 2.2 V                      |

| VDD to GND                                                                       | 2.2 V                      |

| PVDD to GND                                                                      | 2.2 V                      |

| TX_AVDD to GND                                                                   | 2.2 V                      |

| TX_PVDD to GND                                                                   | 2.2 V                      |

| SAVDD to GND                                                                     | 2.2 V                      |

| SDVDD to GND                                                                     | 2.2 V                      |

| CVDD to GND                                                                      | 2.2 V                      |

| DVDDIO to GND                                                                    | 4.0 V                      |

| TVDD to GND                                                                      | 4.0 V                      |

| AC_AVDD to GND                                                                   | 4.0 V                      |

| Maximum Difference Across All 1.8 V<br>Supplies                                  | –0.3 V to +0.3 V           |

| Maximum Difference Across All 3.3 V<br>Supplies                                  | –0.3 V to +0.3 V           |

| Maximum Difference Between 3.3 V<br>Domain Supplies and 1.8 V Domain<br>Supplies | –0.3 V to +2.2 V           |

| Digital Inputs Voltage to GND                                                    | -0.3 V to DVDDIO + 0.3 V   |

| Digital Outputs Voltage to GND                                                   | -0.3 V to DVDDIO + 0.3 V   |

| 5 V Tolerant Digital Inputs to GND <sup>1</sup>                                  | 5.5 V                      |

| Analog Inputs to GND                                                             | -0.3V to AVDD + 0.3 V-0.3V |

|                                                                                  | to AC_AVDD + 0.3 V         |

| XTALN and XTALP to GND                                                           | -0.3 V to PVDD + 0.3 V     |

| Maximum Junction Temperature (T <sub>J MAX</sub> )                               | 125°C                      |

| Storage Temperature Range                                                        | –65°C to +150°C            |

| Infrared Reflow Soldering (20 sec)                                               | 260°C                      |

<sup>1</sup> The following inputs are 3.3 V inputs but are 5 V tolerant: HS\_IN1/TRI7, HS\_IN2/TRI5, VS\_IN1/TRI8, VS\_IN2/TRI6, DDCA\_SCL, DDCA\_SDA, DDCB\_SCL, DDCB\_SDA, DDCC\_SCL, DDCC\_SDA, DDCD\_SCL, DDCD\_SDA, VGA\_SCL, VGA\_SDA, TX\_DDC\_SCL, TX\_DDC\_SDA, RXA\_5V, RXB\_5V, RXC\_5V, RXD\_5V and VGA\_5V.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL PERFORMANCE

To reduce power consumption when using the ADV7850, the user is advised to turn off unused sections of the part.

Due to PCB metal variation, and, therefore, variation in PCB heat conductivity, the value of  $\theta_{IA}$  may differ for various PCBs.

The most efficient measurement solution is obtained using the package surface temperature to estimate the die temperature because this eliminates the variance associated with the  $\theta_{IA}$  value.

The maximum junction temperature  $(T_{J MAX})$  of 125°C must not be exceeded. The following equation calculates the junction temperature using the measured package surface temperature and applies only when no heat sink is used on the device under test (DUT):

$T_{I} \quad T_{S} \quad \left( \Psi_{IT} \times \mathcal{H}_{TOTAL} \right)$

where:

$T_s$  is the package surface temperature (°C).  $\Psi_{TT} = 0.7^{\circ}$ C/W for the 425-ball CSP\_BGA.

$$\begin{split} W_{\text{TOTAL}} &= (PVDD \times I_{PVDD}) + (0.4 \times TVDD \times I_{TVDD}) + \\ (CVDD \times I_{CVDD}) + (AVDD \times I_{AVDD}) + (VDD \times I_{VDD}) + \\ (DVDDIO \times I_{DVDDIO}) + (TX\_AVDD \times I_{TX\_AVDD}) + \\ (TX\_PVDD \times I_{TX\_PVDD}) + (SAVDD \times I_{SAVDD}) + (SDVDD \times I_{SDVDD}) + (TX\_VDD33 \times I_{TX\_VDD33}) + (AC\_AVDD \times I_{AC\_AVDD}) \end{split}$$

where 0.4 reflects the 40% of TVDD power that is dissipated on the part itself.

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

|      | 1           | 2               | 3                          | 4              | 5      | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13           | 14    | 15    | 16      | 17      | 18            | 19      | 20      | 21      | 22                 | 23                 |        |

|------|-------------|-----------------|----------------------------|----------------|--------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-------|-------|---------|---------|---------------|---------|---------|---------|--------------------|--------------------|--------|

|      |             |                 |                            | -              |        |              |              |              |              | -            |              |              | -            |       |       |         |         | -             |         |         |         |                    |                    | •      |

|      | GND         | GND             | GND                        | RXB_2+         | RXB_1+ | RXB_0+       | RXB_C+       | ARC_B        | TVDD         | RXC_2+       | RXC_1+       | RXC_0+       | RXC_C+       | ARC_C | GND   | RXD_2+  | RXD_1+  | RXD_0+        | RXD_C+  | ARC_D   | GND     | GND<br>ACMUXO      | GND<br>ACMUXO      | A      |

| В    | ARC_A       | HPA_A           | GND                        | RXB_2-         | RXB_1- | RXB_0-       | RXB_C-       | HPA_B        | TVDD         | RXC_2-       | RXC_1-       | RXC_0-       | RXC_C-       | HPA_C | GND   | RXD_2-  | RXD_1-  | RXD_0-        | RXD_C-  | HPA_D   | GND     | UT_R               | UT_L<br>ACMUXIN    | В      |

| c    | RXA_C+      | RXA_C-          | CVDD                       | GND            | GND    | GND          | GND          | ROM          | TVDD         | TVDD         | TVDD         | TVDD         | TVDD         | TVDD  | GND   | TVDD    | TVDD    | TVDD          | TVDD    | GND     | GND     | _1R                | _1L                | C      |

| D    | RXA_0+      | RXA_0-          | CVDD                       | RXD_5V         | VGA_5V | DDCA_<br>SCL | DDCA_<br>SDA | DDCB_<br>SCL | DDCB_<br>SDA | DDCC_<br>SCL | DDCC_<br>SDA | DDCD_<br>SCL | DDCD_<br>SDA | VREG  | GND   | VGA_SCL | VGA_SDA | TVDD          | AC_AVDD | AC_AVDD | AC_AVDD | _2R                | ACMUXIN<br>_2L     | D      |

| E    | RXA_1+      | RXA_1-          | CVDD                       | RXC_5V         |        |              |              |              |              |              |              |              |              |       |       |         |         |               |         | GND     | GND     | ACMUXIN<br>_3R     | ACMUXIN<br>_3L     | E      |

| F    | RXA_2+      | RXA_2-          | CVDD                       | RXB_5V         |        |              |              |              |              |              |              |              |              |       |       |         |         |               |         | PLL_LF  | GND     | ACMUXIN<br>_4R     | ACMUXIN<br>_4L     | F      |

| G    | TVDD        | TVDD            | TVDD                       | TVDD           |        |              | GND          | TEST1        | CVDD         | CVDD         | CVDD         | CVDD         | CVDD         | CVDD  | CVDD  | GND     | GND     |               |         | AC_AVDD | GND     | ACMUXIN<br>_5R     | ACMUXIN<br>_5L     | G      |

| н    | EP_MISO     | EP_MOSI         | SPDIF_IN                   | RXA_5V         |        |              | GND          | GND   | GND   | GND     | GND     |               |         | GND     | GND     | FILTA              | VREF_AU<br>DIO     | н      |

| J    | EP_CS       | EP_SCK          | SHARED_<br>EDID            | RESET          |        |              | GND          | GND   | GND   | GND     | GND     |               |         | AC_AVDD | GND     | ISET               | FILTD              | J      |

| к    | GND         | GND             | DVDDIO                     | DVDDIO         |        |              | VDD          | GND          | GND          | GND          | GND          | GND          | GND          | GND   | GND   | GND     | GND     |               |         | AC_AVDD | AC_AVDD | AC<br>DACOŪT_<br>R | AC<br>DACOUT_<br>L | к      |

| L    | HA_AP5      | HA_SCLK         | INT1                       | SDA            |        |              | VDD          | GND          | GND          | GND          | GND          | GND          | GND          | GND   | GND   | GND     | GND     |               |         | AC_AVDD | AC_AVDD | HPOUT_R            | HPOUT_L            | L      |

| м    | HA_AP4      | HA_AP3/<br>INT3 | INT2                       | SCL            |        |              | VDD          | GND          | GND          | GND          | GND          | GND          | GND          | GND   | GND   | GND     | GND     |               |         | AC_AVDD | GND     | GND                | GND                | М      |

| N    | HA_AP2      | HA_AP1          | AC_MCLK                    | AC<br>LRCĪK    |        |              | VDD          | GND          | GND          | GND          | GND          | GND          | GND          | GND   | GND   | GND     | GND     |               |         | PVDD    | PVDD    | XTALN              | XTALP              | N      |

| Р    | HA_AP0      | HA_MCLK<br>OUT  | AC_SDI                     | AC_SCLK        |        |              | VDD          | GND          | GND          | GND          | GND          | GND          | GND          | GND   | GND   | GND     | GND     |               |         | GND     | GND     | GND                | GND                | Р      |

| R    | TTX<br>SCLK | TTX_<br>MOSĪ    | TTX_<br>MISŌ               | TTX_CS         |        |              | VDD          | GND          | GND          | GND          | GND          | GND          | GND          | GND   | GND   | GND     | GND     |               |         | GND     | GND     | REFN               | REFP               | R      |

| т    | DVDDIO      | DVDDIO          | GND                        | GND            |        |              | VDD          | GND          | GND          | GND          | GND          | GND          | GND          | GND   | GND   | GND     | GND     |               |         | AVDD    | AVDD    | AVDD               | AVDD               | т      |

| U    | TX_AVDD     | TX_AVDD         | GND                        | TX_DDC_<br>SCL |        |              | VDD          | TEST2 | GND   | GND     | GND     |               |         | AVIN13  | AVIN12  | AVIN11             | AVIN10             | U      |

| v    | TX_2+       | TX_2-           | GND                        | TX_DDC_<br>SDA |        |              |              |              |              |              |              |              |              |       |       |         |         |               |         | AVDD    | AVDD    | AVDD               | AVDD               | v      |

| w    | TX_1+       | TX_1-           | GND                        | TX_HPD         |        |              |              |              |              |              |              |              |              |       |       |         |         |               |         | GND     | AVOUT2  | AVIN9              | AVIN8              | w      |

| Y    | TX_0+       | TX_0-           | GND                        | GND            | A7     | A3           | A10          | BA0          | СКЕ          | GND          | DQ6          | DQ7          | DQ0          | DQ8   | UDQS  | SDVDD   | SAVDD   | TRI1          | TRI2    | GND     | AVOUT1  | SYNC3              | AVIN7              | Y      |

| AA   | TX_C+       | TX_C-           | тх                         | GND            | A9     | A5           | A1           | BA1          | WE           | GND          | DQ4          | DQ5          | DQ2          | DQ11  | UDQSN | SDVDD   | GND     | HS_IN1/       | VS_IN1/ | GND     | TRI3    | HS_IN2/            | VS_IN2/            | AA     |

| <br> |             | тх              |                            | SDVDD          | A11    | A6           | A2           | CAS          | RAS          | VREF         | SDVDD        | LDQSN        | DQ3          | DQ10  | DQ12  | DQ14    | GND     | TRI7<br>SYNC1 | TRI8    | GND     | SYNC2   | TRI5               | TRI6               | <br>AB |

|      | GND<br>GND  | TX<br>RTERM     | TX<br>PLVDD<br>TX<br>VDD33 | SDVDD          | A8     | A4           | A0           | ĒS           | ски          | ск           | SDVDD        | LDQS         | DQ1          | DQ10  | DQ12  | DQ14    | GND     | AVIN1         | AVIN3   | GND     | AVIN4   | AVIN5              | GND                |        |

| AC   |             |                 |                            |                |        |              |              |              |              |              |              |              |              |       |       |         |         |               |         |         |         |                    |                    | AC     |

|      | 1           | 2               | 3                          | 4              | 5      | 6            | 7            | 8            | 9            | 10           | 11           | 12           | 13           | 14    | 15    | 16      | 17      | 18            | 19      | 20      | 21      | 22                 | 23                 |        |

Figure 9. Pin Configuration

| Pin No.    | Mnemonic   | Description                                                         |

|------------|------------|---------------------------------------------------------------------|

| A1         | GND        | Ground.                                                             |

| A2         | GND        | Ground.                                                             |

| A3         | GND        | Ground.                                                             |

| A4         | RXB_2+     | Digital Input Channel 2 True of Port B in the HDMI Interface.       |

| A5         | RXB_1+     | Digital Input Channel 1 True of Port B in the HDMI Interface.       |

| A6         | RXB_0+     | Digital Input Channel 0 True of Port B in the HDMI Interface.       |

| A7         | RXB_C+     | Digital Input Clock True of Port B in the HDMI interface.           |

| A8         | ARC_B      | Single-Ended Audio Return Channel of Port B in the HDMI Interface.  |

| A9         | TVDD       | HDMI Termination Supply (3.3 V).                                    |

| A10        | RXC_2+     | Digital Input Channel 2 True of Port C in the HDMI Interface.       |

| A11        | RXC_1+     | Digital Input Channel 1 True of Port C in the HDMI Interface.       |

| A12        | RXC_0+     | Digital Input Channel 0 True of Port C in the HDMI Interface.       |

| A13        | <br>RXC_C+ | Digital Input Clock True of Port C in the HDMI Interface.           |

| A14        | ARC_C      | Single-Ended Audio Return Channel of Port C in the HDMI Interface.  |

| A15        | GND        | Ground.                                                             |

| A16        | RXD_2+     | Digital Input Channel 2 True of Port D in the HDMI Interface.       |

| A17        | RXD_1+     | Digital Input Channel 1 True of Port D in the HDMI Interface.       |

| A18        | RXD_0+     | Digital Input Channel 0 True of Port D in the HDMI Interface.       |

| A19        | RXD_C+     | Digital Input Clock True of Port D in the HDMI Interface.           |

| A20        | ARC_D      | Single-Ended Audio Return Channel of Port D in the HDMI Interface.  |

| A21        | GND        | Ground.                                                             |

| A22        | GND        | Ground.                                                             |

| A23        | GND        | Ground.                                                             |

| B1         | ARC_A      | Single-Ended Audio Return Channel of Port A in the HDMI Interface.  |

| B2         | HPA_A      | Hot Plug Assert for Port A.                                         |

| B3         | GND        | Ground.                                                             |

| B4         | RXB_2-     | Digital Input Channel 2 Complement of Port B in the HDMI Interface. |

| B5         | RXB_1-     | Digital Input Channel 1 Complement of Port B in the HDMI Interface. |

| B6         | RXB_0-     | Digital Input Channel 0 Complement of Port B in the HDMI Interface. |

| B7         | RXB_C-     | Digital Input Clock Complement of Port B in the HDMI Interface.     |

| B8         | HPA_B      | Hot Plug Assert for Port B.                                         |

| B9         | TVDD       | HDMI Termination Supply (3.3 V).                                    |

| B10        | RXC_2-     | Digital Input Channel 2 Complement of Port C in the HDMI Interface. |

| B11        | RXC_1-     | Digital Input Channel 1 Complement of Port C in the HDMI Interface. |

| B12        | RXC_0-     | Digital Input Channel 0 Complement of Port C in the HDMI Interface. |

| B12<br>B13 | RXC_C-     | Digital Input Clock Complement of Port C in the HDMI Interface.     |

| B14        | HPA_C      | Hot Plug Assert for Port C.                                         |

| B15        | GND        | Ground.                                                             |

| B16        | RXD_2-     | Digital Input Channel 2 Complement of Port D in the HDMI Interface. |

| B17        | RXD_1-     | Digital Input Channel 1 Complement of Port D in the HDMI Interface. |

| B18        | RXD_0-     | Digital Input Channel 0 Complement of Port D in the HDMI Interface. |

| B19        | RXD_C-     | Digital Input Clock Complement of Port D in the HDMI Interface.     |

| B20        | HPA_D      | Hot Plug Assert for Port D.                                         |

| B20<br>B21 | GND        | Ground.                                                             |

| B21<br>B22 | ACMUXOUT_R | Audio Codec Mux Output Right Channel.                               |

| B22<br>B23 | ACMUXOUT_K | Audio Codec Mux Output Left Channel.                                |

| 625<br>C1  | RXA_C+     | Digital Input Clock True of Port A in the HDMI Interface.           |

| C2         | RXA_C+     | Digital Input Clock Complement of Port A in the HDMI Interface.     |

| C2<br>C3   | CVDD       | HDMI Comparator Supply (1.8 V).                                     |

| C3<br>C4   | GND        | Ground.                                                             |

| C4<br>C5   | GND        | Ground.                                                             |

|            | GND        |                                                                     |

| Pin No. | Mnemonic   | Description                                                            |

|---------|------------|------------------------------------------------------------------------|

| C7      | GND        | Ground.                                                                |

| C8      | VDD_EEPROM | External EDID EEPROM Power Supply.                                     |

| C9      | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| C10     | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| C11     | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| C12     | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| C13     | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| C14     | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| C15     | GND        | Ground.                                                                |

| C16     | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| C17     | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| C18     | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| C19     | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| C20     | GND        | Ground.                                                                |

| C21     | GND        | Ground.                                                                |

| C22     | ACMUXIN_1R | Audio Codec Mux Input 1 Right Channel.                                 |

| C23     | ACMUXIN_1L | Audio Codec Mux Input 1 Left Channel.                                  |

| D1      | RXA_0+     | Digital Input Channel 0 True of Port A in the HDMI Interface.          |

| D2      | RXA_0-     | Digital Input Channel 0 Complement of Port A in the HDMI Interface.    |

| D3      | CVDD       | HDMI Comparator Supply (1.8 V).                                        |

| D4      | RXD_5V     | 5 V Detect Pin for Port D in the HDMI Interface.                       |

| D5      | VGA_5V     | 5 V Detect I/O for VGA Connector.                                      |

| D6      | DDCA_SCL   | Serial Clock for DDC Bus of Port A. DDCA_SCL is 5 V tolerant.          |

| D7      | DDCA_SDA   | Serial Data for DDC Bus of Port A. DDCA_SDA is 5 V tolerant.           |

| D8      | DDCB_SCL   | Serial Clock Port for DDC Bus of Port B. DDCB_SCL is 5 V tolerant.     |

| D9      | DDCB_SDA   | Serial Data Port for DDC Bus of Port B. DDCB_SDA is 5 V tolerant.      |

| D10     | DDCC_SCL   | Serial Clock Port for DDC Bus of Port C. DDCC_SCL is 5 V tolerant.     |

| D11     | DDCC_SDA   | Serial Data Port for DDC Bus of Port C. DDCC_SDA is 5 V tolerant.      |

| D12     | DDCD_SCL   | Serial Clock Port for DDC Bus of Port D. DDCD_SCL is 5 V tolerant.     |

| D13     | DDCD_SDA   | Serial Data Port for DDC Bus of Port D. DDCD_SDA is 5 V tolerant.      |

| D14     | VREG       | Voltage Regulator Output. Must be decoupled to GND via 1 µF capacitor. |

| D15     | GND        | Ground.                                                                |

| D16     | VGA_SCL    | Serial Clock for VGA Interface. VGA_SCL is 5 V tolerant.               |

| D17     | VGA_SDA    | Serial Data for VGA Interface. VGA_SDA is 5 V tolerant.                |

| D18     | TVDD       | HDMI Termination Supply (3.3 V).                                       |

| D19     | AC_AVDD    | Audio Block Supply (3.3 V).                                            |

| D20     | AC_AVDD    | Audio Block Supply (3.3 V).                                            |

| D21     | AC_AVDD    | Audio Block Supply (3.3 V).                                            |

| D22     | ACMUXIN_2R | Audio Codec Mux Input 2 Right Channel.                                 |

| D23     | ACMUXIN_2L | Audio Codec Mux Input 2 Left Channel.                                  |

| E1      | RXA_1+     | Digital Input Channel 1 True of Port A in the HDMI Interface.          |

| E2      | RXA_1-     | Digital Input Channel 1 Complement of Port A in the HDMI Interface.    |

| E3      | CVDD       | HDMI Comparator Supply (1.8 V).                                        |

| E4      | RXC_5V     | 5 V Detect Pin for Port C in the HDMI Interface.                       |

| E20     | GND        | Ground.                                                                |

| E21     | GND        | Ground.                                                                |

| E22     | ACMUXIN_3R | Audio Codec Mux Input 3 Right Channel.                                 |

| E23     | ACMUXIN_3L | Audio Codec Mux Input 3 Left Channel.                                  |

| F1      | RXA_2+     | Digital Input Channel 2 True of Port A in the HDMI Interface.          |

| F2      | RXA_2–     | Digital Input Channel 2 Complement of Port A in the HDMI Interface.    |

| F3      | CVDD       | HDMI Comparator Supply (1.8 V).                                        |

| F4      | RXB_5V     | 5 V Detect Pin for Port B in the HDMI Interface.                       |

| F20     | PLL_LF     | Loop Filter Ball for Audio Codec PLL.                                  |

# Data Sheet

\_

| Pin No. | Mnemonic    | Description                                                       |

|---------|-------------|-------------------------------------------------------------------|

| F21     | GND         | Ground.                                                           |

| F22     | ACMUXIN_4R  | Audio Codec Mux Input 4 Right Channel.                            |

| F23     | ACMUXIN_4L  | Audio Codec Mux Input 4 Left Channel.                             |

| G1      | TVDD        | HDMI Termination Supply (3.3 V).                                  |

| G2      | TVDD        | HDMI Termination Supply (3.3 V).                                  |

| G3      | TVDD        | HDMI Termination Supply (3.3 V).                                  |

| G4      | TVDD        | HDMI Termination Supply (3.3 V).                                  |

| G7      | GND         | Ground.                                                           |

| G8      | TEST1       | Test Pin. Do not connect.                                         |

| G9      | CVDD        | HDMI Comparator Supply (1.8 V).                                   |

| G10     | CVDD        | HDMI Comparator Supply (1.8 V).                                   |

| G11     | CVDD        | HDMI Comparator Supply (1.8 V).                                   |

| G12     | CVDD        | HDMI Comparator Supply (1.8 V).                                   |

| G13     | CVDD        | HDMI Comparator Supply (1.8 V).                                   |

| G14     | CVDD        | HDMI Comparator Supply (1.8 V).                                   |

| G15     | CVDD        | HDMI Comparator Supply (1.8 V).                                   |

| G16     | GND         | Ground.                                                           |

| G17     | GND         | Ground.                                                           |

| G20     | AC_AVDD     | Audio Block Supply (3.3 V).                                       |

| G21     | GND         | Ground.                                                           |

| G22     | ACMUXIN_5R  | Audio Codec Mux Input 5 Right Channel.                            |

| G23     | ACMUXIN_5L  | Audio Codec Mux Input 5 Left Channel.                             |

| H1      | EP_MISO     | External EDID EEPROM Interface.                                   |

| H2      | EP_MOSI     | External EDID EEPROM Interface.                                   |

| H3      | SPDIF_IN    | S/PDIF Digital Audio Input for Audio Return Channel (ARC).        |

| H4      | RXA_5V      | 5 V Detect Pin for Port A in the HDMI Interface.                  |

| H7      | GND         | Ground.                                                           |

| H8      | GND         | Ground.                                                           |

| H9      | GND         | Ground.                                                           |

| H10     | GND         | Ground.                                                           |

| H11     | GND         | Ground.                                                           |

| H12     | GND         | Ground.                                                           |

| H13     | GND         | Ground.                                                           |

| H14     | GND         | Ground.                                                           |

| H15     | GND         | Ground.                                                           |

| H16     | GND         | Ground.                                                           |

| H17     | GND         | Ground.                                                           |

| H20     | GND         | Ground.                                                           |

| H21     | GND         | Ground.                                                           |

| H22     | FILTA       | Audio Codec ADC Filter Capacitor.                                 |

| H23     | VREF_AUDIO  | Audio Codec Block Reference Voltage Capacitor.                    |

| J1      | EP_CS       | External EDID EEPROM Interface.                                   |

| J2      | EP_SCK      | External EDID EEPROM Interface.                                   |

| J3      | SHARED_EDID | EDID Selection Signal for HDMI Port D.                            |

| J4      | RESET       | Chip Reset. Active low. Minimum low time guarantee reset is 5 ms. |

| J7      | GND         | Ground.                                                           |

| J8      | GND         | Ground.                                                           |

| J9      | GND         | Ground.                                                           |

| J10     | GND         | Ground.                                                           |

| J11     | GND         | Ground.                                                           |

| J12     | GND         | Ground.                                                           |

| J13     | GND         | Ground.                                                           |

| J14     | GND         | Ground.                                                           |

| Pin No.MnemonicDescriptionJ15GNDGround.J16GNDGround.                                                                |                                 |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                                                                                                     |                                 |

| J16 GND Ground.                                                                                                     |                                 |

| J17 GND Ground.                                                                                                     |                                 |

| J20 AC_AVDD Audio Block Supply (3.3 V).                                                                             |                                 |

| J21 GND Ground.                                                                                                     |                                 |

| J22 ISET Audio Codec ADC Current Settings.                                                                          |                                 |

| J23 FILTD Audio Codec DAC Filter Capacitor.                                                                         |                                 |

| K1 GND Ground.                                                                                                      |                                 |

| K2 GND Ground.                                                                                                      |                                 |

| K3 DVDDIO I/O Supply (3.3 V).                                                                                       |                                 |

| K4 DVDDIO I/O Supply (3.3 V).                                                                                       |                                 |

| K7 VDD Video Digital Supply (1.8 V).                                                                                |                                 |