# **Sequential Linear LED Driver**

#### **Features**

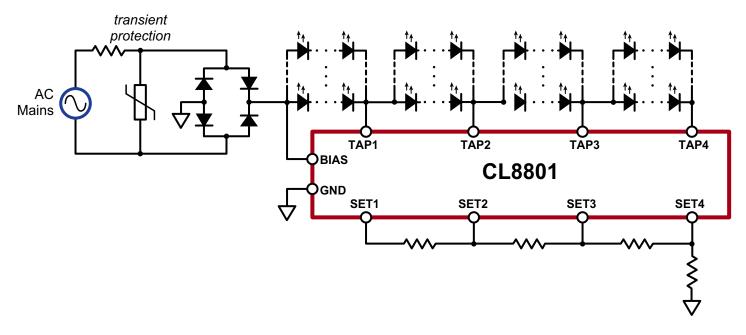

- Minimal component count (base config: CL8801 + 4 resistors + diode bridge)

- No magnetics, no capacitors

- Up to 7.5W output (13W w/ heat sink)

- >110Lm/W using efficient LEDs

- ► 85% electrical efficiency

- >0.95 power factor

- <30% THD line current</p>

- Low conducted EMI w/o filters

- ▶ 85% LED luminous utilization

- Phase dimmer compatible with an RC network

## Applications

- Fluorescent tube retrofit

- Incandescent & CFL bulb replacement

- General LED lighting

### **General Description**

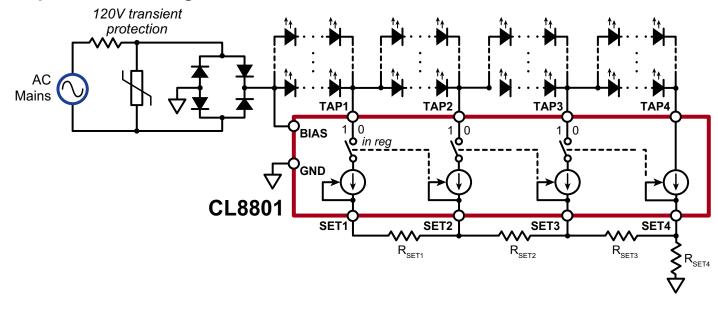

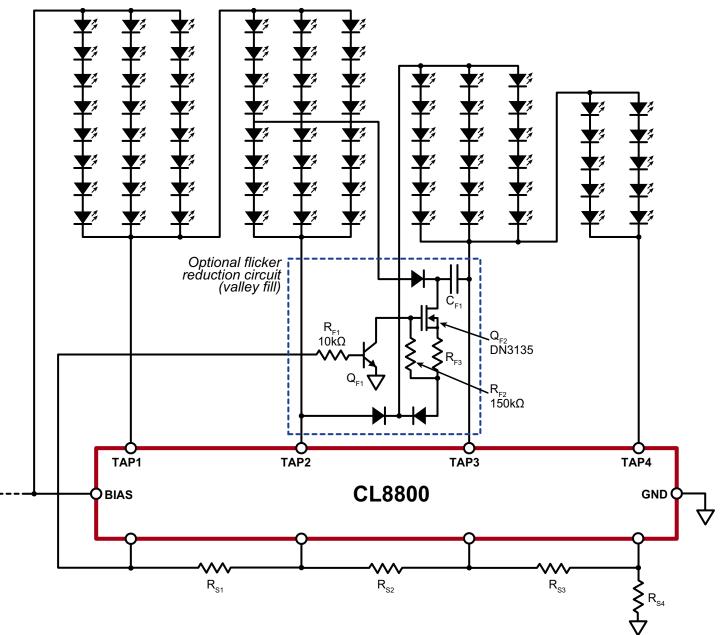

The CL8801 is designed to drive a long string of inexpensive, low current LEDs directly from the AC mains. A basic driver circuit consists of the CL8801, four resistors, and a bridge rectifier. Two to four additional components are optional for various levels of transient protection. No capacitors, EMI filters, or power factor correction circuits are needed.

A string of series/parallel LEDs is tapped at four locations. Four linear current regulators sink current at each tap and are sequentially turned on and off, tracking the input sine wave voltage. Voltage across each regulator is minimized when conducting, providing high efficiency. Output current at each tap is individually resistor-adjustable. Crossregulation, as the CL8801 switches from one regulator to the next, provides smooth transitions. The current waveform can be tailored to optimize for input voltage range, line/load regulation, output power/current, efficiency, power factor, THD, dimmer compatibility, and LED utilization.

With the addition of an RC network, the driver is compatible with phase dimming.

GND

S

## **Ordering Information**

| Part Number      | Package Options   | Packing   |  |  |

|------------------|-------------------|-----------|--|--|

| CL8801K63-G      | 33-Lead (6x6) QFN | 490/Tray  |  |  |

| CL8801K63-G M935 | 33-Lead (6x6) QFN | 2000/Reel |  |  |

-G denotes a lead (Pb)-free / RoHS compliant package

ESD Sensitive Device

# **Absolute Maximum Ratings**

| Parameter                             | Value           |

|---------------------------------------|-----------------|

| V <sub>BIAS</sub> , V <sub>TAP1</sub> | –0.5V to +550V  |

| V <sub>TAP2-4</sub>                   | –0.5V to +320V  |

| V <sub>SET1-4</sub>                   | 4.0V            |

| Operating junction temperature        | -55°C to +125°C |

| Storage temperature, T <sub>s</sub>   | -65°C to +150°C |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

# **Typical Thermal Resistance**

| Package     | $\theta_{ja}^{1}$ | $\theta_{jc}^{2}$ |  |  |  |

|-------------|-------------------|-------------------|--|--|--|

| 33-Lead QFN | 24°C/W            | 2.5°C/W           |  |  |  |

Notes:

1. 1.0oz Cu 4-layer board, 3x4" PCB with thermal pad and thermal via array.

2. Junction to exposed heat slug.

# **Recommended Operating Conditions**

| Sym               | Parameter            |        | Parameter |   | Min | Тур | Мах            | Units | Conditions |

|-------------------|----------------------|--------|-----------|---|-----|-----|----------------|-------|------------|

|                   |                      | TAP1   | -         | - | 60  |     |                |       |            |

| I <sub>out</sub>  | Output current       | TAP2   | -         | - | 90  |     |                |       |            |

|                   |                      | TAP3   | -         | - | 200 | mA  |                |       |            |

|                   |                      | TAP4   | -         | - | 200 |     |                |       |            |

|                   |                      | TAP1   | -         | - | 400 |     | Non-conducting |       |            |

| V <sub>OUT</sub>  | Output voltage       | TAP2-4 | -         | - | 300 | V   | Non-conducting |       |            |

|                   |                      | TAP1-4 | -         | - | (1) |     | Conducting     |       |            |

| V <sub>BIAS</sub> | Applied BIAS voltage |        | -         | - | 440 | V   |                |       |            |

Note:

(1) Voltage capability is determined by power dissipation (V  $\times$  I).

Downloaded from: http://www.datasheetcatalog.com/

www.supertex.com

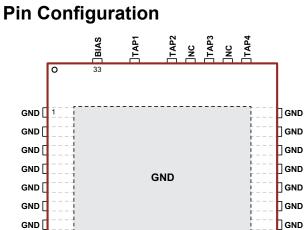

## **Product Marking**

SET1[ NC[

GND [

g

33-Lead QFN (top view)

NC NC SET4

NC SET3

33-Lead QFN

## Electrical Characteristics (over recommended operating conditions at 25°C unless specified otherwise)

| Sym                   | Parameter                      | Min      | Тур  | Max  | Units | Conditions                         |                                                    |  |

|-----------------------|--------------------------------|----------|------|------|-------|------------------------------------|----------------------------------------------------|--|

| I <sub>BIAS</sub>     | BIAS pin input current         | -        | 250  | 410  | μA    | V <sub>BIAS</sub> = 170V           |                                                    |  |

|                       |                                | TAP1     | 60   | -    | -     | mA                                 | V <sub>TAP1</sub> = 30V, V <sub>SET1~4</sub> = GND |  |

|                       | Output current, on             | TAP2     | 90   | -    | -     |                                    | V <sub>TAP2</sub> = 17V, V <sub>SET1~4</sub> = GND |  |

| TAP(ON)               |                                | TAP3     | 200  | -    | -     |                                    | V <sub>TAP3</sub> = 17V, V <sub>SET1~4</sub> = GND |  |

|                       |                                | TAP4     | 200  | -    | -     |                                    | V <sub>TAP4</sub> = 17V, V <sub>SET1~4</sub> = GND |  |

| I <sub>TAP(OFF)</sub> | Output current, off            | -        | 0    | 10   | μA    | TAP1 - 3, V <sub>BIAS</sub> = 170V |                                                    |  |

|                       | Degulation voltage at CET nine | SET1 - 3 | 1.80 | 2.00 | 2.20  | V                                  |                                                    |  |

| $V_{REG}$             | Regulation voltage at SET pins | 1.89     | 2.10 | 2.31 | V     |                                    |                                                    |  |

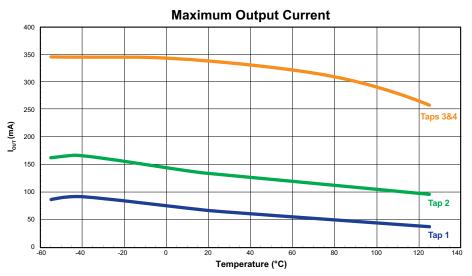

## **Output Current Thermal Characteristics**

## Simplified Block Diagram

#### Overview

Designing a driver to meet particular requirements may be a difficult task considering the number of design variables (16): tap current (4), number of series-connected LEDs per segment (4), and the number of parallel-connected LEDs per segment (4). Manually selecting values will provide light, but the chosen values may be far from optimal in regards to efficiency, LED utilization, line regulation, etc.

Contact your nearest Supertex Field Applications Engineer for design assistance. MathCAD and Excel worksheets are available by contacting <u>apps@supertex.com</u>.

In addition to configuring the driver, several circuits may be employed to increase reliability, performance, and cost. The following sections briefly describe these circuits.

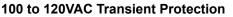

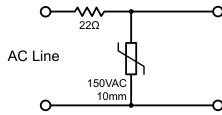

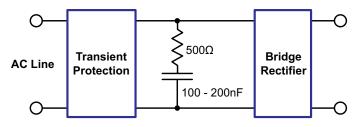

#### **Transient Protection**

Since the driver circuits have no need for capacitors that could otherwise absorb transient energy, nor is there a need for EMI filters that would block transients, the full burden of transient protection is borne by the protection circuit. The two-stage approach in the following schematics provide 2.5kV protection, both pulse and ring per EN 61000-4-5 and EN 61000-4-12, six hits each.

#### **230VAC Transient Protection**

#### Zener Substitution

Zeners may be substituted for LEDs in the bottom stages. The last 1 or 2 stages contribute little to light output - they are mainly to off-load the adjacent upstream regulator at high line voltages to minimize losses. Zener substitution advantages include minimizing unlit LEDs at low line for better light uniformity, better line regulation at high line, fewer LEDs for lower cost and less PCB area, and fewer board-to-board connections. Disadvantages include slightly reduced efficiency at high line, and additional heat load on the driver board.

#### **Phase Dimming**

As with any light load, the LED lamp might not draw enough current to assure proper dimmer operation. This is especially true for 230VAC dimmers. Triacs used in dimmers require a minimum latching current when triggered to place the triac in the latched-on state. Once latched, a minimum holding current is required to maintain the triac in the on state. Latching current is many times greater than the holding current, and is the main concern with dimmer compatibility.

Higher latching current can be provided by a simple series RC network across the AC line. A short time constant provides a current spike at the turn-on edge.

Less common is inadequate holding current. The minimum dimmer holding current is typically 10-20mA. Tap1 at 60mA (max) exceeds the minimum.

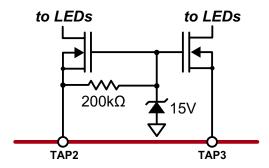

#### Flicker

Twice per AC line cycle the line voltage crosses zero volts, during which time there is no light output.

The circuit below can provide 5-10% valley fill. It has little effect on input current waveshape (THD, PF) and efficiency.

#### **Power Boost**

Higher output power can be achieved by off-loading a portion of the power dissipation from the CL8801 to external FETs. The circuit below drops most of the tap voltage across the FETs, thereby shifting the bulk of the dissipation to the FET.

Valley Fill Circuit

## **Pin Description**

| Pin #   | Pin<br>Name     | Description                                                                                                                                                    |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 - 8   | GND             | Circuit common (use for heat sink ground plane pass through).                                                                                                  |

| 9       | SET1            | Current sense for linear current regulators for each tap. Resistors on these pins sets the tap currents.                                                       |

| 10      | NC              | No internal connection.                                                                                                                                        |

| 11      | SET2            | Current sense for linear current regulators for each tap. Resistors on these pins sets the tap currents.                                                       |

| 12      | NC              | No internal connection.                                                                                                                                        |

| 13      | SET3            | Current sense for linear current regulators for each tap. Resistors on these pins sets the tap currents.                                                       |

| 14      | NC              | No internal connection.                                                                                                                                        |

| 15      | NC              | No internal connection.                                                                                                                                        |

| 16      | NC              | No internal connection.                                                                                                                                        |

| 17      | SET4            | Current sense for linear current regulators for each tap. Resistors on these pins sets the tap currents.                                                       |

| 18      | NC              | No internal connection.                                                                                                                                        |

| 19 - 20 | GND             | Circuit common (use for heat sink ground plane pass through).                                                                                                  |

| 21      | GND             | Circuit common. Connect to bridge rectifier return (use for heat sink ground plane pass through).                                                              |

| 22 - 26 | GND             | Circuit common (use for heat sink ground plane pass through).                                                                                                  |

| 27      | TAP4            | Current regulator outputs. Connect to taps along the LED string.                                                                                               |

| 28      | NC              | No internal connection.                                                                                                                                        |

| 29      | TAP3            | Current regulator outputs. Connect to taps along the LED string.                                                                                               |

| 30      | NC              | No internal connection.                                                                                                                                        |

| 31      | TAP2            | Current regulator outputs. Connect to taps along the LED string.                                                                                               |

| 32      | TAP1            | Current regulator outputs. Connect to taps along the LED string.                                                                                               |

| 33      | BIAS            | Provides bias for driver. Connect to rectified AC.                                                                                                             |

|         | de plate<br>ND) | For heatsinking purposes, it should be soldered to a 4.0cm <sup>2</sup> exposed copper area. It should also be electrically connected to circuit common (GND). |

Note:

The high voltage pins are located on one side of the package and are arranged from lowest voltage to highest. Pin-to-pin voltage gradients are minimized.

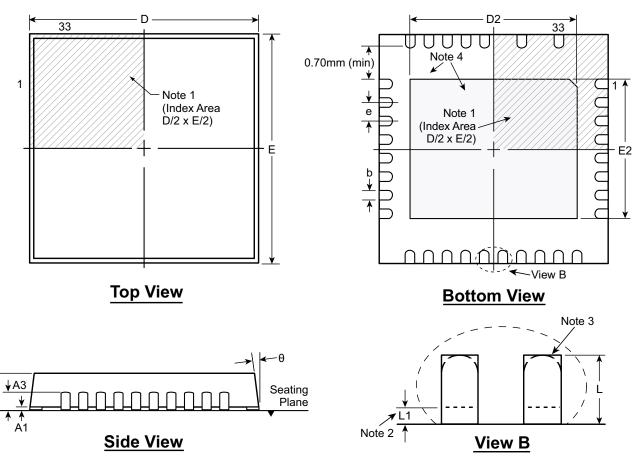

# 33-Lead QFN Package Outline (K6)

6.00x6.00mm body, 1.00mm height (max), 0.50mm pitch

Notes:

- 1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Depending on the method of manufacturing, a maximum of 0.15mm pullback (L1) may be present.

- 3. The inner tip of the lead may be either rounded or square.

- 4. There will be an exposed DAP. A minimum of 0.7mm spacing will be maintained between the leads and the DAP.

| Symb              | ol  | Α    | A1   | A3          | b    | D    | D2   | E    | E2   | е           | L    | L1   | θο |

|-------------------|-----|------|------|-------------|------|------|------|------|------|-------------|------|------|----|

| Dimension<br>(mm) | MIN | 0.80 | 0.00 | 0.20<br>REF | 0.18 | 5.85 | 4.00 | 5.85 | 3.60 | 0.50<br>BSC | 0.30 | 0.00 | 0  |

|                   | NOM | 0.90 | 0.02 |             | 0.25 | 6.00 | 4.15 | 6.00 | 3.75 |             | 0.40 | -    | -  |

|                   | MAX | 1.00 | 0.05 |             | 0.30 | 6.15 | 4.25 | 6.15 | 3.85 |             | 0.50 | 0.15 | 14 |

Drawings not to scale.

Supertex Doc. #: DSPD-33QFNK636X6P050, Version A021312.

(The package drawings in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2014 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.

Downloaded from: http://www.datasheetcatalog.com/