# Radiation Hardened, 2-Terminal Temperature Transducer

### ISL71590SEH

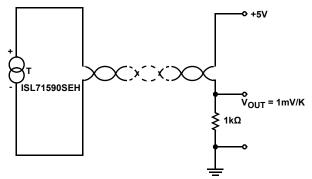

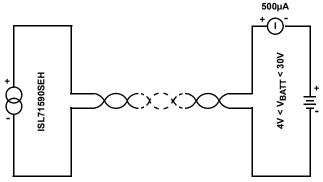

The <u>ISL71590SEH</u> is a temperature-to-current transducer possessing two terminals. It has a high impedance current output that allows it to be insensitive to voltage drops across long lines. When provided a differential voltage between 4V and 33V, the device acts as a constant current regulator that generates a current equal to 1µA/Kelvin (K).

The ISL71590SEH is specified across the -55°C to +125°C temperature range and with  $\pm 1.7$ °C accuracy without the need of additional circuitry, and also capable of operating up to +150°C. With power requirements as low as 1.5mW (5V at +25°C), it is an ideal choice for remote sensing applications as any well-insulated twisted pair cable will allow for proper operation. It can be used in several additional applications including temperature compensation networks, flow rate analysis, anemometry and biasing proportional to absolute temperature.

The high output impedance (> $10M\Omega$ ) leaves plenty of room for variations in the power supply voltage. It is electrically durable as it can withstand a forward operating voltage of 33V over the full temperature range both under and without ion beam radiation and a reverse voltage of -40V.

The ISL71590SEH is available in a 2 Ld flatpack and die forms.

## **Applications**

- · RF power amplifier bias compensation

- · LCD bias compensation

- · Laser diode bias compensation

- · Sensor bias and linearization

- · Data acquisition systems

### **Features**

- High output impedance provides excellent rejection to variations in the supply line

- · Additional linearization circuitry is not needed for operation

- Operating temperature range.....-55°C to +150°C

- · QML qualified per MIL-PRF-38535 requirements

- Radiation environment

- SEL/SEB LET<sub>TH</sub> ...... 86.4 MeV cm<sup>2</sup>/mg

Total dose, high dose rate. ..... 300krad(Si)

- Total dose, low dose rate ...... 50krad(Si)\*

- \* Product capability established by initial characterization. The EH version is acceptance tested on a wafer-by-wafer basis to 50krad(Si) at low dose rate.

- Electrically screened to SMD#\_5962-13215

### **Related Literature**

- AN1844, "ISL71590SEHXX Evaluation Board User's Guide"

- AN1895, "Total Dose Testing of the ISL71590SEH Radiation Hardened Temperature Sensor"

- AN1894, "Single Event Effects (SEE) Testing of the ISL71590SEH Temperature Sensor"

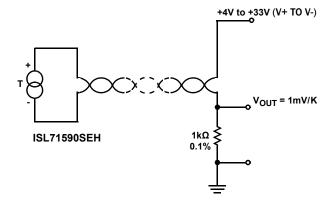

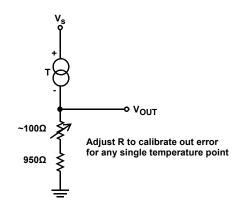

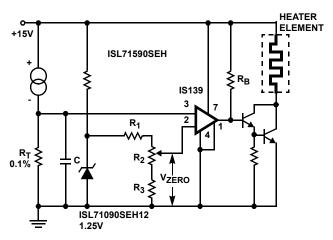

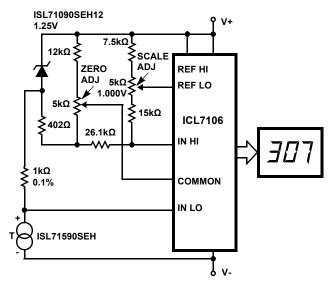

FIGURE 1. TYPICAL APPLICATION

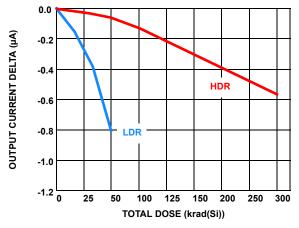

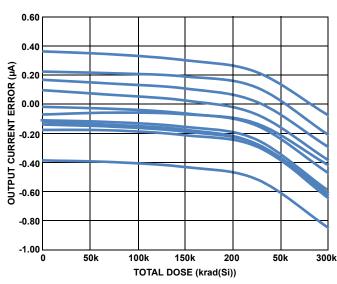

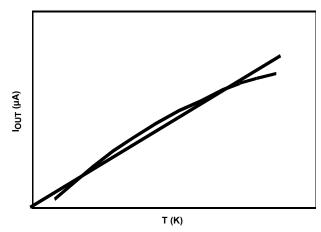

FIGURE 2. IOUT SHIFT vs LOW/HIGH DOSE RATE RADIATION

## **Ordering Information**

| ORDERING / SMD NUMBER (Note 2) | PART NUMBER<br>(Note 1) | TEMPERATURE RANGE (°C) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |

|--------------------------------|-------------------------|------------------------|-----------------------------|----------------|

| 5962F1321501VXC                | ISL71590SEHVF           | -55 to +125            | 2 Ld Flatpack               | K2.A           |

| 5962F1321501V9A                | ISL71590SEHVX           | -55 to +125            | Die                         |                |

| N/A                            | ISL71590SEHF/PROTO      | -55 to +125            | 2 Ld Flatpack               | K2.A           |

| N/A                            | ISL71590SEHX/SAMPLE     | -55 to +125            | Die                         |                |

| N/A                            | ISL71590SEHMF           | -55 to +125            | 2 Ld Flatpack               | K2.A           |

|                                | ISL71590SEHEV1Z         | Evaluation Board       | .1                          | ,              |

#### NOTES:

- 1. These Intersil Pb-free Hermetic packaged products employ 100% Au plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

- 2. Specifications for Rad Hard QML devices are controlled by the Defense Logistics Agency Land and Maritime (DLA). The SMD numbers listed must be used when ordering.

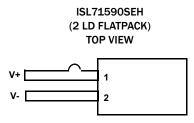

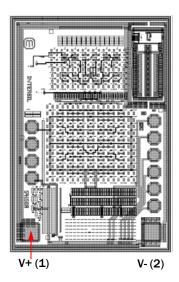

## **Pin Configuration**

## **Pin Descriptions**

| ISL71590SEH<br>(2 Ld FLATPACK) | PIN NAME | EQUIVALENT ESD CIRCUIT | DESCRIPTION                           |

|--------------------------------|----------|------------------------|---------------------------------------|

| 1                              | V+       | Circuit 1              | Positive Voltage lead Range 4V to 33V |

| 2                              | V-       | Circuit 1              | Negative Voltage lead                 |

|                                |          | V+ ESD CIRCUIT V-      | T O                                   |

Submit Document Feedback 2 intersil June 3, 2016

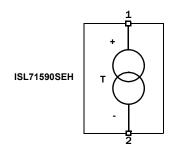

## **Functional Block Diagram**

FIGURE 3. BLOCK DIAGRAM

# **Typical Applications**

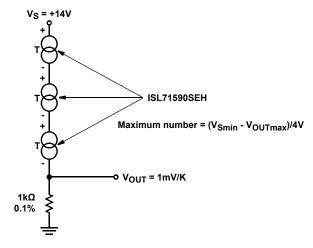

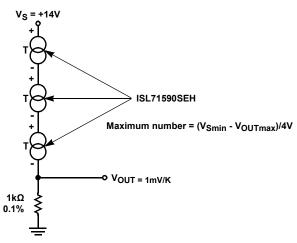

FIGURE 4. LOWEST TEMPERATURE SENSING SCHEME. OUTPUT CURRENT IS THAT OF THE "COLDEST" SENSOR

e.g., with 4 sensors and R = 250 $\Omega$  V<sub>OUT</sub> = 1mV/K)

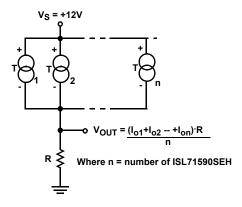

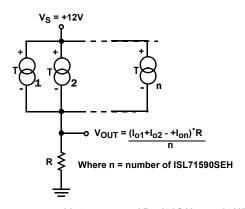

FIGURE 5. AVERAGE TEMPERATURE SENSING SCHEME. OUTPUT CURRENT IS THE SUM OF ALL SENSOR CURRENTS

### **Absolute Maximum Ratings**

| Maximum Supply Voltage                             | 40V    |

|----------------------------------------------------|--------|

| In-Beam Maximum Supply Voltage (Note 5)            | 37V    |

| Maximum Reverse Voltage                            | 40V    |

| Maximum Differential Input Voltage                 | ±40V   |

| Case to Lead Breakdown Voltage                     | .±200V |

| ESD Rating                                         |        |

| Human Body Model (Tested per MIL-STD-883 TM3015.7) | 3kV    |

| Machine Model (Tested per EIA/JESD22-A115-A)       | 300V   |

| Charged Device Model (Tested per JESD22-C101D)     | 750V   |

|                                                    |        |

### **Thermal Information**

| Thermal Resistance (Typical)              | $\theta_{JA}(^{\circ}C/W)$ | $\theta_{JC}$ (°C/W) |

|-------------------------------------------|----------------------------|----------------------|

| 2 Ld Flatpack (Notes 3, 4)                | 80                         | 8                    |

| Storage Temperature Range                 | 6!                         | 5°C to +155°C        |

| Maximum Junction Temperature $(T_{JMAX})$ |                            | +150°C               |

### **Recommended Operating Conditions**

| Ambient Operating Temperature Range                     | 55°C to +125°C |

|---------------------------------------------------------|----------------|

| Maximum Operating Junction Temperature                  | +150°C         |

| Supply Voltage (V+ to V-) ( <u>Notes 5</u> , <u>6</u> ) | 4V to 33V      |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 3.  $\theta_{JA}$  is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 4. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the ceramic on the package underside.

- 5. The maximum supply voltage specified is for operation in a heavy ion environment at an LET =  $86.4 \, \text{MeV} \cdot \text{cm}^2/\text{mg}$ .

- 6. The maximum voltage beyond which output current performance is not to be considered valid (Figure 9).

### Electrical Specifications $V_s = 5V$ , $T_A = +25$ °C, unless otherwise noted. Boldface limits apply across the operating temperature range, -55°C to +125°C.

| SYMBOL PARAMETER                           |                                                                              | TEST CONDITIONS                                | MIN<br>(Note 7) | TYP              | MAX<br>(Note 7) | UNIT          |

|--------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------|-----------------|------------------|-----------------|---------------|

| V <sub>S</sub>                             | Power Supply Voltage Range                                                   | (V+ to V-) ( <u>Note 5</u> )                   | 4               |                  | 31              | V             |

| I <sub>0</sub>                             | Nominal Current Output                                                       |                                                |                 | 298.1            |                 | μΑ            |

| E                                          | Ambient Error Accuracy                                                       |                                                | -0.50           | -0.05            | 0.50            | °C            |

| TCIO                                       | Current Output Temperature Coefficient                                       |                                                |                 | 1                |                 | μ <b>A</b> /K |

| E <sub>A</sub>                             | Absolute Error without External Calibration                                  | Over full temperature range                    | -2.0            |                  | 2.0             | °C            |

| NL                                         | Nonlinearity                                                                 | At 5 discrete temperature points               | -0.5            |                  | 0.5             | °C            |

| RPT                                        | Repeatability                                                                | After temperature range end point cycling      | -0.1            |                  | 0.1             | °C            |

| dE/dt                                      | Long Term Drift                                                              | V+ = 31V for 1khr at +125°C                    | -0.25           | -0.05            | 0.25            | °C            |

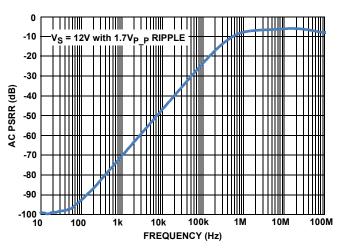

| PSRR                                       | Output Current V <sub>S</sub> Rejection                                      | 5V > V <sub>S</sub> >4V                        |                 | 0.05             | 0.50            | μ <b>A</b> /V |

|                                            |                                                                              | 5V ≤ V <sub>S</sub> ≤ 15V                      |                 | 0.03             | 0.20            | μ <b>A</b> /V |

|                                            |                                                                              | 5V ≤ V <sub>S</sub> ≤ 31V                      |                 | 0.04             | 0.10            | μ <b>A</b> /V |

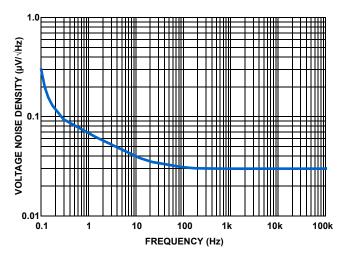

| V <sub>nd</sub>                            | Voltage Noise Density                                                        | f = 100Hz                                      |                 | 0.03             |                 | μV/√Hz        |

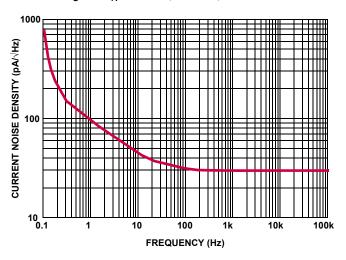

| I <sub>nd</sub>                            | Current Noise Density                                                        | f = 100Hz                                      |                 | 30               |                 | pA/√Hz        |

| Iso                                        | Case Isolation to Either Lead                                                | Case to lead voltage = 200V                    |                 | 10 <sup>10</sup> |                 | Ω             |

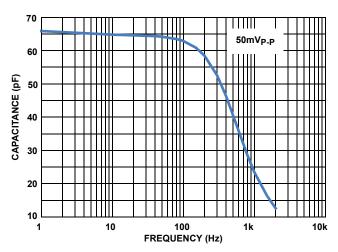

| C <sub>S</sub>                             | Effective Shunt Capacitance                                                  | f = 10Hz                                       |                 | 65               |                 | pF            |

| t <sub>ON</sub>                            | Electrical Turn-On Time                                                      | V <sub>S</sub> = 4V to I <sub>OUT</sub> stable |                 | 2                |                 | μs            |

| I <sub>LEAK</sub>                          | -10V Reverse Bias Leakage Current                                            | +125°C = Worst case                            |                 | 50               |                 | nA            |

| POST RADIATION                             | l                                                                            | ,                                              |                 |                  |                 |               |

| E- <sub>RADD</sub><br>( <u>Figure 19</u> ) | Post Low Dose Rate Radiation (LDR)<br>Ambient Error 50krad at 0.01 rad(Si)/s | Ambient error accuracy plus TID shift (Note 8) | -2.0            |                  | 0.5             | °C            |

|                                            | Post High Dose Rate Radiation (HDR)<br>Ambient Error 300krad at 70 rad(Si)/s | Ambient error accuracy plus TID shift (Note 8) | -2.0            |                  | 0.5             | °C            |

### NOTES:

- 7. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 8. The post radiation Ambient Error specs are defined as the absolute temperature error.

Submit Document Feedback intersil June 3, 2016

**TABLE 1. BURN-IN AND LIFE TEST DELTA PARAMETERS**

| PARAMETER             | SYMBOL | BURN-IN<br>END POINT | BURN-IN<br>DELTA | MIL-STD GROUP C<br>END POINT | MIL-STD GROUP C<br>DELTA | UNITS |

|-----------------------|--------|----------------------|------------------|------------------------------|--------------------------|-------|

| Ambient Error (+25°C) | E      | ±0.5                 | ±0.25            | ±0.5                         | ±0.25                    | °C    |

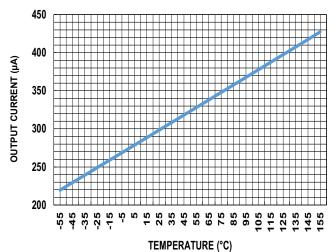

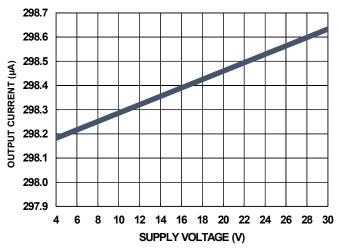

# **Typical Performance Curves** Unless otherwise specified, $V_S$ = 5V, $T_A$ = +25°C.

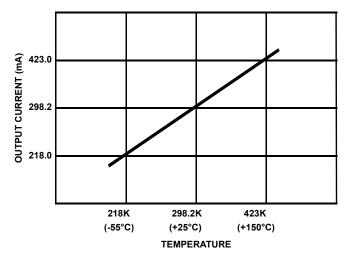

FIGURE 6. OUTPUT CURRENT vs TEMPERATURE

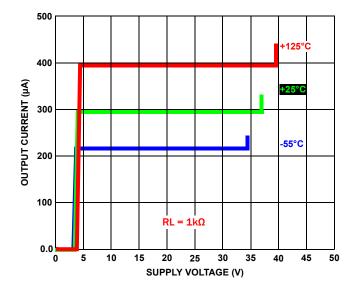

FIGURE 7. OUTPUT CURRENT vs V<sub>S</sub> VOLTAGE

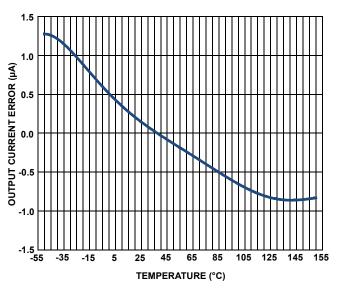

FIGURE 8. TYPICAL ABSOLUTE ERROR WITHOUT EXTERNAL CALIBRATION vs TEMPERATURE

FIGURE 9. VI CURVE OF  $V_S$  vs  $I_{OUT}$  OVER-TEMPERATURE

Submit Document Feedback 5 Intersil June 3, 2016

# Typical Performance Curves Unless otherwise specified, $V_S = 5V$ , $T_A = +25$ °C. (Continued)

FIGURE 10. VOLTAGE NOISE DENSITY vs FREQUENCY

FIGURE 12. AC PSRR vs FREQUENCY

FIGURE 14. SINGLE TEMPERATURE ERROR CALIBRATION

FIGURE 11. CURRENT NOISE DENSITY vs FREQUENCY

FIGURE 13. SHUNT CAPACITANCE vs FREQUENCY

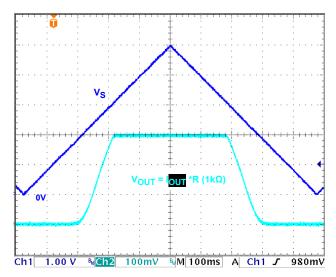

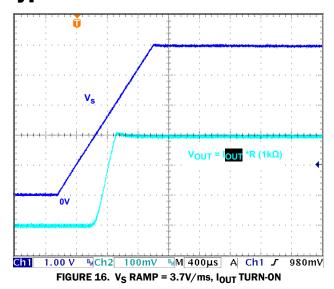

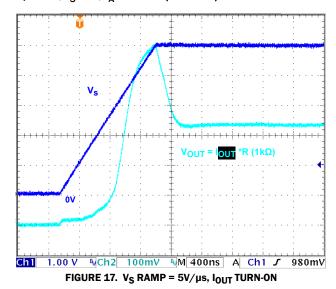

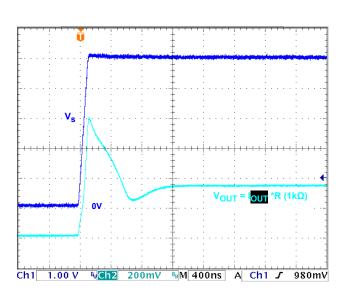

FIGURE 15. TURN-ON/OFF  $V_S$  VOLTAGE

Submit Document Feedback 6 June 3, 2016 intersil

## Typical Performance Curves Unless otherwise specified, V<sub>S</sub> = 5V, T<sub>A</sub> = +25°C. (Continued)

FIGURE 19. TYPICAL ABSOLUTE I<sub>OUT</sub> ERROR vs TOTAL IONIZING DOSE FOR HIGH DOSE RATE

## **Functional Description**

### **Functional Overview**

The ISL71590SEH is an integrated-circuit temperature-to-current transducer, which produces an output current proportional to absolute temperature. The device acts as a high impedance constant current regulator passing  $1\mu\text{A/K}$  for supply voltages (V+ to V-) from +4V to +33V.

The ISL71590SEH is manufactured in Intersil's PR40, silicon-on-insulator process, which makes this device immune to single event latch-up and provides excellent radiation tolerance. This makes it the ideal choice for high reliability applications in harsh radiation prone environments.

The ISL71590SEH is specified over temperatures of -55°C to +125°C without the need for additional circuitry to produce an output within  $\pm 1.7$ °C accuracy. With power requirements as low as 1.5mW (5V at +25°C), it is an ideal choice for remote sensing as any length of a well-insulated twisted pair cable will allow for proper operation. The high output impedance (>10M $\Omega$ ) leaves plenty of room for variations in the power supply voltage. It is electrically durable since it can withstand a forward operating voltage of 33V over the full temperature range with and without ion beam radiation and a reverse voltage of -40V.

The ISL71590SEH should be used in any temperature sensing application from -55 °C to +150 °C in which conventional electrical temperature sensors are currently employed. The ISL71590SEH provides a total temperature sensing solution that is both low in complexity and small in size by eliminating the

support circuitry necessary with other thermal sensors such as thermistors, thermocouples and other discrete based solutions. External linearization circuitry, precision voltage amplifiers, resistance measuring circuitry and cold junction compensation are not needed when applying the ISL71590SEH.

In the simplest application, the ISL71590SEH, a resistor, a power source and any voltmeter can be used to measure temperature. Ideally resistors used should be of a metal film or metal strip type, such resistors having very low thermal coefficient values.

When voltage is initially applied to the ISL71590SEH, the circuit becomes active at slightly less than 4V, (V+ to V-), with  $I_{OUT}$  ramping up typically 2µs after. There will be an initial short period of time for the  $I_{OUT}$  to be correctly proportional to the ambient temperature. Depending on the  $V_S$  ramp rate and amplitude this may take a few µs before a reliable temperature reading is available. See Figures 15 through 18 for scope shot examples.

The output characteristics also makes the ISL71590SEH easy to multiplex; with either or both the input supply voltage or the output current can be switched by a CMOS multiplexer such as the HS-508 or HS-1840 from Intersil.

When the ISL71590SEH die product is used, the die substrate should be tied to the more negative of the 2 terminals for optimum performance.

## **Parameter Glossary**

The ISL71590SEH parametric specifications provide for an understanding of the temperature sensor performance over-temperature and radiation exposure. Following are critical parameter explanations as they relate to usage and interpretation.

**Ambient Error Accuracy** refers to the maximum error at an ambient temperature of  $+25^{\circ}$ C and is expressed as  $\pm 0.5^{\circ}$ C of the **Nominal Current Output** at  $+25^{\circ}$ C (298.15K) of 298.15 $\mu$ A.

The **Absolute Error without External Calibration** describes the temperature accuracy over the entire -55 °C to +125 °C range. The typical performance is shown in Figure 8 on page 5. Both of these two first specification explanations are to be considered as initial error accuracy specifications.

The Post Low Dose Rate Radiation Ambient Error (E<sub>RADD</sub>) is the specified accuracy after 50krad(Si) at 0.01 rad(Si) per second (LDR) and 300krad(Si) at 70 rad(Si) per second (HDR) exposure. This radiation hardness performance is unmatched in the industry for this class of device, this performance is shown in Figure 2 on page 1 as a delta over radiation type and in Figure 19 on page 7 as an absolute measurement.

**Non-Linearity** in referring to the ISL71590SEH, is the maximum allowable deviation of the output current over-temperature for any single part relative to its individual best fit line over 5 discrete temperature (-55°C, -15°C, +25°C, +85°C, +125°C) points. This performance is guaranteed by testing.

Repeatability Errors arise from a strain hysteresis of the package. For the ISL71590SEH this is the maximum deviation between +25°C readings after a single temperature excursion between -55°C and +125°C, and is guaranteed by characterization and is not tested. The magnitude of this error is solely a function of the magnitude of the temperature span and duration over which the device is exposed.

Long Term Drift Errors are related to the average operating temperature and the magnitude of the thermal shocks experienced by the device. Extended use of the ISL71590SEH temperatures at +125°C typically results in long-term drift of -0.05°C after 1khr with a specification of -0.25°C to +0.25°C.

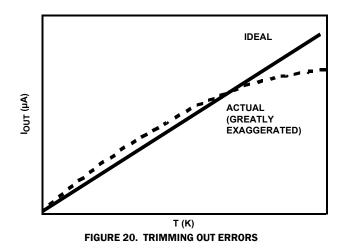

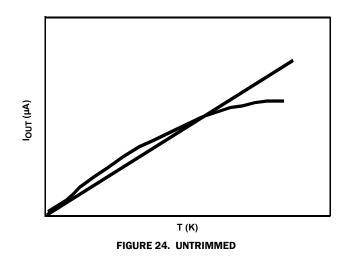

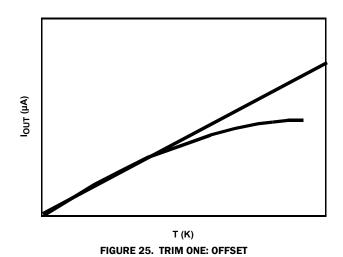

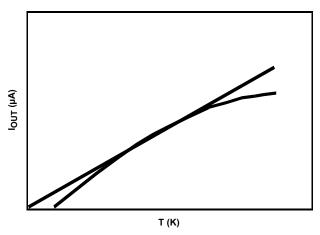

## **Trimming Out Errors**

The ideal graph of current versus temperature for the ISL71590SEH is a straight line, but as Figure 20 on page 9 shows, the actual shape is slightly different (exaggerated greatly for explanation). Since the sensor is limited to the range of -55°C to +150°C it is possible to optimize the accuracy by trimming. Trimming extracts the maximum performance from the sensor.

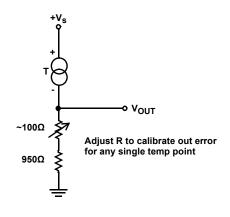

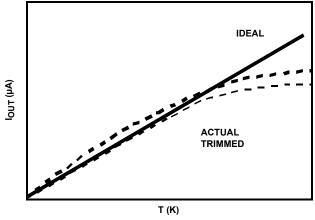

The circuit in Figure 21 on page 9 trims the slope of the ISL71590SEH output. The effect of this is shown in Figure 22 on page 9.

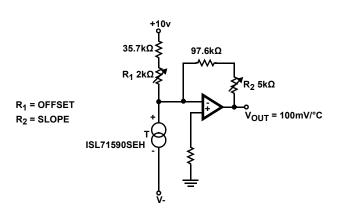

The circuit of Figure 23 on page 9 trims both the slope and the offset

Starting in Figure 24 on page 9 with an untrimmed slope, then progressing through to Figure 27 on page 10 each figure showing the effect of adjusting the offset and slope and finally the offset again to finally arrive at an optimized condition.

The diagrams curvatures are highly are exaggerated to show effects, but it should be clear that these trims can be used to minimize errors over a partial or the entire temperature range.

Submit Document Feedback 8 intersil June 3, 2016

# **Trimming Out Errors**

FIGURE 21. SLOPE TRIMMING

FIGURE 22. EFFECT OF SLOPE TRIM

FIGURE 23. SLOPE AND OFFSET TRIMMING

Submit Document Feedback intersil\* June 3, 2016 FN8376.2

## Trimming Out Errors (Continued)

FIGURE 26. TRIM TWO: SLOPE

## **Typical Applications**

The following section of the datasheet illustrates several application ideas, touching on each with a short explanation. There is an evaluation board ISL71590SEHEV1Z and accompanying user guide <u>"ISL71590SEH Evaluation Board</u> User's Guide" that details 4 of the more fundamental implementations of this device.

FIGURE 28. TYPICAL APPLICATION

FIGURE 29. SIMPLE CONNECTION. OUTPUT IS PROPORTIONAL TO **ABSOLUTE TEMPERATURE**

FIGURE 27. TRIM THREE: OFFSET AGAIN

FIGURE 30. LOWEST TEMPERATURE SENSING SCHEME. OUTPUT **CURRENT IS THAT OF THE "COLDEST" SENSOR**

e.g., with 4 sensors and R = 250 $\Omega$  V<sub>OUT</sub> = 1mV/K)

FIGURE 31. AVERAGE TEMPERATURE SENSING SCHEME

The sum of the ISL71590SEH currents appears across R, which represents the average temperature in the sensor array (see Figure 31).

Submit Document Feedback 10 June 3, 2016 intersil

FIGURE 32. SINGLE SETPOINT TEMPERATURE CONTROLLER

In Figure 32, the ISL71590SEH produces a temperature dependent voltage across R<sub>T</sub> (C is for filtering noise). Setting R<sub>2</sub> produces a scale-zero voltage. For the celsius scale, make  $R_T$  = 1k $\Omega$  and  $V_{ZERO}$  = 0.273V. For Fahrenheit,  $R_T$  = 1.8k $\Omega$  and  $V_{ZERO} = 0.460V.$

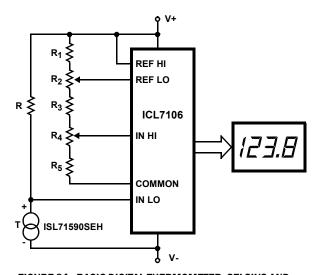

FIGURE 33. SIMPLEST THERMOMETER

Figure 33, illustrates the simplest thermometer displaying current output directly in Kelvin. using the ISL71590SEH, sensor output is within ±1.7K over the entire range.

FIGURE 34. BASIC DIGITAL THERMOMETER, CELSIUS AND **FAHRENHEIT SCALES**

|    | R    | R <sub>1</sub> | R <sub>2</sub> | R <sub>3</sub> | R <sub>4</sub> | R <sub>5</sub> |

|----|------|----------------|----------------|----------------|----------------|----------------|

| °F | 9.00 | 4.02           | 2.0            | 12.4           | 10.0           | 0              |

| °C | 5.00 | 4.02           | 2.0            | 5.11           | 5.0            | 11.8           |

$$\sum_{n=1}^{5} R_n = 28k\Omega \text{ nominal}$$

NOTE: ALL values are in  $k\Omega$ .

In Figure 34, the ICL7106 has a  $\rm V_{\mbox{\footnotesize IN}}$  span of ±2.0V and a  $\rm V_{\mbox{\footnotesize CM}}$ range of (V+ - 0.5V) to (V- + 1V). R is scaled to bring each range within  $V_{CM}$  while not exceeding  $V_{IN}$ . The  $V_{REF}$  for both scales is 500mV, maximum reading on the celsius range is 150°C limited by the maximum allowable sensor temperature. Maximum reading on the fahrenheit range is 199.9°F (93.3°C) limited by the number of display digits.

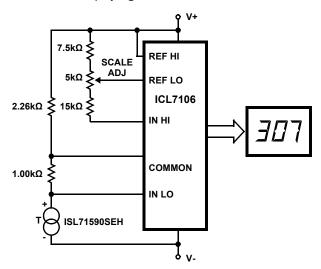

FIGURE 35. BASIC DIGITAL THERMOMETER, KELVIN SCALE

Figure 35, illustrates the Kelvin scale version reading from 0 to 1999K theoretically, and from 223K to 473K actually. The  $2.26k\Omega$  resistor brings the input within the ICL7106  $V_{CM}$  range: 2 general-purpose silicon diodes or an LED may be substituted.

FIGURE 36. BASIC DIGITAL THERMOMETER, KELVIN SCALE WITH ZFRO ADJUST

The circuit in Figure 36 allows "zero adjustment" as well as slope adjustment. The ISL71090SEH12 brings the input within the common-mode range, while the  $5k\Omega$  pots trim any offset at 218K (-55°C) and set the scale factor.

Since all 3 scales have narrow  $V_{IN}$  spans, some optimization of the ICL7106 components can be made to lower noise and preserve CMR. Table 2 shows the suggested values. Similar scaling can be used with the ICL7126 and ICL7136 (see Figures 34 through 36).

TABLE 2.

| SCALE | V <sub>IN</sub> RANGE<br>(V) | RINT<br>(kΩ) | CAZ<br>(µF) |

|-------|------------------------------|--------------|-------------|

| К     | 0.223 to 0.473               | 220          | 0.47        |

| С     | -0.25 to +1.0                | 220          | 0.1         |

| F     | -0.29 to +0.996              | 220          | 0.1         |

FOR ALL:

$C_{\mathsf{REF}} = 0.1 \mu \mathsf{F}$

$C_{INT} = 0.22 \mu F$

C<sub>OSC</sub> =100pF

$R_{OSC} = 100 \text{k}\Omega$

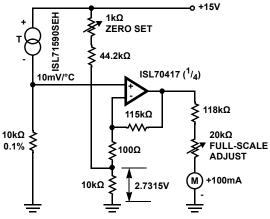

FIGURE 37. CENTIGRADE THERMOMETER (0°C TO +100°C)

Figure 37, illustrates the low bias current of the ISL70417, which allows the use of large value gain resistors, keeping meter current error under 0.5%. Therefore saving the expense of an extra meter driving amplifier.

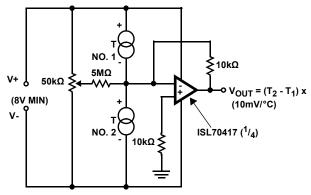

Figure 38 shows a differential temperature sensing circuit configuration. The  $50k\Omega$  pot trims offset in the devices whether internal or external, so it can be used to set the size of the difference interval. This also makes it useful for liquid level detection where there will be a measurable temperature difference.

FIGURE 38. DIFFERENTIAL THERMOMETER

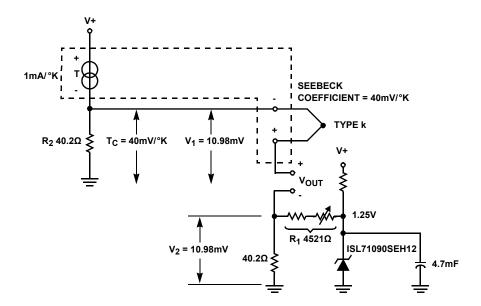

In Figure 39 the reference junction(s) should be in close thermal contact with the ISL71590SEH case. V+ must be at least 4V, while ISL71090SEH12 current should be set 1mA to 2mA. Calibration does not require shorting or removal of the thermocouple: set  $R_1$  for  $V_2=10.98$ mV. If very precise measurements are needed, adjust  $R_2$  to the exact Seebeck coefficient for the thermocouple used (measured or from table) note  $V_1$  and set  $R_1$  to buck out this voltage (i.e., set

For other thermocouple types, adjust values to the appropriate Seebeck coefficient.

Submit Document Feedback 12 intersil June 3, 2016 FN8376.2

$V_2 = V_1$ ).

FIGURE 39. COLD JUNCTION COMPENSATION FOR TYPE K THERMOCOUPLE

Submit Document Feedback 13 June 3, 2016 FN8376.2

## **Package Characteristics**

### **Weight of Packaged Device**

0. 07Grams (Typical)

### **Lid Characteristics**

Finish: Gold Potential: Floating

Case Isolation to Any Lead:  $10 \times 10^9 \Omega$  (minimum)

### **Die Characteristics**

### **Die Dimensions**

1185µm x 1695µm (46.7 mils x 66.7 mils) Thickness: 254µm ±25.4µm (10 mils ±1 mil)

### **Interface Materials**

### **GLASSIVATION**

Type: Nitrox Thickness: 15kÅ

#### **TOP METALLIZATION**

Type: AICu (99.5%/0.5%) Thickness: 30kÅ

### **BACKSIDE FINISH**

Silicon

### **ASSEMBLY RELATED INFORMATION**

#### **SUBSTRATE POTENTIAL**

Tied to V- pin

### **ADDITIONAL INFORMATION**

### **WORST CASE CURRENT DENSITY**

$<5 \times 10^3 \text{A/cm}^2$

#### **PROCESS**

Dielectrically Isolated Bipolar SOI - PR40

#### TRANSISTOR COUNT

92

## **Metallization Mask Layout**

| PAD NAME | PIN NUMBER | Χ<br>(μm) | Υ<br>(μm) | ΔX<br>(μm) | ΔΥ<br>(μm) | BOND WIRES<br>PER PAD |

|----------|------------|-----------|-----------|------------|------------|-----------------------|

| V+       | 1          | 0         | 0         | 110        | 110        | 1                     |

| V-       | 2          | 823       | 0         | 110        | 110        | 1                     |

#### NOTES:

9. Origin of coordinates is the centroid of pad 1.

10. Bond wire size is 1.25 mil.

Submit Document Feedback 14 June 3, 2016 intersil

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Revision.

| DATE               | REVISION | CHANGE                                                                                                                                                                                                                                                                                                            |

|--------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 3, 2016       | FN8376.2 | Clarified minimum differential voltage throughout document. Replaced figures 5 and 6.                                                                                                                                                                                                                             |

| January 19, 2016   | FN8376.1 | Removed Pb-Free Reflow reference from "Thermal Information" on page 4 as it is not applicable to hermetic packages.  In "Electrical Specifications" on page 4: -Updated EA maximum and minimum limitsUpdated ERADD Low Dose minimum limitsUpdated ERADD High Dose minimum limits. Updated About Intersil Section. |

| September 26, 2013 | FN8376.0 | Initial Release                                                                                                                                                                                                                                                                                                   |

### **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at www.intersil.com.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

Submit Document Feedback 15 intersil June 3, 2016

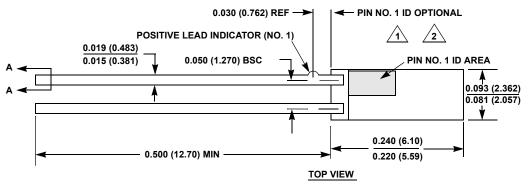

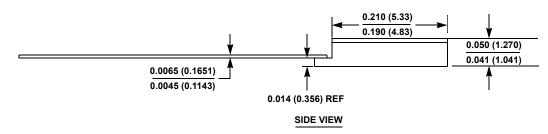

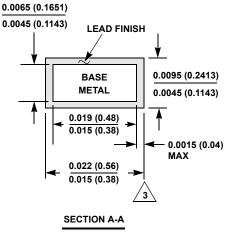

## **Package Outline Drawing**

### **K2.A**

#### **2 LEAD CERAMIC METAL SEAL FLATPACK PACKAGE**

Rev 1, 4/12

#### NOTES:

1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark. Alternately, a tab may be used to identify pin one.

1 If a pin one identification mark is used in addition to a tab, the limits of the tab dimension do not apply.

3. The maximum limits of lead dimensions (section A-A) shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- 4. Dimensioning and tolerancing conform to ANSI Y14.5M-1982.

- 5. Dimensions: Inch (mm). Controlling dimension: Inch.

Submit Document Feedback 16 June 3, 2016 FN8376.2