## XRC 100 BASE-TX/FX REPEATER CONTROLLER

#### 1.0 FEATURES

- Eight 100 BASE-TX/FX ports; each port individually configurable to TX or FX

- Direct interface with analog clock generation/recovery chips

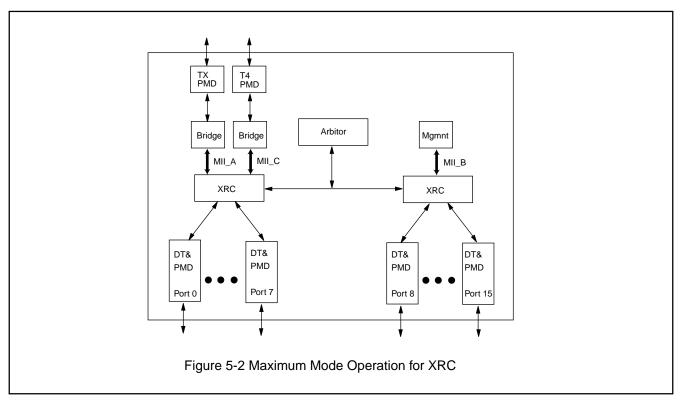

- Three Media Independent Interface (MII)

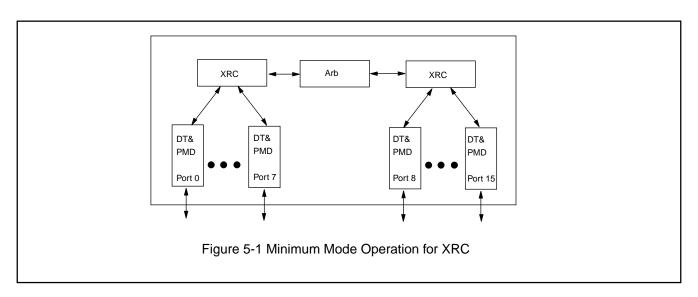

- Expandable to increase number of repeater ports

- Low latency design simplified high port number Class II repeater implementation

- Management features accessible through MII or serial ports

- All ports can be separately isolated or partitioned in reponse to fault conditions

- Conforms to IEEE 802.3u Repeater Unit Specification

- LED display for TX/FX port activities and collisions

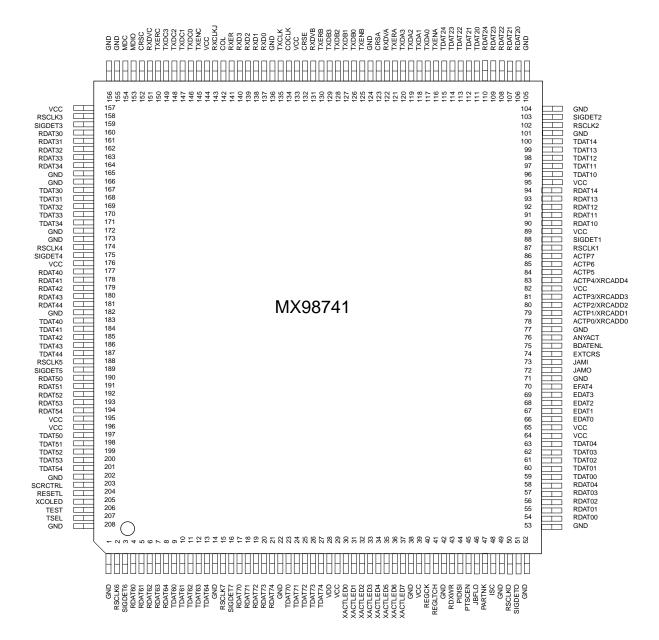

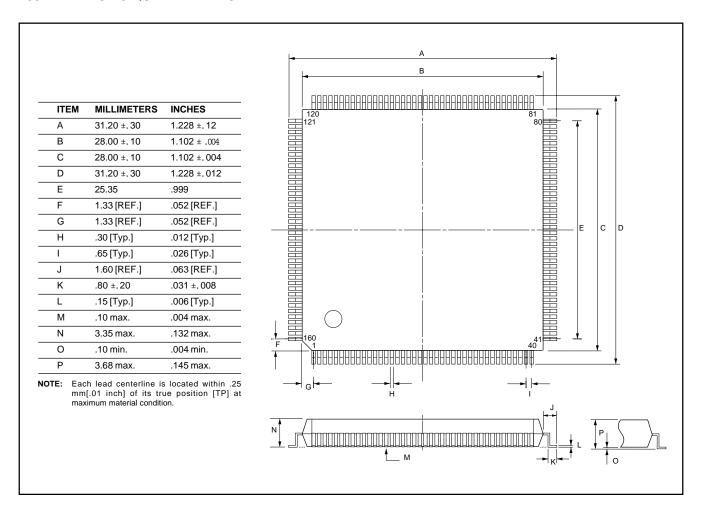

- 208-pin, CMOS device in PQFP package

#### 2.0 GENERAL DESCRIPTION

The MX98741 (100BASE-TX Repeater Controller, XRC) is a 208-pin PQFP device that interfaces directly with offshell clock generation/recovery chips. Eight ports can be configured as 100 BASE-TX or FX ports individually. Three additional ports have Media Independent Interfaces (MII) which allow easy connection of management and bridge devices. The expansion port allows multiple XRCs to be linked together to form a repeater of high port counts. LEDs are provided for visual monitoring of TX/FX port activities and collisions.

The XRC's design inserts minimum delay between the TX/FX ports and the expansion port. A master-slave type arbitration is also implemented to shorten the communciation time among multiple XRCs. As a result, design for Class II stackable hub is greatly simplified.

Control Functions and management status are implemented through internal registers. These registers are accessed via either standard MII management interface (MDC, MDIO) or several serial ports. These serial ports are accessed easily by hardware for debugging and configuration purposes. A dedicated management chip can also utilize these serial ports to access the XRC.

#### 3.0 PIN CONFIGURATION

## **4.0 PIN DESCRIPTION**

Table 4-1 Pin Description for MX98741

|         | A. MX Data Trans | ceiver (Am7 | 78965/Am78966 or MC68836), 98 pins                                     |

|---------|------------------|-------------|------------------------------------------------------------------------|

| PAD#    | Name             | I/O         | Description                                                            |

| 59-63   | TDAT[0:7][0:4]   | O, EXP      | Transmit Data. These five outputs are 4B/5B encoded transmit           |

| 96-100  |                  |             | data symbols, driven at the rising edge of TXCLK.                      |

| 111-115 |                  |             | TDAT4 is the Most Significant Bit.                                     |

| 167-171 |                  |             |                                                                        |

| 183-187 |                  |             |                                                                        |

| 197-201 |                  |             |                                                                        |

| 9-13    |                  |             |                                                                        |

| 23-27   |                  |             |                                                                        |

| 135     | TXCLK            | I, TTL      | Transmit Clock. This pin supplies the frequency reference to the       |

|         |                  |             | transmit logic. It should be driven by an external 25 MHz              |

|         |                  |             | crystal-controlled clock source.                                       |

| 54-58   | RDAT[0:7][0:4]   | I, TTL      | Receive Data. These 5-bit parallel data symbols from transceiver       |

| 90-94   |                  |             | are latched by the rising edge of RSCLK.                               |

| 106-110 |                  |             | RDAT4 is the Most Significant Bit.                                     |

| 160-164 |                  |             |                                                                        |

| 177-181 |                  |             |                                                                        |

| 190-194 |                  |             |                                                                        |

| 4-8     |                  |             |                                                                        |

| 17-21   |                  |             |                                                                        |

| 50,87   | RSCLK[0:7]       | I, TTL      | Recovered Sumbol Clock. This is a 25 MHz clock, which is derived       |

| 102,158 |                  |             | from the clock synchroniztion PLL circuit.                             |

| 174,188 |                  |             |                                                                        |

| 2,15    |                  |             |                                                                        |

| 51,88   | SIGDET[0:7]      | I, TTL      | Signal Detect. This signal indicates that the received signal is above |

| 103,159 |                  |             | the detection threshold and will be used for the link test state       |

| 175,189 |                  |             | machine.                                                               |

| 3,16    |                  |             |                                                                        |

| 134     | COCLK            | I, TTL      | Core Clock. 50M Clock input used by Repeater Core.                     |

|           |              |            | pansion Port, 18 pins                                                 |

|-----------|--------------|------------|-----------------------------------------------------------------------|

| PAD #     | Name         | I/O        | Description                                                           |

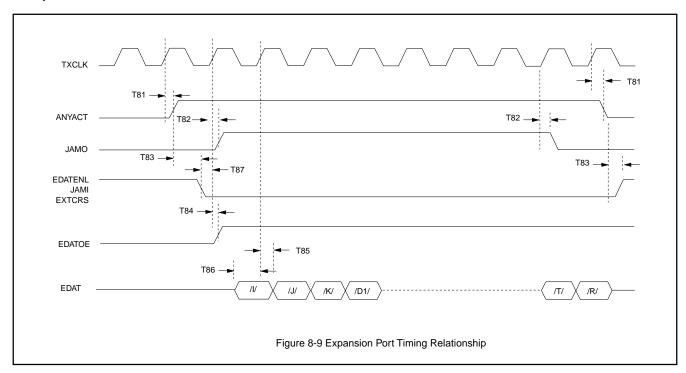

| 72        | JAMO         | O, TTL     | Forced Jam Out. Active High. The OR'd forced jam signals ex           |

|           |              |            | clude JAMI input) controlled by Carrier Integrity Monitor of each     |

|           |              |            | port. If collision occurs inside the XRC, this pin is also asserted.  |

| 73        | JAMI         | I, Schm    | Forced Jam Input. Active High. Asserted by external arbiter, and      |

|           |              |            | XRC will generate JAM patterns to all its ports.                      |

|           |              |            | Note: Glitch on JAMI and EDATENL may cause internal state             |

|           |              |            | machine malfunction.                                                  |

| 75        | EDATENL      | I, Schm    | Enable Expansion Data. Active Low. Asserted by an external arbitor    |

|           |              |            | XRC will drive data into EDAT.                                        |

| 66-70     | EDAT[0:4]    | I/O, EXP   | Expansion Data. Bidirectional 5-bit wide data. By default, EDAT is    |

|           |              |            | an input. When EDATENL is low, EDAT changed from input mode           |

|           |              |            | to output mode. Internally pull-up.                                   |

| 84-86     | ACTP[5:8]    | O, TTL     | Activity Out. This is the activity of port 58 synchronous to COCL     |

|           |              |            | (50M clock used by core). It also serves as data framing signal fo    |

|           |              |            | the packet on EDAT. ACTP leads EDAT's /J/K/ pattern by more           |

|           |              |            | than 80 ns and deasserted 40ns after the /T/R/ or the last byte o     |

|           |              |            | jam patterns.                                                         |

| 78-81, 83 | ACTP[0:4]    | I/O, TTL   | Activity Out/Physical Address. When RESETL goes high, value           |

|           | /XRCADD[0:4] |            | on ACTP[0;4] will be latched into internal buffer as physical         |

|           |              |            | address of XRC. After reset, these five pins have the same            |

|           |              |            | function as ACTP[5:8].                                                |

| 76        | ANYACT       | O, TTL     | Any Activity. Active High. The OR'd ACTP[7:0] and TXEN A to C         |

|           |              |            | This is used as an indication that an XRC is ready to drive data into |

|           |              |            | EDAT.                                                                 |

| 74        | EXTCRS       | I, Schm    | External Carrier Sense. Active high. Asserted by an external arbito   |

|           |              |            | indicating activity from other XRC's at the expansion port.           |

|           |              | C. Miscell | aneous Pins, 2 pins                                                   |

| 204       | RESETL       | I, Schm    | Reset. Active Low. This signal is output by the system to reset al    |

|           |              |            | the logic on the chip.                                                |

| 203       | SCRCTRL      | I, TTL     | Scrambler Control. If high, the scrambler/descrambler of each por     |

|           |              |            | is individually controlled by MII register 17. If low, the scrambler  |

|           |              |            | descrambler is bypassed in all the ports.                             |

|       |         |          | D. Register Access Pins, 8 pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|---------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAD # | Name    | 1/0      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

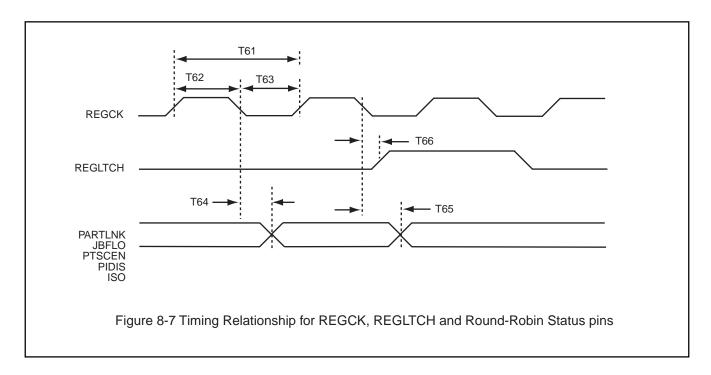

| 47    | PARTLNK | O, TTL   | Partition/Link Status. This pin shows the status of internal register #18 in round-robin fashion starting at port 0 partition status and ending at port7 Link Status after REGLTCH is deasserted.                                                                                                                                                                                                                                                                                                                                                               |

| 46    | JBFLO   | O, TTL   | Jabber/Buffer Status. This pin shows the status of internal register #19 in round-robin fashion starting at port 0 Jabber Status and ending at port 7 Elastic Buffer Over/Underflow Status after REGLTCH is deasserted.                                                                                                                                                                                                                                                                                                                                         |

| 45    | PTSCEN  | I/O, TTL | Port/Scrambler Enable. If RDXWR is high, each port's enable/disable status (register #17) will be displayed at the rising edge of REGCK in round-robin fashion starting at port 0 Port 0 Enable status and ending at port 7 Scrambler Enable status after REGLTCH is deasserted. If RDXWR is low, 16-bit data can be written into the XRC at the rising edge of REGCK in round-robin fashion starting at port 0 Port Enable Signal and ending at port 7 Scrambler enable after REGLTCH is asserted high. Internally pull-up.                                    |

| 44    | PIDIS   | I/O, TTL | Partition/Isolation Disable. If RDXWR is high, each port's partition/ Isolation Disable status will be displayed at the rising edge of REGCK in round-robin fashion starting at port 0 partition disable status and ending at port7 Isolation Disable status after REGLTCH is deasserted. If RDXWR is low, 16-bit data can be written into the XRC at the rising edge of REGCK in round-robin fashion starting at port 0 partition disable status and ending at port 7 Isolation disable status after REGLTCH is asserted high. Internally pull-down.           |

| 48    | ISO     | O, TTL   | Isolation. Active High. Each port's isolation status will be displayed at the rising edge of REGCK in round-robin fashion starting at port0 after REGLTCH is deasserted.                                                                                                                                                                                                                                                                                                                                                                                        |

| 43    | RDXWR   | I, TTL   | Read/Write. High indicates "Read" mode; register is being read out. REGLTCH is output. Low indicates "Write" mode; control registers are being written and REGLTCH is input. When RDXWR is programmed to "Write" Mode, internal "Read" status machine will be reset immediately.                                                                                                                                                                                                                                                                                |

| 41    | REGLTCH | I/O, TTL | Register Latch. An output if RDXWR is high; an input if RDXWR is low. At the rising edge of REGCK, PARTLNK, JBFLO, PTSCEN, PIDIS, ISO display bit 0 status of corresponding registers, at the rising edge of next REGCK, bit 1 status is displayed, etc. After bit 15 is displayed, REGLTCH is asserted at the rising edge of next REGCK. Note: Both Data and REGLTCH are driven at the falling edge of REGCK inside the XRC. To make sure the data setup time, it is strongly recommended that the frequency of REGCK is below 12.5 MHz. Internally pull-down. |

| 40    | REGCK   | I, TTL   | Register Clock. A clock used as reference to display various status of each port or to latch control information inside XRC. The recommended clock's frequency is below 12.5MHz.                                                                                                                                                                                                                                                                                                                                                                                |

|         |              | E. LED P | ins, 9 pins                                                           |

|---------|--------------|----------|-----------------------------------------------------------------------|

| PAD#    | Name         | I/O      | Description                                                           |

| 30-37   | XACTLED[0:7] | O, TTL   | Activity LED. Active Low. This pin provides a minimum 80ms ON         |

|         |              |          | time (low) and 20ms OFF time (high) for activities on each port.      |

|         |              |          | External buffers are necessary to drive LEDs.                         |

| 205     | XCOLED       | O, MII   | Collision LED. This pin is capable of driving LED directly to display |

|         |              |          | Activity status. The ON (active low) time and OFF (active high)       |

|         |              |          | time of LED's is 80ms and 20ms respectively.                          |

|         |              |          | F. Media Independent Interface (MII), 33 pins                         |

| 116     | TXENA        | I, TTL   | Transmit Enable MII A. Synchronous to the TXCLK's rising edge. It     |

|         |              |          | is asserted by the MAC with the first nibble of the preamble and      |

|         |              |          | remains asserted while all nibbles to be transmitted are presented.   |

| 117-120 | TXDA[0:3]    | I, TTL   | Transmit Data MII A. Synchronous to the TXCLK's rising edge. For      |

|         |              |          | each TXCLK period in which TXENA is asserted, TXDA[3:0] are           |

|         |              |          | also driven by the MAC. While TXENA is de-asserted, the value of      |

|         |              |          | TXDA[3:0] is ignored. TXDA3 is the Most Significant Bit.              |

| 121     | TXERA        | I, TTL   | Transmit Error MII A. Synchronous to the TXCLK's rising edge.         |

|         |              |          | When TXERA is asserted for one or more TXCLK period while             |

|         |              |          | TXENA is also asserted, one or more "HALT" symbols will present       |

|         |              |          | at TDAT4_0.                                                           |

| 122     | RXDVA        | O, TTL   | Receive Data Valid MII A. Synchronous to RXCLK's rising edge.         |

|         |              |          | This signal remains asserted through the whole frame, starting with   |

|         |              |          | the start-of-frame delimiter and excluding any end-of-frame delim-    |

|         |              |          | iter. High impedance after reset.                                     |

| 123     | CRSA         | O, TTL   | Carrier Sense MII A. In TX mode, synchronous to RXCLK. This           |

|         |              |          | pin is asserted when (1) the receiving medium is not idle, or (2) the |

|         |              |          | transmitting medium is not idle in the half-duplex mode. High im-     |

|         |              |          | pedance after reset.                                                  |

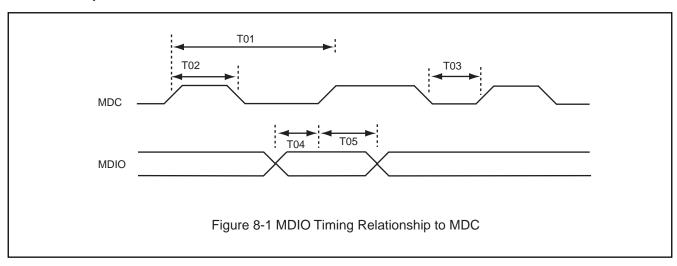

| 153     | MDIO         | I/O, TTL | Management Data Input/Output. A bi-directional signal. After re-      |

|         |              |          | set, this pin is in high-impedance state. The selection of input/     |

|         |              |          | output direction is based on IEEE 802.3u management functions         |

|         |              |          | (Section 22.2.4). Low after reset due to internally pull-down. When   |

|         |              |          | RDXWR is low (i.e. Write operation, MDIO will be forced to low to     |

|         |              |          | disable the function of MDC and MDIO. i.e. Programming internal       |

|         |              |          | registers through register access pins owns higher priority.          |

| PAD#    | Name      | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 125     | TXENB     | I, TTL | Transmit Enable MII B. Synchronous to the TXCLK's rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |           |        | is asserted by the MAC with the first nibble of the preamble ar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |           |        | remains asserted while all nibbles to be transmitted are presente                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 126-129 | TXDB[0:3] | I, TTL | Transmit Data MII B. Synchronous to the TXCLK's rising edge. F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |           |        | each TXCLK period in which TXENB is asserted, TXDB[3:0] a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |           |        | also driven by the MAC. While TXENB is de-asserted, the value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |           |        | TXDB[3:0] is ignored. TXDB3 is the Most Significant Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 130     | TXERB     | I, TTL | Transmit Error MII B. Synchronousto the TXCLK's rising edge. Wh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |           |        | TXERB is asserted for one or more TXCLK period while TXENE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |           |        | also asserted, one or more "HALT" symbols will present at TDAT4_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 131     | RXDVB     | O, TTL | Receive Data Valid MII B. Synchronous to RXCLK's rising edg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |           |        | This signal remains asserted through the whole frame, starting w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |           |        | the start-of-frame delimiter and excluding any end-of-frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |           |        | deliminter. High impedance after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 132     | CRSB      | O, TTL | Carrier Sense MII B. In TX mode, synchronous to RXCLK. T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |           |        | pin is asserted when (1) the receiving medium is not idle, or (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |           |        | transmitting medium is not idle in the half-duplex mode. High i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |           |        | pedance after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 145     | TXENC     | I, TTL | Transmit Enable MII C. Synchronous to the TXCLK's rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |           |        | is asserted by the MAC with the first nibble of the preamble a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |           |        | remains asserted while all nibbles to be transmitted are presented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 146-149 | TXDC[0:3] | I, TTL | Transmit Data MII C. Synchronous to the TXCLK's rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |           |        | each TXCLK period in which TXENC is asserted, TXDC[3:0] a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |           |        | also driven by the MAC. While TXENC is de-asserted, the value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |           |        | TXDC[3:0] is ignored. TXDC3 is the Most Significant Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 150     | TXERC     | I, TTL | Transmit Error MII C. Synchronousto the TXCLK's rising ed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         |           |        | When TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is asserted for one or more TXCLK period when TXERC is a second contains the transfer of the transfer of the transfer or the transfer of the transfer o |