# Am79C864A

# Physical Layer Controller With Scrambler (PLC-S)

#### DISTINCTIVE CHARACTERISTICS

- Implements FDDI PHY layer protocol for ISO standard (FDDI) 9314-1

- Implements ANSI standard Stream Cipher Scrambling/Descrambling

- Hardware Physical Connection Management (PCM) support

- Performs Physical Connection insertion and removal

- On-chip Link Error Monitor (LEM) and Link Confidence Test (LCT)

- Line state detection

- Repeat filter

- Elasticity buffer and smoother functions

- 4B/5B encoding/decoding

- **■** Full duplex operation

- Data framing

- **■** Built-in Self Test

#### **GENERAL DESCRIPTION**

The Physical Layer Controller with Scrambler (PLC-S) is a CMOS device which along with Physical Data Transmitter (PDT) and Physical Data Receiver (PDR) implements the Physical Layer Protocol (PHY) and portions of the Station Management (SMT) of the ANSI Fiber Distributed Data Interface (FDDI) standard. The PLC-S, PDT and PDR are collectively known as the AmPHY. PHY functions performed by the PLC-S include framing of data on symbol pair boundaries, the elasticity buffer function, the smoothing function, 4B/5B encoding and decoding of symbols, line state detection, the repeat filter function, and Stream Cipher Scrambling/Descrambling. SMT functions performed include Physical Connection Management (PCM), Physical Connection insertion and removal and Error Monitor.

The PLC-S chip receives symbol-wide (5 bits) data along with a 25 MHz recovered clock from the PDR chip and searches for a JK symbol pair (also known as Starting Delimiter). It uses the starting delimiter to establish byte boundaries (i.e. to frame the data).

Framed data is then sent to the Elasticity Buffer which serves to compensate for the frequency difference between the recovered clock and the local clock. Data output by the Elasticity Buffer is checked by the Smoother and when necessary, Idle symbols are inserted between frames to maintain a minimum number of Idle symbols in the interframe gap.

The data is then decoded and sent to the Media Access Control (MAC) chip. The data is byte-wide (10 bits) and is clocked by a 12.5 MHz local clock.

The PLC-S receives byte-wide data from the MAC at 12.5 million bytes per second, encodes the data and sends out symbol-wide data at 25 million symbols per second to PDT chip. In the transmit path, there is a Repeat Filter to detect corrupted symbols and convert them into the specified pattern of Halt and Idle symbols. The Repeat Filter in each PLC-S chip converts the last byte of a frame fragment into Idle symbols and thus eventually removing fragments from the ring.

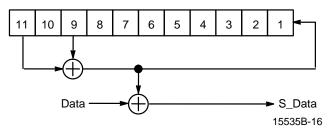

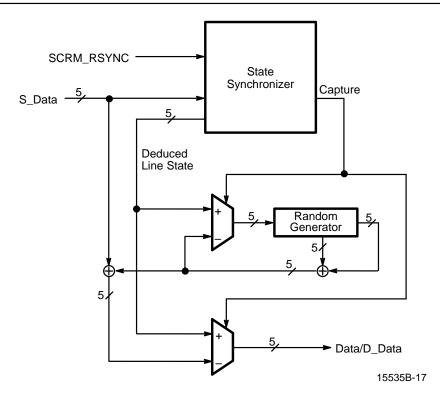

The PLC-S device includes a Stream Cipher Scrambler/ Descrambler as prescribed in the ANSI TP-PMD standard for transmission over twisted-pair cable. For copper-based designs, the scrambler/descrambler may be enabled either through software or hardware. For fiber-based designs, the scrambler/descrambler is disabled by default. For a detailed description of the ANSI-compliant copper FDDI system using the PLC-S device, refer to AMD PID #18258A, *Implementing FDDI over Copper; The ANSI X3T9.5 Standard.*

The PCM initializes the connection of neighboring PHYs and manages the PHY signaling. PCM consists of the PCM state machine, which determines the timing and state requirements for PCM, and the PCM Pseudo Code, which provides the information to be communicated to the neighboring PCM and specifies the connection policies. The PLC-S chip contains the PCM State Machine, while the PCM Pseudo Code is controlled by software. The PCM State Machine communicates with other PCMs using a bit signaling mechanism whereby certain line states are received and transmitted. The PCM also makes use of the Link Error Monitor in the

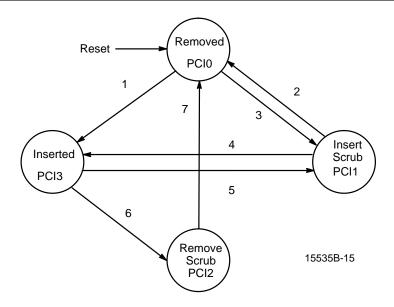

PLC-S chip during Link Confidence Test and after the link has been formed, to detect a noisy link. The PLC-S contains a Line State Machine for detecting received line states and a Data Stream Generator for transmitting the various line states. The PLC-S also contains a state machine called Physical Connection Insertion (PCI) which is used in Physical Connection insertion and removal. It performs the necessary ring scrubbing and data path switching.

The Node Processor Interface in the PLC-S consists of several control and status registers. The PLC-S also contains error and special event counters, Built In Self Test (BIST) logic, Boundary Scan logic, and several data loopback multiplexers so that internal data paths may be reconfigured for test purposes.

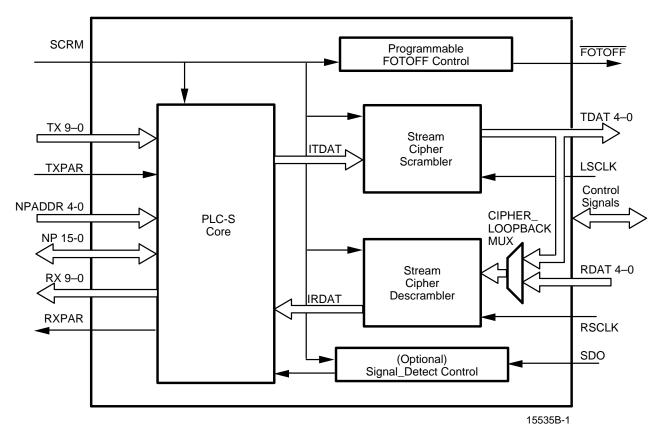

### **PLC-S BLOCK DIAGRAM**

See next page for the PLC-S Core block diagram

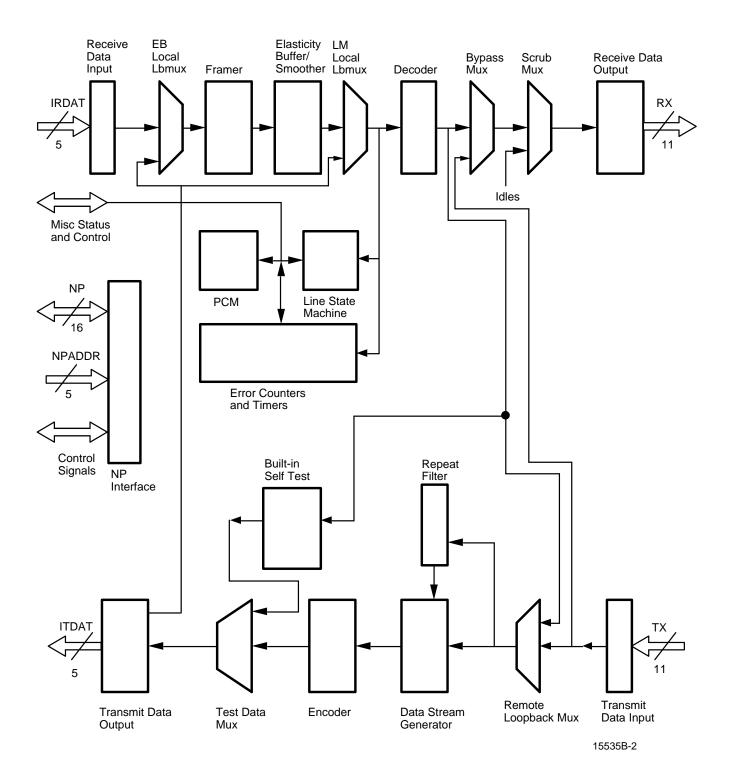

# **PLC-S CORE BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| DISTINCTIVE CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |

| PLC-S BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                   |

| PLC-S CORE BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                              |

| TABLE OF CONTENTS   3-6                                                                                                                                                                                                                                                                                                                                               |

| CONNECTION DIAGRAM                                                                                                                                                                                                                                                                                                                                                    |

| PIN DESIGNATIONS                                                                                                                                                                                                                                                                                                                                                      |

| <b>LOGIC SYMBOL</b> 3-10                                                                                                                                                                                                                                                                                                                                              |

| ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                  |

| PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |

| FUNCTIONAL DESCRIPTION3-15Node Processor Interface3-15Read Cycle3-15Write Cycle3-15Registers3-17PLC-S Control and Status Registers3-17Physical Connection Management Timers3-27Physical Connection Management Timing Parameters3-28Physical Connection Management Bit Signaling Registers3-28Event Counters3-28Interrupt Registers3-30Built In Self Test Register3-32 |

| Framer                                                                                                                                                                                                                                                                                                                                                                |

| Elasticity Buffer                                                                                                                                                                                                                                                                                                                                                     |

| Smoother Operation                                                                                                                                                                                                                                                                                                                                                    |

| Line State Machine (LSM)                                                                                                                                                                                                                                                                                                                                              |

| Link Error Monitor                                                                                                                                                                                                                                                                                                                                                    |

| Physical Connection Management (PCM)       3-33         PCM Operation       3-35         PCM State Machine       3-35         Pseudo Code Bit Signaling       3-35         PCI Operation       3-37         PCI State Machine       3-38                                                                                                                              |

# **TABLE OF CONTENTS**

| Decoder 3-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Encoder 3-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Scrambler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Descrambler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Repeat Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Data Stream Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Data Path MUXes       3-43         EB Local Loopback MUX       3-43         Cipher Loopback MUX       3-43         LM Local Loopback MUX       3-43         Bypass MUX       3-43         Remote Loopback MUX       3-43         Scrub MUX       3-43         Test Data MUX       3-44         Data Input/Output       3-44         Receive Data Input       3-44         Receive Data Output       3-44         Transmit Data Input       3-44         Transmit Data Output       3-44         Transmit Data Output       3-44         Transmit Data Output       3-44 |

| Built In Self Test (BIST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ABSOLUTE MAXIMUM RATINGS 3-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OPERATING RANGES 3-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DC CHARACTERISTICS 3-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>CAPACITANCE</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SWITCHING CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

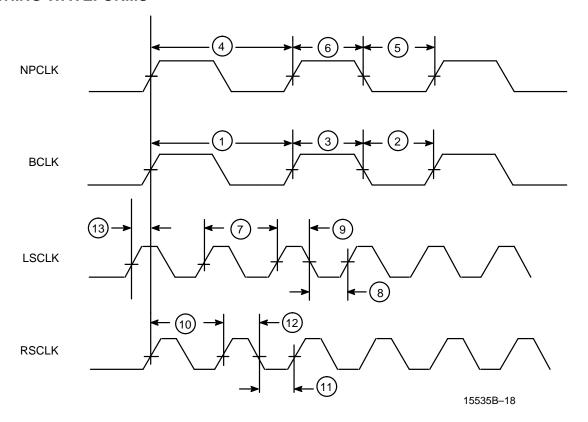

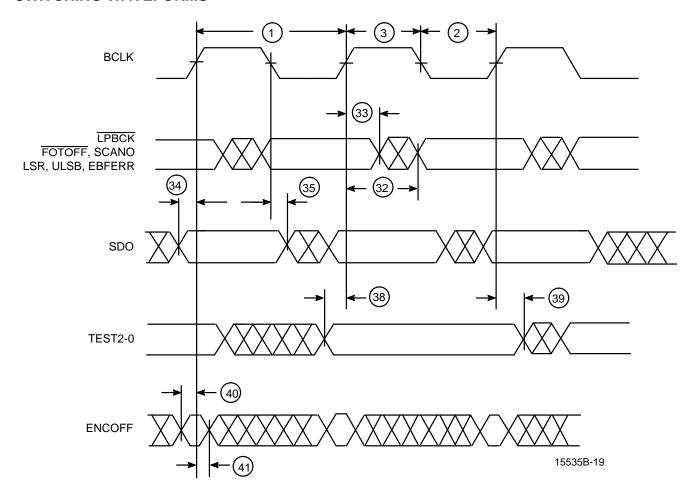

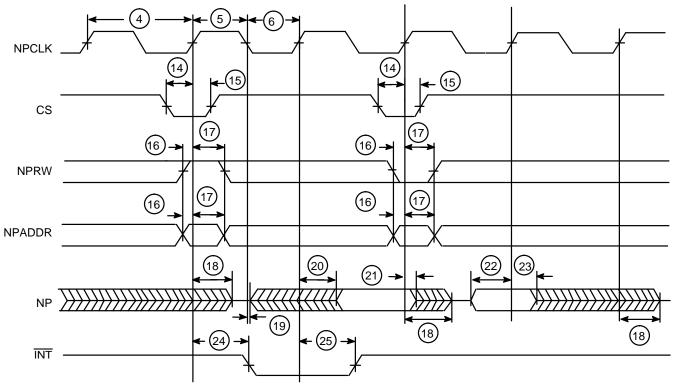

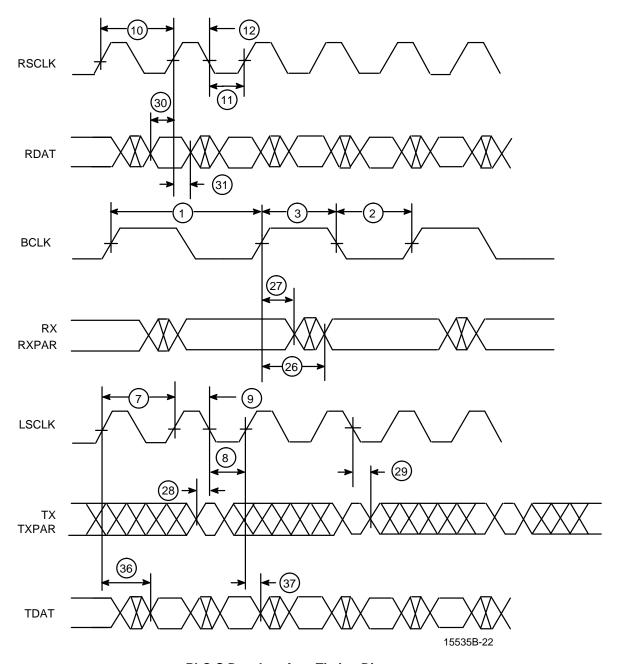

| SWITCHING WAVEFORMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

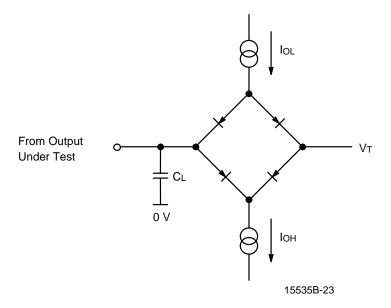

| SWITCHING TEST CIRCUIT 3-52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

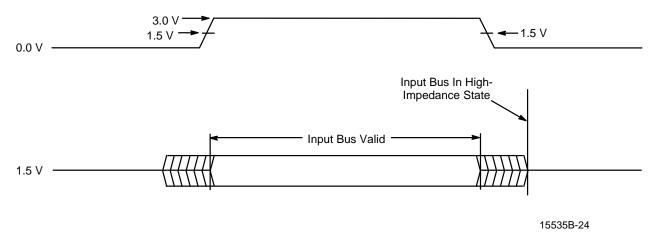

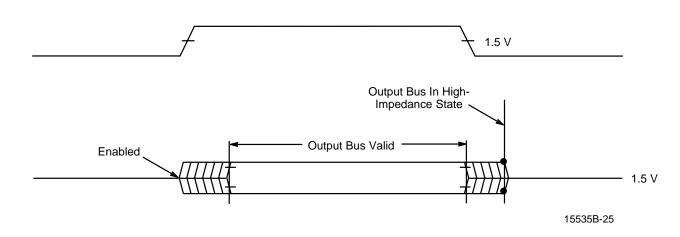

| SWITCHING TEST WAVEFORMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

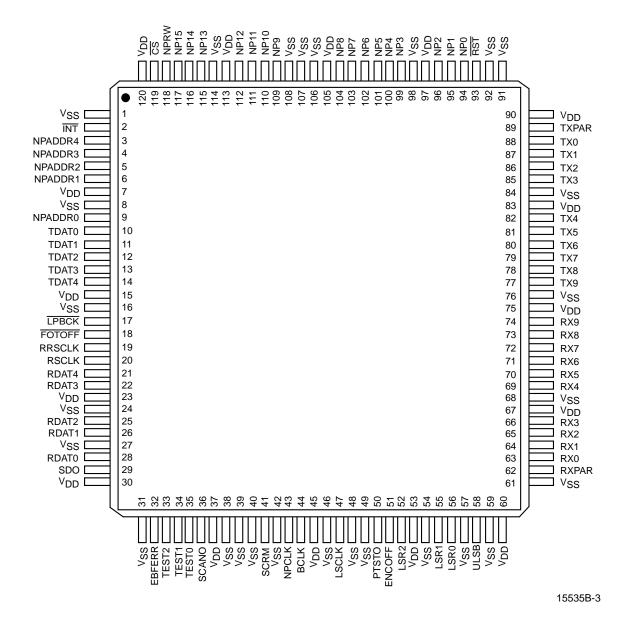

# CONNECTION DIAGRAM 120-Pin PQR (Top View)

# **PQFP PIN DESIGNATIONS**

# **Listed by Pin Number**

| Pin Number | Pin Name        |

|------------|-----------------|------------|-----------------|------------|-----------------|------------|-----------------|

| 1          | V <sub>SS</sub> | 31         | V <sub>SS</sub> | 61         | V <sub>SS</sub> | 91         | V <sub>SS</sub> |

| 2          | ĪNT             | 32         | EBFERR          | 62         | RXPAR           | 92         | Vss             |

| 3          | NPADDR4         | 33         | TEST2           | 63         | RX0             | 93         | RST             |

| 4          | NPADDR3         | 34         | TEST1           | 64         | RX1             | 94         | NP0             |

| 5          | NPADDR2         | 35         | TEST0           | 65         | RX2             | 95         | NP1             |

| 6          | NPADDR1         | 36         | SCANO           | 66         | RX3             | 96         | NP2             |

| 7          | $V_{DD}$        | 37         | $V_{DD}$        | 67         | $V_{DD}$        | 97         | $V_{DD}$        |

| 8          | $V_{SS}$        | 38         | $V_{SS}$        | 68         | V <sub>SS</sub> | 98         | $V_{SS}$        |

| 9          | NPADDR0         | 39         | $V_{SS}$        | 69         | RX4             | 99         | NP3             |

| 10         | TDAT0           | 40         | $V_{SS}$        | 70         | RX5             | 100        | NP4             |

| 11         | TDAT1           | 41         | SCRM            | 71         | RX6             | 101        | NP5             |

| 12         | TDAT2           | 42         | $V_{SS}$        | 72         | RX7             | 102        | NP6             |

| 13         | TDAT3           | 43         | NPCLK           | 73         | RX8             | 103        | NP7             |

| 14         | TDAT4           | 44         | BCLK            | 74         | RX9             | 104        | NP8             |

| 15         | $V_{DD}$        | 45         | $V_{DD}$        | 75         | $V_{DD}$        | 105        | $V_{DD}$        |

| 16         | $V_{SS}$        | 46         | $V_{SS}$        | 76         | Vss             | 106        | $V_{SS}$        |

| 17         | <b>LPBCK</b>    | 47         | LSCLK           | 77         | TX9             | 107        | V <sub>SS</sub> |

| 18         | FOTOFF          | 48         | $V_{SS}$        | 78         | TX8             | 108        | Vss             |

| 19         | RRSCLK          | 49         | $V_{SS}$        | 79         | TX7             | 109        | NP9             |

| 20         | RSCLK           | 50         | PTSTO           | 80         | TX6             | 110        | NP10            |

| 21         | RDAT4           | 51         | ENCOFF          | 81         | TX5             | 111        | NP11            |

| 22         | RDAT3           | 52         | LSR2            | 82         | TX4             | 112        | NP12            |

| 23         | $V_{DD}$        | 53         | $V_{DD}$        | 83         | $V_{DD}$        | 113        | $V_{DD}$        |

| 24         | $V_{SS}$        | 54         | $V_{SS}$        | 84         | V <sub>SS</sub> | 114        | V <sub>SS</sub> |

| 25         | RDAT2           | 55         | LSR1            | 85         | TX3             | 115        | NP13            |

| 26         | RDAT1           | 56         | LSR0            | 86         | TX2             | 116        | NP14            |

| 27         | V <sub>SS</sub> | 57         | $V_{SS}$        | 87         | TX1             | 117        | NP15            |

| 28         | RDAT0           | 58         | ULSB            | 88         | TX0             | 118        | NPRW            |

| 29         | SDO             | 59         | $V_{SS}$        | 89         | TXPAR           | 119        | <del>cs</del>   |

| 30         | $V_{DD}$        | 60         | $V_{DD}$        | 90         | $V_{DD}$        | 120        | $V_{DD}$        |

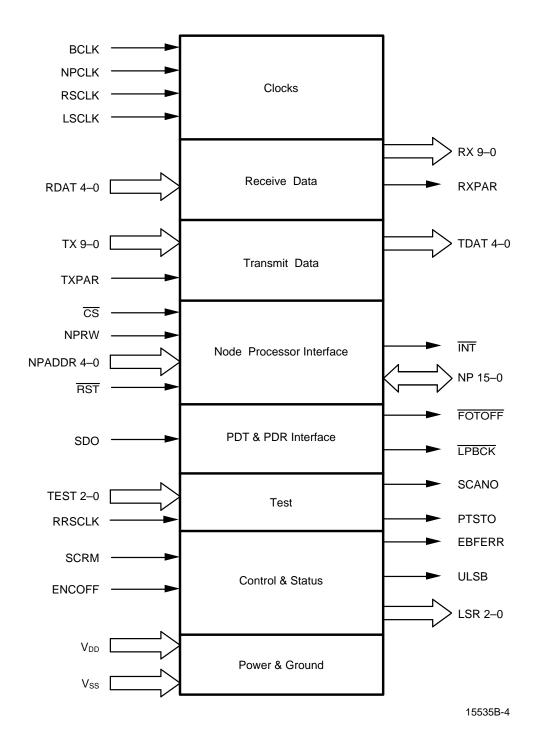

## LOGIC SYMBOL

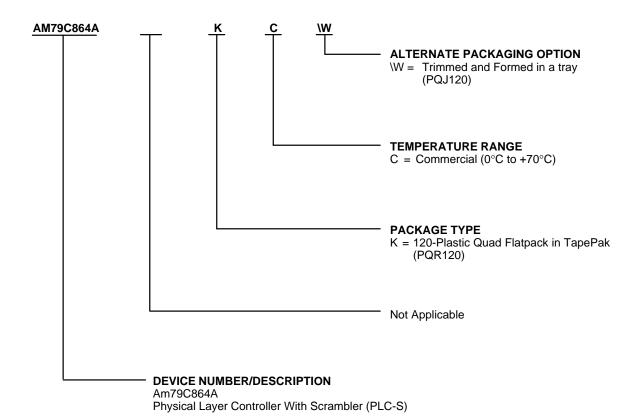

# ORDERING INFORMATION

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |          |  |

|--------------------|----------|--|

| AM79C864A          | KC, KC\W |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

#### PIN DESCRIPTION

## **Clock Signals**

#### **BCLK**

### **Byte Clock (Input)**

BCLK is a 12.5 MHz clock. It is used by the PLC-S to clock most internal operations, clock RX 9–0 to the MAC device and, along with LSCLK, latch TX 9–0 from the MAC device.

#### **NPCLK**

#### **Node Processor Clock (Input)**

NPCLK is used to latch Node Processor inputs, run the Node Processor Interface state machine, and clock output signals to the Node Processor. It is distinct from the BCLK for test and diagnostic purposes only. For normal operations, the BCLK and NPCLK pins MUST be tied together.

#### **RSCLK**

#### **Recovered Symbol Clock (Input)**

RSCLK is a 25 MHz clock. It is recovered from the data sent to the Physical Data Receiver (PDR) by the upstream station in the ring. It is used to latch RDAT 4–0 from the PDR device. It is also used for clocking the Framer and the Elasticity Buffer input controller.

#### **LSCLK**

#### **Local Symbol Clock (Input)**

LSCLK is a 25 MHz clock. It is used by the PLC-S to clock TDAT 4–0 to the Physical Data Transmitter (PDT) and, along with BCLK, to latch TX 9–0 from the MAC device.

#### **Receive Data Signals**

### **RX 9-0**

#### **Receive Data Bus (Output)**

RX 9–0 is a ten bit output bus used to transfer symbol pairs from the PLC-S to a MAC device, or to another PLC-S. The ten bits are clocked to the MAC device on the rising edge of BCLK. RX 9–5 contain the most significant symbol and RX 4–0 contain the least significant symbol of the framed byte. Bit 9 is the upper control bit and bit 4 is the lower control bit.

#### **RXPAR**

#### **Receive Data Parity bit (Output)**

RXPAR is an output signal used to enhance error detection on the RX bus. If there is an odd number of ones on RX 9–0 then RXPAR will be one, and if there is an even number of ones on RX 9–0 then RXPAR will be zero (even parity). When the PLC-S is in Bypass mode (that is when the data output on RX 9–0 is the data input on TX 9–0) RXPAR is not calculated and is just the value input on TXPAR.

#### **RDAT 4-0**

#### **Receive Data Bus (Input)**

RDAT 4–0 is a five bit input bus used to transfer data from the PDR device to the PLC-S. Data is latched by the PLC-S on the rising edge of RSCLK.

## **Transmit Data Signals**

#### **TDAT 4-0**

#### **Physical Transmit Data Bus (Output)**

TDAT 4–0 is a five bit output bus used to transfer symbols from the PLC-S to the PDT. The symbols are clocked to the PDT on the rising edge of LSCLK.

#### TX 9-0

#### **Transmit Data Bus (Input)**

TX 9–0 is a ten bit input bus used to transfer symbol pairs from a MAC device, or from another PLC-S, to the PLC-S. The ten bits are latched by the PLC-S on the falling edge of LSCLK. Bits 9–5 of the bus contain the first symbol to be transmitted on the fiber and bits 4–0 contain the second symbol. Bit 9 is the upper control bit and bit 4 is the lower control bit.

#### **TXPAR**

#### **Transmit Data Parity bit (Input)**

TXPAR is an input signal used to implement even parity on the TX bus. If there is an odd number of ones on TX 9–0 then TXPAR should be one and if there is an even number of ones on TX 9–0 then TXPAR should be zero.

### **Node Processor Interface Signals**

#### $\overline{\mathsf{INT}}$

## Interrupt (Output, Active Low)

The INT signal indicates an interrupt request from the PLC-S. This signal is active until cleared by reading the INTR\_EVENT register at address 17 (hex).

#### **CS**

#### **Chip Select (Input, Active Low)**

CS selects the PLC-S for the current bus cycle.

#### NPADDR 4-0

#### **Node Processor Address Bus (Input)**

The NPADDR 4–0 bus is a five bit input bus used to select one of the registers in the PLC-S for a read or write cycle.

#### NP 15-0

# Node Processor Data Bus (Input/Output, Three State)

The NP 15–0 bus is a sixteen bit bi-directional, three-state data bus used to exchange data between the PLC-S and the Node Processor.

#### **NPRW**

#### Node Processor Read/Write (Input)

The NPRW signal indicates whether the current bus cycle is a read (NPRW = 1) or a write (NPRW = 0) cycle.

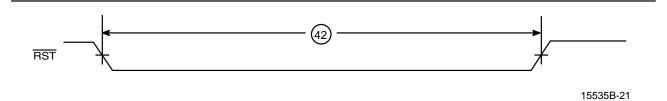

#### **RST**

#### Reset (Input, Active Low, Asynchronous)

The RST signal provides a means of initializing the PLC-S on power up. When asserted, the Reset causes the following:

- The various state machines are initialized: LSM-NOT ACTIVE, PCM-OFF, PCI-REMOVED, Repeat Filter on REPEAT, Node Processor Interface-NOT ACTIVE.

- All writable registers are cleared and all registers that are cleared on a read are cleared.

- Built-in Self Test OFF

- The Fiber Optic Transmitter Off (FOTOFF) signal is asserted, Quiet Symbols are transmitted on TDAT, and TX is looped back onto RX.

Once  $\overline{\mathsf{RST}}$  is asserted low, it must remain asserted for at least twenty NPCLK cycles. When it is deasserted the PLC-S is ready to begin its normal operation.

Assertion and deassertion are asynchronous. A warm reset (assertion of RST after the device is in operation) will cause device outputs to be unpredictable until the device is initialized.

# PDT and PDR Interface Signals

# **LPBCK**

#### Loopback (Output, Active Low)

The LPBCK signal controls the receive multiplexer in the PDR device. If LPBCK= 0, the MUX selects its input from the PDT. If LPBCK = 1, the MUX selects its input from the Fiber Optic Receiver.

#### **FOTOFF**

# Fiber Optic Transmitter Off (Output, Active Low)

The FOTOFF signal, when asserted, causes the PDT to transmit Quiet symbols. This signal is asserted whenever:

■ The FOT\_OFF bit, LOOPBACK bit, EB\_LOC\_LOOP bit, LM\_LOC\_LOOP bit in the PLC\_CNTRL\_A register (or) CIPHER\_LPBCK bit in PLC\_CNTRL\_C register is set.

- The MAINT\_LS field in the PLC\_CNTRL\_B register equal Transmit QUIET and the PCM is in the MAINT state and FOTOFF assertion timer expires. if enabled.

- The Physical Connection Management logic has set LS\_REQUEST = Transmit QUIET Line State and FOTOFF assertion timer expires, if enabled.

- Built-in Self Test is active.

#### **SDO**

#### Signal Detect (Input, Active High)

The SDO signal is output by the PDR to indicate whether the Fiber Optic Receiver is detecting an optical signal above its threshold. The inverted value of this signal is held in the PLC\_STATUS\_A register, and the LSDO bit in the INTR\_EVENT register is set when SDO is asserted.

## **Test Signals**

#### **PTSTO**

#### **Parametric Test Output (Output)**

This is an internal parametric test output signal. This pin should be left unconnected.

#### **SCANO**

#### Scan Output (Output)

The SCANO signal is used as an output of the scan chain when the PLC-S is in Boundary Scan Serial Test Mode.

# **TEST 2–0**

### PLC-S Test Mode (Input)

The three TEST 2–0 input pins are used to select between normal operating mode and three different test modes. The different operating modes are as follows:

| TEST 2-0       | Mode of Device Operation                              |

|----------------|-------------------------------------------------------|

| 0 0 0          | Normal Operating Mode                                 |

| 0 1 X          | Normal Operating Mode                                 |

| 0 0 1          | Factory Test Mode (Counter Segmentation Test)         |

| 1 0 Scan Input | Boundary Scan Serial<br>Test Mode                     |

| 1 1 0          | Boundary Scan Parallel<br>Test Mode                   |

| 1 1 1          | All output pins except<br>PTSTO are High<br>Impedance |

#### **RRSCLK**

#### Reserved (Input)

This pin should be connected to VSS.

### **Control and Status Signals**

#### **EBFERR**

#### **Elasticity Buffer Error (Output, Active High)**

EBFERR indicates when an overflow or underflow condition occurs in the Elasticity Buffer.

#### **ENCOFF**

#### **Encoder Off (Input, Active High)**

The ENCOFF signal turns off the encoding and decoding function of the PLC-S. This allows for the transmission of any symbol, including invalid symbols for diagnostic purposes.

#### LSR 2-0

# Line State Register (Output)

The LSR 2–0 signals directly output the LINE\_ST field of the PLC\_STATUS\_A register to ring test and monitor equipment.

| LSR 2-0 | Description                                              |

|---------|----------------------------------------------------------|

| 000     | Noise Line State (NLS)                                   |

| 001     | Active Line State (ALS)                                  |

| 010     | Undefined                                                |

| 011     | Idle Line State (ILS4 – achieved after 4 Idle symbols)   |

| 100     | Quiet Line State (QLS)                                   |

| 101     | Master Line State (MLS)                                  |

| 110     | Halt Line State (HLS)                                    |

| 111     | Idle Line State (ILS16 – achieved after 16 Idle symbols) |

#### **ULSB**

#### **Unknown Line State (Output)**

The ULSB signal directly outputs the UNKN\_LINE\_ST bit of the PLC\_STATUS\_A register to ring test and monitor equipment.

#### **SCRM**

#### **Scrambler Enable (Input)**

This pin when held high will enable the Stream Cipher Scrambling/Descrambling function. If this pin is held low, then bit 0 of PLC\_CNTRL\_C Register determines if Stream Cipher Scrambling/Descrambling function is enabled.

#### **Power and Ground**

#### $V_{DD}$

#### **Power (Inputs)**

The  $V_{DD}$  pins supply +5 V to the device.

#### Vss

#### **Ground (Input)**

The V<sub>SS</sub> pins ground the device.

#### **FUNCTIONAL DESCRIPTION**

# **Node Processor Interface (NPI)**

The Node Processor Interface serves as the interface between an external Node Processor and the PLC-S. The interface is a general purpose synchronous interface.

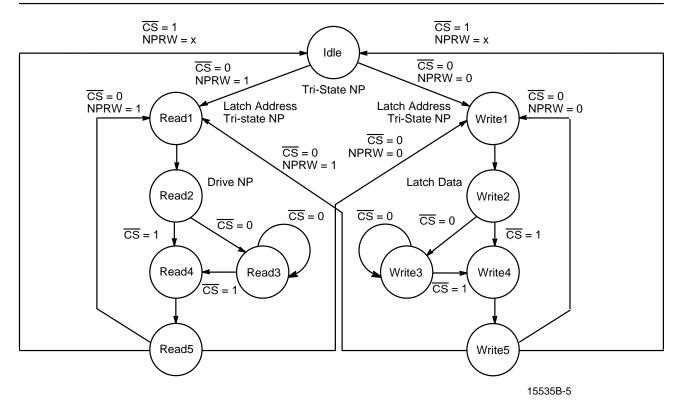

The Node Processor Interface is controlled by the NPCLK. In normal operation this clock is tied to the BCLK. All signals of the NPI must be synchronous with the NPCLK, that is the signals must be stable a setup time before and a hold time after a rising edge of the NPCLK. Figure 1 illustrates the NPI state machine.

#### Read Cycle

A read cycle is used by the Node Processor to read data from a PLC-S register. Normally the PLC-S is unaffected by a read, although the INTR\_EVENT, VIOL\_SYM\_CTR, MIN\_IDLE\_CTR, and LINK\_ERR\_ CTR registers are cleared when read.

A read cycle of one of the PLC-S registers is initiated by the assertion of the CS signal which is sampled by the rising edge of NPCLK. Once the CS signal is asserted the NPADDR bus and NPRW signals are sampled. The NPRW signal should be high for a read and low for a write. At least one half NPCLK cycle after this edge, the PLC-S will begin to drive the NP bus to allow the chip driving the bus in the previous read or write cycle time to tri-state the NP bus.

After the next rising edge of NPCLK (the second rising edge after the assertion of CS), the data on the NP bus will be valid. It will remain valid until the second rising edge of NPCLK after the deassertion of CS. The PLC-S will tri-state the NP bus within 1/2 NPCLK cycle after this clock edge.

The timing described above will allow a read cycle every 2 NPCLK periods. However, if the Node Processor needs to extend the read cycle and have the NP bus valid longer than one clock cycle, it can delay the deassertion of the CS signal. For a minimum length read cycle (2 NPCLK periods), the Node Processor must deassert CS a setup time before the second rising edge of NPCLK following the assertion of CS. If CS remains asserted for a hold time after the second rising edge of NPCLK, again with respect to  $\overline{CS}$  being asserted, the PLC-S will continue to drive the NP bus with valid data for two more rising edges of the NPCLK. When  $\overline{\text{CS}}$  is kept asserted beyond the initial read cycle, the read cycle extends by two NPCLK periods. The CS signal is sampled on the second and each subsequent rising edge of NPCLK after the initial assertion of CS. The Node Processor can indefinitely extend the read cycle by maintaining the assertion of the CS signal. The Node Processor must deassert and then assert the CS signal for each unique read access.

#### **Write Cycle**

A write cycle is used by the Node Processor to write data into a PLC-S control register. The Node Processor is normally allowed to write to any read-write or write-only register at any time except to the following registers XMIT\_VECTOR, VECTOR\_LENGTH, TPC\_LOAD VALUE, and TNE\_LOAD\_VALUE due to special operating conditions imposed by the PLC-S in their usage. If the Node Processor attempts a write on a readonly register or the special registers mentioned above at a wrong time, the PLC-S sets the NP\_ERR bit in the INTR EVENT register. The PLC-S will not modify the contents of the register accessed.

The write cycle is very similar to the read cycle. The principal differences are as follows:

- The NPRW signal must be low while CS is asserted

- The data to be written must be valid on the second rising edge of NPCLK after CS is asserted

The Node Processor must tri-state the NP bus within one half NPCLK period after the second rising edge after the deassertion of CS. Thus, by delaying the deassertion of the CS signal, the Node Processor can extend the write cycle and the time it has to tri-state the NP bus. The deassertion of the CS signal has no effect on the PLC-S during a write cycle. The PLC-S will not attempt to write to a selected register more than once until the CS signal has been deasserted. Thus, to accomplish back to back writes, the Node Processor must deassert the CS signal before attempting the second write.

Figure 1. Node Processor Interface State Machine

# Registers

The PLC-S contains twenty-six 16 bit registers addressed from 00 to 1A (hex). These registers are listed in Table 1.

**Table 1. PLC-S Registers**

| Address<br>(hex) | Name           | Туре                |

|------------------|----------------|---------------------|

| 00               | PLC_CNTRL_A    | read/write          |

| 01               | PLC_CNTRL_B    | read/write          |

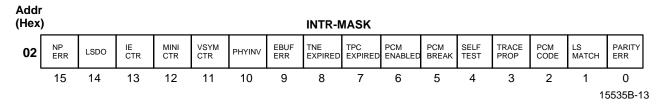

| 02               | INTR_MASK      | read/write          |

| 03               | XMIT_VECTOR    | read/write (Note 1) |

| 04               | VECTOR_LENGTH  | read/write (Note 1) |

| 05               | LE_THRESHOLD   | read/write          |

| 06               | C_MIN          | read/write          |

| 07               | TL_MIN         | read/write          |

| 08               | TB_MIN         | read/write          |

| 09               | T_OUT          | read/write          |

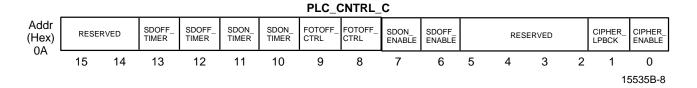

| 0A               | PLC_CNTRL_C    | read/write          |

| 0B LC_LENGTH     |                | read/write          |

| 0C               | T_SCRUB        | read/write          |

| 0D               | NS_MAX         | read/write          |

| 0E               | TPC_LOAD_VALUE | write only (Note 2) |

| 0F               | TNE_LOAD_VALUE | write only (Note 3) |

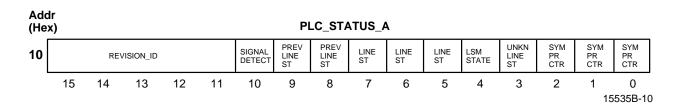

| 10 PLC_STATUS_A  |                | read only           |

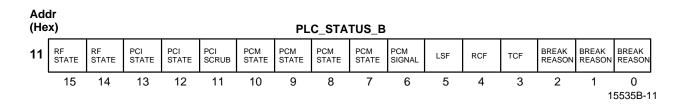

| 11               | PLC_STATUS_B   | read only           |

| 12               | TPC            | read only           |

| 13               | TNE            | read only           |

| 14               | CLK_DIV        | read only           |

| 15               | BIST_SIGNATURE | read only           |

| 16               | RCV_VECTOR     | read only           |

| 17               | INTR_EVENT     | read only (Note 4)  |

| 18               | VIOL_SYM_CTR   | read only (Note 4)  |

| 19               | MIN_IDLE_CTR   | read only (Note 4)  |

| 1A               | LINK_ERR_CTR   | read only (Note 4)  |

#### Notes:

- 1. Writable only when the PCM\_SIGNALING bit in the PLC\_STATUS\_B register is not set.

- 2. Writable only when the PCM is in the MAINT state.

- 3. Writable only when the PCM is in the MAINT state and the NOISE\_TIMER bit in the PLC\_CONTROL\_A register is not set.

- 4. Register cleared on read.

# **PLC-S Control and Status Registers**

The control and status information for the PLC-S is contained in four registers.

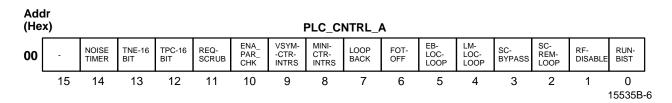

#### PLC-S Control Register A (PLC\_CNTRL\_A)

PLC\_CNTRL\_A has address 00 (hex). It is readable and writable. All bits of this register are cleared with the assertion of RST. PLC\_CNTRL\_A is used for the following functions:

- Timer configuration

- Specification of PCM MAINT state options

- Counter interrupt frequency

- PLC-S data path configuration

- Execution of PLC-S Built In Self Test

Note that several bits of this register can only be written if the PCM is in the OFF or MAINT state. If this register is written when the PCM is in any other state these bits will remain unchanged.

The PLC\_CNTRL\_A register bit assignments are listed in Table 2.

# Table 2. PLC\_CNTRL\_A

| Bit | Name           | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15  |                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 14  | NOISE_TIMER    | The NOISE_TIMER bit allows the noise timing function of the PCM to be used when the PCM is in the MAINT state. This function causes the TNE Timer to be loaded with the value in the NS_MAX register whenever the Line State Machine transitions from Idle Line State to Noise Line State, Active Line State or Unknown Line State. If the timer expires before Idle Line State is recognized, the TNE_EXPIRED bit in the INTR_EVENT register is set.                                                                                                                                          |  |  |

| 13  | TNE_16BIT      | When TNE_16BIT is set it causes the TNE Timer to operate as a 16 bit timer. In this mode the 2 bits of the TNE Clock Divider are bypassed and the TNE Timer is incremented every 80 ns. TNE_16BIT can only be written if the PCM is in the OFF or MAINT state.                                                                                                                                                                                                                                                                                                                                 |  |  |

| 12  | TPC_16BIT      | When TPC_16BIT is set it causes the TPC Timer to operate as a 16 bit timer. In this mode the 8 bits of the TPC Clock Divider are bypassed and the TPC Timer is incremented every 80 ns. TPC_16BIT can only be written if the PCM is in the OFF or MAINT state.                                                                                                                                                                                                                                                                                                                                 |  |  |

| 11  | REQ_SCRUB      | The REQ_SCRUB bit allows limited access to the scrub capability of the PLC-S chip. If the PCM is in the MAINT state or if the CONFIG_CNTRL bit in the PLC_CNTRL_B register is set then the REQ_ SCRUB bit controls the Scrub MUX. If REQ_SCRUB is set then Idle symbols are sourced at the RX 9–0 output port. The output at the TDAT 4–0 output port is controlled separately by the MAINT_LS field in the PLC_CNTRL_B register. This bit may be written at any time, but only takes effect when the PCM is in the MAINT state or if the CONFIG_CNTRL bit in the PLC_CNTRL_B register is set. |  |  |

| 10  | ENA_PAR_CHK    | If this bit is set, then parity checking takes place on TX9–0 lines. If reset, then parity checking is disabled.  Note: PLC-S supports even parity.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 09  | VSYM_CTR_INTRS | The VSYM_CTR_INTRS bit controls when the VSYM_CTR interrupt bit in the INTR_EVENT register is asserted. When VSYM_CTR_INTRS is set, the interrupt is generated only when the VIOL_SYM_CTR overflows (reaches 256). When VSYM_CTR_INTRS is cleared, the interrupt is generated every time the VIOL_SYM_CTR is incremented (whenever a violation symbol is detected).                                                                                                                                                                                                                            |  |  |

| 08  | MINI_CTR_INTRS | The MINI_CTR_INTRS bit partially controls when the MINI_CTR interrupt bit in the INTR_EVENT register is asserted. When MINI_CTR_INTRS is set, the interrupt is generated when the Minimum Idle Gap Counter portion of MIN_IDLE_CTR overflows (reaches16). When MINI_CTR_INTRS is cleared, the interrupt is generated every time the counter is incremented (whenever a minimum length Idle gap is detected). Note that this bit does not affect interrupts caused by the Idle Counter Minimum Detector portion of MIN_IDLE_CTR.                                                                |  |  |

| 07  | LOOPBACK       | When LOOPBACK is set, it causes the LPBCK output pin to be asserted low. This, in turn, causes data to be looped back from the output of the PDT chip to the input of the PDR chip.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

# Table 2. PLC\_CNTRL\_A (continued)

| Bit | Name        | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |                                        |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------|

| 06  | FOT_OFF     | The setting of this bit will cause the assertion of the FOTOFF output pin of the PLC-S.  Read PLC_CNTRL_C register description for behavior of this signal when scrambling/ descrambling is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |                                        |

| 05  | EB_LOC_LOOP | When EB_LOC_LOOP is set, a loopback path is set up in the PLC-S chip just prior to the framer. Data from the PLC-S transit path are looped back to the input of the Framer. This loopback path is also set up when the PLC-S is executing its Built In Self Test. Note that this bit also controls which clock the Framer and Elasticity Buffer use. When it is not set, the Recovered Byte Clock is derived from the RSCLK input pin, and when it is set, the BCLK is used. Thus, when this bit gets set, a clock glitch could be created which could cause receive data to be indeterminate for a clock cycle, spurious interrupts, and unknown values in the event counters. EB_LOC_LOOP can only be written if the PCM is in the OFF or MAINT state.                                                                                                    |                             |                                        |

| 04  | LM_LOC_LOOP | When LM_LOC_LOOP is set a loopback path is set up in the PLC-S chip such that data from TX 9–0 are passed through the PLC-S transmit path and looped back to the input of the receive path just after the Elasticity Buffer at the LM Local Loopback MUX. This loopback path differs from EB_LOC_LOOP in that the Framer and Elasticity Buffer are bypassed. LM_LOC_LOOP can only be written if the PCM is in the OFF or MAINT state.                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |                                        |

| 03  | SC_BYPASS   | The SC_BYPASS bit provides limited control over the PLC-S's data path by providing a physical bypass of the PLC-S. If the PCM is in the MAINT state or if the CONFIG_CNTRL bit in the PLC_CNTRL_B register is set, then the SC_BYPASS bit controls the Bypass MUX. If both SC_BYPASS and REQ_ SCRUB are asserted then RX 9–0 is driven with Idle symbols. If SC_BYPASS is asserted and REQ_SCRUB cleared, then RX 9–0 is driven by the data entering the PLC-S at the TX 9–0 input. Otherwise, RX 9–0 is driven by the data entering the PLC-S at the RDAT 4–0 input. This bit may be written at any time, but only takes effect when the PCM is in its MAINT state or if the CONFIG_CNTRL bit in the PLC_CNTRL_B register is set.                                                                                                                          |                             |                                        |

|     |             | SC_BYPASS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REQ_SCRUB                   | RX 9-0                                 |

|     |             | SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SET                         | IDLE                                   |

|     |             | SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RESET                       | TX 9–0                                 |

|     |             | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RESET                       | RDAT 4–0                               |

|     |             | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SET                         | RDAT 4–0                               |

| 02  | SC_REM_LOOP | When SC_REM_LOOP is set, a remote loopback path is set up inside the PLC-S where symbols from the receive data path are looped back onto the transmit data path, traversing all of both paths except for the receive data output latch and the transmit data input latch. If the PCM is in the MAINT state or if the CONFIG_CNTRL bit in the PLC_CNTRL_B register is set, then the SC_REM_LOOP bit controls the Remote Loopback MUX. This loopback is used by the PCM to control the configuration and can be used to monitor the ring or otherwise control configuration during normal operation. This bit only has effect if the EB_LOC_LOOP, LM_LOC_LOOP and CIPHER_LPBCK bits are not set. This bit may be written at any time, but only takes effect when the PCM is in the MAINT state or if the CONFIG_CNTRL bit in the PLC_CNTRL_B register is set. |                             |                                        |

| 01  | RF_DISABLE  | When RF_DISABLE i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | s set, it disables the Repe | eat Filter state machine in the PLC-S. |

| 00  | RUN_BIST    | When RF_DISABLE is set, it disables the Repeat Filter state machine in the PLC-S.  When RUN_BIST is set, it causes the PLC-S to begin running its Built In Self Test. The completion of BIST is indicated via an interrupt. BIST can be stopped before completion by clearing this bit. Once BIST has completed, this bit must be cleared and set again before BIST will restart. For more detail, refer to pages 30 and 42.  Reset PLC-S before setting this bit.                                                                                                                                                                                                                                                                                                                                                                                          |                             |                                        |

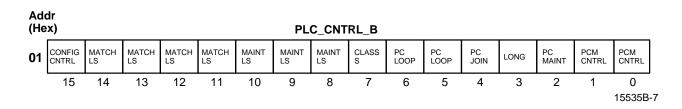

# PLC-S Control Register B (PLC\_CNTRL\_B)

PLC\_CNTRL\_B has address 01 (hex). It is readable and writeable. All bits of this register are cleared with the assertion of RST. PLC\_CNTRL\_B contains signals and requests to direct the process of physical connection

management. It is also used to control the Line State Match interrupt.

The PLC\_CNTRL\_B register bit assignments are listed in Table 3.

Table 3. PLC\_CNTRL\_B

| Bit   | Name                                                                                                                                                                                         | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| 15    | CONFIG_CNTRL                                                                                                                                                                                 | The CONFIG_CNTRL bit allows control over the Scrub, Bypass, and Remote Loopback datapath MUXes while the PCM is in normal operation. If this bit is set, then the REQ_SCRUB, SC_BYPASS, and SC_REM_LOOP bits in the PLC_CNTRL_A register will have effect regardless of the state of the PCM. If this bit is not set then the REQ_SCRUB, SC_BYPASS and SC_REM_LOOP bits will only have effect if the PCM is in the MAINT state.                                                                                                                     |                                                                                     |  |

| 14–11 | MATCH_LS                                                                                                                                                                                     | The MATCH_LS field specifies line states to be compared with the currently detected line state (as defined by LINE_ST in the PLC_STATUS_A register). When a match occurs, the LS_MATCH interrupt bit in the INTR_EVENT register is asserted. Each bit of MATCH_LS corresponds to a line state. If more than one bit is set, the interrupt is signalled if any of the line states match the current line state. If no bits are set, the interrupt is signalled on any change in the LINE_ST field or the UNKN_LINE_ST bit. It is defined as follows: |                                                                                     |  |

|       |                                                                                                                                                                                              | MATCH_LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                         |  |

|       |                                                                                                                                                                                              | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interrupt on any change in LINE_ST or UNKN_LINE_ST                                  |  |

|       |                                                                                                                                                                                              | 1XXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interrupt on Quiet Line State                                                       |  |

|       |                                                                                                                                                                                              | X1XX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interrupt on Master Line State                                                      |  |

|       |                                                                                                                                                                                              | XX1X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interrupt on Halt Line State                                                        |  |

|       |                                                                                                                                                                                              | XXX1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interrupt on Idle Line State                                                        |  |

|       |                                                                                                                                                                                              | In the above table, "X" means don't care. Also Idle Line State refers to ILS16, which is signalled only after sixteen Idle symbols (eight Idle bytes) have been received.                                                                                                                                                                                                                                                                                                                                                                           |                                                                                     |  |

| 10–8  | The MAINT_LS field defines the line state the PCM will source while in the state. The PCM enters the MAINT state from the OFF state if the PC_M/ asserted. It is further defined as follows: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rs the MAINT state from the OFF state if the PC_MAINT bit is                        |  |

|       |                                                                                                                                                                                              | MAINT_LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                         |  |

|       |                                                                                                                                                                                              | 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Transmit QUIET Line State                                                           |  |

|       |                                                                                                                                                                                              | 001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Transmit IDLE Line State                                                            |  |

|       |                                                                                                                                                                                              | 010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Transmit HALT Line State                                                            |  |

|       |                                                                                                                                                                                              | 011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Transmit MASTER Line State                                                          |  |

|       |                                                                                                                                                                                              | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Transmit QUIET Line State                                                           |  |

|       |                                                                                                                                                                                              | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Transmit QUIET Line State                                                           |  |