### **Brief Description**

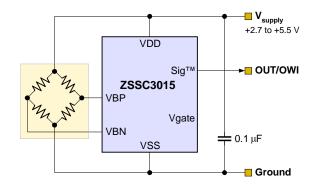

The ZSSC3015 sensor signal conditioner IC is adjustable to nearly all piezo-resistive bridge sensors. Measured and corrected bridge values are provided at the Sig<sup>™</sup> pin, which can be configured as an analog voltage output or as a one-wire serial digital output.

The ZACwire™ digital one-wire interface (OWI) can be used for a simple PC-controlled calibration procedure to program a set of calibration coefficients into an on-chip EEPROM. The calibrated ZSSC3015 and a specific sensor are mated digitally: fast, precise, and without the cost overhead associated with trimming by external devices or laser. Integrated diagnostics functions make the ZSSC3015 particularly well suited for automotive applications.

#### **Features**

- Digital compensation of sensor offset, sensitivity, temperature drift, and nonlinearity

- Programmable analog gain and digital gain; accommodates bridges with spans < 1mV/V and high offset

- Many diagnostic features on chip (e.g., EEPROM signature, bridge connection checks, bridge short detection, power loss detection)

- Independently programmable high and low clipping levels

- · 24-bit customer ID field for module traceability

- Internal temperature compensation reference (no external components)

- Option for external temperature compensation with addition of single diode

- Output options: rail-to-rail ratiometric analog voltage (12-bit resolution), absolute analog voltage, ZACwire™ digital one-wire interface

- Fast power-up to data out response; output available 5ms after power-up

- Current consumption depends on programmed sample rate and mode: 1mA down to 300µA (typ.)

- Fast response time: 1.4ms typical

- High voltage protection: ≤ 30V with external JFET

- AEC-Q100 qualified

#### **Benefits**

- · No external trimming components required

- PC-controlled configuration and calibration via ZACwire™ one-wire interface – simple, low cost

- High accuracy (as high as ±0.1% FSO @ -25 to 85°C; ±0.25% FSO @ -50 to 150°C)

- Single-pass calibration quick and precise

# Available Support

- · Evaluation Kit available

- Mass Calibration System available

- Support for industrial mass calibration available

- Quick circuit customization possible for large production volumes

## **Physical Characteristics**

- Wide operation temperature: -50°C to +150°C

- Supply voltage 2.7 to 5.5V; with external JFET, 5.5 to 30V

- Small SOP8 package

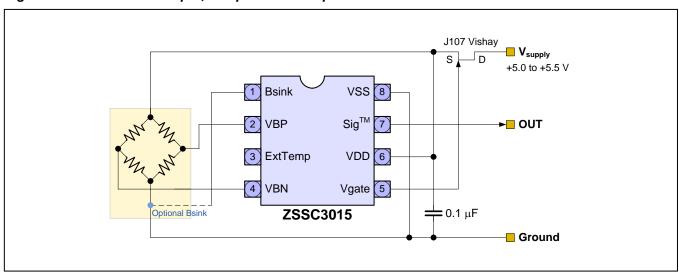

#### ZSSC3015 Application Circuit

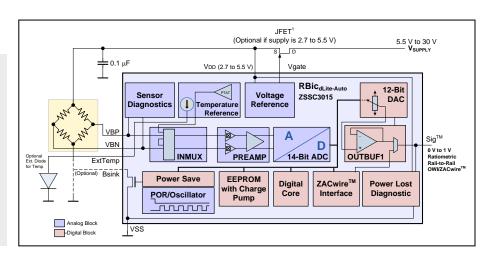

# **ZSSC3015 Block Diagram**

Highly Versatile Applications in Many Markets Including

- · Industrial

- Building Automation

- Office Automation

- White Goods

- Automotive

- Portable Devices

- Your Innovative Designs

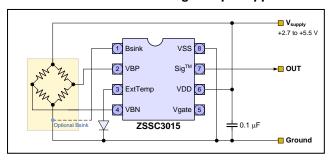

#### Rail-to-Rail Ratiometric Voltage Output Applications

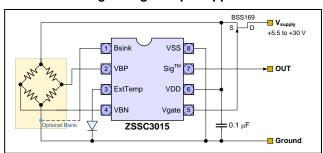

#### Absolute Analog Voltage Output Applications

#### Part Ordering Examples (See section 11 in the data sheet for additional options.)

| Sales Code      | Description                                                                                                                                                          | Package                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| ZSSC3015NE1B    | ZSSC3015 Die — Temperature range: -50°C to +150°C                                                                                                                    | Unsawn on Wafer                              |

| ZSSC3015NE1C    | ZSSC3015 Die — Temperature range: -50°C to +150°C                                                                                                                    | Sawn on Wafer Frame                          |

| ZSSC3015NE2T(R) | ZSSC3015 SOP8 (150 mil) — Temperature range: -50°C to +150°C                                                                                                         | Tube: add "-T" to sales code. Reel: add "-R" |

| ZSSC3015KIT     | ZSSC3015 SSC Evaluation Kit: Communication Board, SSC Board, Sensor Replacement Board, USB cable, 5 IC samples, instructions for downloading SSC Evaluation Software | Kit                                          |

#### **Corporate Headquarters**

6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com

#### Sales

1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales

#### **Tech Support**

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <a href="www.idt.com/qo/qlossary">www.idt.com/qo/qlossary</a>. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.

# **Contents**

| List of Fig | gures                                     | 4  |

|-------------|-------------------------------------------|----|

| List of Ta  | ables                                     | 5  |

|             | trical Characteristics                    |    |

| 1.1.        | Absolute Maximum Ratings                  | 6  |

| 1.2.        | Recommended Operating Conditions          | 6  |

| 1.3.        | Electrical Parameters                     | 7  |

| 1.4.        | Analog Inputs versus Output Resolution    | 9  |

| 2 Circu     | uit Description                           | 11 |

| 2.1.        | Signal Flow and Block Diagram             | 11 |

| 2.2.        | Analog Front End                          | 12 |

| 2.2.1       | 1. Bandgap/PTAT and PTAT Amplifier        | 12 |

| 2.2.2       | 9 11 7                                    |    |

| 2.2.3       |                                           |    |

| 2.2.4       | · · · · · · · · · · · · · · · · · · ·     |    |

| 2.3.        | Digital Signal Processor                  |    |

| 2.3.1       |                                           |    |

| 2.3.2       |                                           |    |

|             | Output Stage                              |    |

| 2.4.1       | 3 ( - 1                                   |    |

| 2.4.2       |                                           |    |

| 2.4.3       |                                           |    |

|             | Clock Generator / Power-On Reset (CLKPOR) |    |

|             | Diagnostic Features                       |    |

| 2.6.1       | <b>5</b> ,                                |    |

| 2.6.2       |                                           |    |

| 2.6.3       |                                           |    |

| 2.6.4       |                                           |    |

| 2.6.5       | '                                         |    |

|             | ctional Description                       |    |

|             | General Working Mode                      |    |

|             | Normal Mode Sample Rate                   |    |

|             | ZACwire™ Communication Interface          |    |

|             | 1. Properties and Parameters              |    |

| 3.3.2       | <u> </u>                                  |    |

| 3.3.3       | •                                         |    |

| 3.3.4       | ·                                         |    |

| 3.3.5       | · ·                                       |    |

|             | Command/Data Bytes Encoding               |    |

|             | Calibration Sequence                      |    |

| 3.6.        | EEPROM Bits                               | 31 |

| 3.7. Cal      | libration Math                                                                             | 34 |

|---------------|--------------------------------------------------------------------------------------------|----|

| 3.7.1.        | Correction Coefficients                                                                    | 34 |

| 3.7.2.        | Interpretation of Binary Numbers for Correction Coefficients                               | 35 |

| 3.8. Rea      | ading EEPROM Contents                                                                      | 38 |

| 4 Applicat    | tion Circuit Examples                                                                      | 39 |

| 4.1. Thr      | ee-Wire Rail-to-Rail Ratiometric Output                                                    | 39 |

| 4.2. Abs      | solute Analog Voltage Output                                                               | 40 |

| 4.3. Thr      | ree-Wire Ratiometric Output with Over-Voltage Protection                                   | 41 |

| 4.4. Dig      | ital Output                                                                                | 41 |

| 4.5. Out      | tput Resistor/Capacitor Limits                                                             | 41 |

| 5 EEPRO       | DM Restoration                                                                             | 42 |

|               | fault EEPROM Contents                                                                      |    |

| 5.1.1.        | 1V_Trim/JFET_Trim                                                                          | 42 |

| 5.2. EEI      | PROM Restoration Procedure                                                                 | 42 |

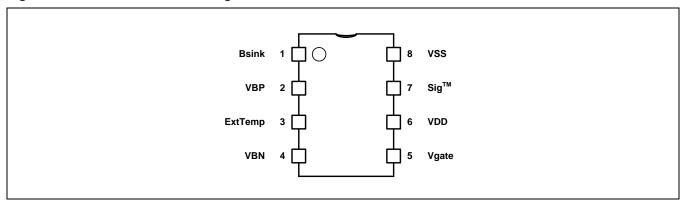

| 6 Pin Con     | nfiguration and Package                                                                    | 44 |

| 7 ESD/La      | atch-Up-Protection                                                                         | 45 |

| 8 Test        | ······································                                                     | 45 |

| 9 Quality     | and Reliability                                                                            | 45 |

| 10 Custom     | ization                                                                                    | 45 |

| 11 Orderin    | g Sales Codes                                                                              | 46 |

| 12 Related    | I Documents                                                                                | 46 |

| 13 Definition | ons of Acronyms                                                                            | 47 |

| 14 Docume     | ent Revision History                                                                       | 48 |

|               |                                                                                            |    |

|               |                                                                                            |    |

| List of       | Figures                                                                                    |    |

| Figure 2.1    | ZSSC3015 Block Diagram                                                                     | 11 |

| Figure 2.2    | DAC Output Timing for Highest Update Rate                                                  |    |

| Figure 3.1    | General Working Mode                                                                       |    |

| Figure 3.2    | Manchester Duty Cycle                                                                      |    |

| Figure 3.3    | 19-Bit Write Frame                                                                         |    |

| Figure 3.4    | Read Acknowledge                                                                           |    |

| Figure 3.5    | Digital Output (NOM) Bridge Readings                                                       |    |

| Figure 3.6    | Digital Output (NOM) Bridge Readings with Temperature                                      |    |

| Figure 3.7    | Read EEPROM Contents                                                                       |    |

| Figure 3.8    | Transmission of a Number of Data Packets                                                   |    |

| Figure 3.9    | ZACwire™ Output Timing for Lower Update Rates                                              |    |

| Figure 4.1    | Rail-to-Rail Ratiometric Voltage Output – Temperature Compensation via External Diode      |    |

| Figure 4.2    | Absolute Analog Voltage Output – Temperature Compensation via External Diode with External |    |

| -             | JFET Regulation                                                                            |    |

| Figure 4.3    | Ratiometric Output, Temperature Compensation via Internal PTAT                             | 41 |

| Figure 5.1    | EEPROM Validation and Restoration Procedure                                                | 43 |

| Figure 6.1 | ZSSC3015 Pin-Out Diagram                                                    | 44 |

|------------|-----------------------------------------------------------------------------|----|

| List of    | Tables                                                                      |    |

| Table 1.1  | ADC Resolution Characteristics for an Analog Gain of 6                      | g  |

| Table 1.2  | ADC Resolution Characteristics for an Analog Gain of 24                     |    |

| Table 1.3  | ADC Resolution Characteristics for an Analog Gain of 48                     |    |

| Table 1.4  | ADC Resolution Characteristics for an Analog Gain of 96                     |    |

| Table 2.1  | 1V Reference Trim (1V vs. Trim for Nominal Process Run)                     | 17 |

| Table 2.2  | Summary of Diagnostic Features                                              | 18 |

| Table 3.1  | Update Rate for Analog Output                                               | 22 |

| Table 3.2  | ZACwire™ Parameters                                                         | 23 |

| Table 3.3  | Idle Time between Packets versus Update Rate                                | 26 |

| Table 3.4  | Total Transmission Time for Different Update Rate and Output Configurations | 27 |

| Table 3.5  | Command/Data Bytes Encoding                                                 | 28 |

| Table 3.6  | ZSSC3015 EEPROM Bits                                                        | 31 |

| Table 3.7  | Correction Coefficients                                                     | 34 |

| Table 3.8  | Gain_B [13:0] Weightings                                                    | 35 |

| Table 3.9  | Offset_B Weightings                                                         |    |

| Table 3.10 | Gain_T Weightings                                                           | 36 |

| Table 3.11 | Offset_T Weightings                                                         | 37 |

| Table 3.12 | EEPROM Read Order                                                           |    |

| Table 6.1  | ZSSC3015 Pin Configuration                                                  | 44 |

# 1 Electrical Characteristics

# 1.1. Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. The ZSSC3015 might not function or be operable above the recommended operating conditions. Stresses exceeding the absolute maximum ratings might also damage the device. In addition, extended exposure to stresses above the recommended operating conditions might affect device reliability. IDT does not recommend designing to the "Absolute Maximum Ratings."

| Parameter                                                  | Symbol                    | Min   | Max     | Unit |

|------------------------------------------------------------|---------------------------|-------|---------|------|

| Analog Supply Voltage                                      | $V_{DD}$                  | -0.3  | 6.0     | V    |

| Voltages at Analog I/O – In Pin                            | V <sub>INA</sub>          | -0.3  | VDD+0.3 | V    |

| Voltages at Analog I/O – Out Pin                           | V <sub>OUTA</sub>         | -0.3  | VDD+0.3 | V    |

| Electrostatic Discharge – Human Body Model (see section 7) |                           | ±4000 |         | V    |

| Storage Temperature Range (≥10 hours)                      | T <sub>STOR</sub>         | -50   | 150     | °C   |

| Storage Temperature Range (<10 hours)                      | T <sub>STOR &lt;10h</sub> | -50   | 170     | °C   |

# 1.2. Recommended Operating Conditions

| Parameter                                                       | Symbol             | Min | Тур | Max                    | Unit |

|-----------------------------------------------------------------|--------------------|-----|-----|------------------------|------|

| Analog Supply Voltage to Ground                                 | $V_{DD}$           | 2.7 | 5.0 | 5.5                    | V    |

| Analog Supply Voltage (with external JFET Regulator)            | V <sub>SUPP</sub>  | 5.5 | 7   | 30                     | V    |

| Common Mode Voltage                                             | V <sub>CM</sub>    | 1   |     | V <sub>DDA</sub> – 1.3 | V    |

| Ambient Temperature Range 1), 2)                                | T <sub>AMB</sub>   | -50 |     | 150                    | °C   |

| External Capacitance between V <sub>DD</sub> and Ground         | C <sub>VDD</sub>   | 100 | 220 | 470                    | nF   |

| Output Load Resistance to V <sub>SS</sub> or V <sub>DD</sub> 3) | R <sub>L,OUT</sub> | 5   |     |                        | kΩ   |

| Output Load Capacitance 4)                                      | C <sub>L,OUT</sub> |     | 10  | 15                     | nF   |

| Bridge Resistance 5), 6)                                        | R <sub>BR</sub>    | 0.3 |     | 100                    | kΩ   |

| Power-On Rise Time                                              | t <sub>PON</sub>   |     |     | 100                    | ms   |

$<sup>^{\</sup>rm 1)}\,$  Note that the maximum EEPROM programming temperature is 85°C.

<sup>&</sup>lt;sup>2)</sup> If buying die, designers should use caution not to exceed maximum junction temperature by proper package selection.

<sup>3)</sup> Only needed for Analog Output Mode; not needed for Digital Output Mode. When a pull-down resistor is used as load resistor, the power loss detection diagnostic for loss of VSS cannot be assured at RL=5k; RL=10k is recommended for this configuration.

<sup>&</sup>lt;sup>4)</sup> Using the output for digital calibration, CL,OUT is limited by the maximum rise time tZAC,rise. See section 1.3.

<sup>&</sup>lt;sup>5)</sup> Note: Minimum bridge resistance is only a factor if using the Bsink feature. The RDS(ON) of the Bsink transistor is 8 to 10Ω when operating at VDD=5V. This gives rise to a ratiometricity inaccuracy that becomes greater with low bridge resistances.

Note: Minimum bridge resistance is important if using certain diagnostic features. It must be at least 0.3kΩ at V<sub>DD</sub>=2.7V and at least 0.6kΩ at V<sub>DD</sub>=5V for the Sensor Short Check to function properly. For details, see section 2.6.3.

# 1.3. Electrical Parameters

Note: See important table notes at end of table. For parameters marked with an asterisk \* there is no verification in mass production; the parameter is guaranteed by design and/or quality observation.

| Parameter                                | Symbol                | Conditions                                                                                                                         | Min  | Тур | Max    | Unit                 |

|------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------|----------------------|

| Supply Voltage                           | $V_{DD}$              |                                                                                                                                    | 2.7  | 5.0 | 5.5    | V                    |

| Supply Current (varies with              |                       | At slowest update rate                                                                                                             |      | 0.3 |        |                      |

| update rate and output mode)             | I <sub>DD</sub>       | At fastest update rate                                                                                                             |      | 1.0 | 1.4    | mA                   |

| Temperature Coefficient –<br>PTAT Source | T <sub>CPTAT</sub>    |                                                                                                                                    |      | 20  | 100    | ppm/K                |

| Power Supply Rejection Ratio*            | PSRR                  |                                                                                                                                    | 60   |     |        | dB                   |

| Power-On Reset Level                     | POR                   |                                                                                                                                    | 1.4  |     | 2.6    | V                    |

| EEPROM                                   |                       |                                                                                                                                    |      |     |        |                      |

| Number Write Cycles                      | n <sub>wri_eep</sub>  | At 85°C                                                                                                                            |      |     | 100k   | Cycles               |

| Data Retention                           | t <sub>WRI_EEP</sub>  | At 100°C                                                                                                                           |      |     | 10     | Years                |

| Analog Front-End (AFE)                   |                       |                                                                                                                                    |      |     |        |                      |

| Leakage Current—Pins VBP and VBN         | I <sub>IN_LEAK</sub>  | Sensor connection and short check must be disabled. See sections 2.6.2 and 2.6.3.                                                  |      |     | ±10    | nA                   |

| Analog-to-Digital Converter (A           | DC)                   |                                                                                                                                    |      |     |        |                      |

| ADC Resolution                           | r <sub>ADC</sub>      |                                                                                                                                    |      |     | 14     | Bit                  |

| Integral Nonlinearity (INL) 1)           | INL <sub>ADC</sub>    | Based on ideal slope.                                                                                                              |      |     | ±8     | LSB                  |

| Differential Nonlinearity (DNL)*         | DNL <sub>ADC</sub>    |                                                                                                                                    |      |     | ±1     | LSB                  |

| Digital-to-Analog Converter (D           | AC) and Bu            | iffer for Analog Output                                                                                                            |      |     |        |                      |

| Maximum Output Current                   | I <sub>OUT</sub>      | Maximum current maintaining accuracy.                                                                                              | 2.2  |     |        | mA                   |

| Resolution                               | Res                   | Referenced to V <sub>DD</sub> .                                                                                                    |      |     | 12     | Bit                  |

| Absolute Error                           | E <sub>ABS</sub>      | DAC input to output.                                                                                                               |      |     | ±0.2%  | $V_{DD}$             |

| Differential Nonlinearity *              | DNL                   | No missing codes.                                                                                                                  | -0.9 |     | +3.0   | LSB <sub>12Bit</sub> |

| Upper Output Voltage Limit               | $V_{OUT}$             | $R_L = 5 \text{ k}\Omega.$                                                                                                         | 95%  |     |        | $V_{DD}$             |

| Lower Output Voltage Limit               | Vout                  | With $5k\Omega$ pull down, 0-1V output.                                                                                            |      |     | 16.5mV | mV                   |

| Output Short Circuit<br>Protection Limit | Isc                   | Depends on operating conditions. Short circuit protection must be enabled via Diag_cfg (EEPROM word [102:100]). See section 2.4.2. | 3    |     | 20     | mA                   |

| Analog Output Noise<br>Peak-to-Peak      | V <sub>NOISE,PP</sub> | Shorted input.                                                                                                                     |      |     | 5±1LSB | mV                   |

| Parameter                                        | Symbol                | Conditions                                               | Min   | Тур | Max  | Unit     |

|--------------------------------------------------|-----------------------|----------------------------------------------------------|-------|-----|------|----------|

| Diagnostics                                      |                       |                                                          |       |     |      |          |

| Upper Diagnostic Output Level                    | $V_{DIA,H}$           |                                                          | 97.5% |     |      | $V_{DD}$ |

| Lower Diagnostic Output Level                    | $V_{DIA,L}$           |                                                          |       |     | 2.5% | $V_{DD}$ |

| Minimum Load Resistor for<br>Power Loss          | R <sub>L,OUT_PS</sub> | Pull-up or pull-down <sup>2)</sup> in Analog Output Mode | 5     |     |      | kΩ       |

| External Temperature Measure                     | ement                 |                                                          |       |     |      |          |

| ExtTemp Signal Input Range                       | $V_{TSE}$             |                                                          | 150   |     | 800  | mV       |

| Required External Temperature Diode Sensitivity  | ST <sub>TSE</sub>     |                                                          | 1.9   |     | 3.25 | mV/K     |

| Temperature Span with External Temperature Diode | T <sub>TSE_SP</sub>   |                                                          | -50   |     | 150  | °C       |

| 7∆Cwire™ Serial Interface                        |                       |                                                          | •     | •   |      |          |

#### ZACwire™ Serial Interface

See section 3.3.1 for specifications related to the ZACwire™ serial interface.

| System Response                                      |                       |                                  |      |       |        |       |

|------------------------------------------------------|-----------------------|----------------------------------|------|-------|--------|-------|

| Start-Up Time (Power-up to data output)              | t <sub>STA</sub>      | Fast Startup                     | 6    |       | 8      | ms    |

| Response Time – Analog<br>Output                     | t <sub>RESP-A</sub>   | Update_rate = 0                  | 0.88 | 1.4   | 3.2    | ms    |

| Response and Transmission<br>Time for Digital Output | t <sub>RES, DIG</sub> | Update_rate = 0                  | 1.7  | 2.75  | 5.5    | ms    |

| Overall Linearity Error– Digital                     | E <sub>LIND</sub>     | Bridge input to output           |      | 0.025 | 0.04   | %     |

| Overall Linearity Error – Analog                     | E <sub>LINA</sub>     | Bridge input to output           |      | 0.1   | 0.2    | %     |

| Overall Ratiometricity Error                         | RE <sub>out</sub>     | ±10%VDD; not using Bsink feature |      | 0.025 | 0.1    | %     |

| Overall Accuracy – Digital                           | 4.0                   | -25°C to 85°C                    |      |       | ±0.1%  | %FSO  |

| (only IC, without sensor bridge)                     | $AC_{outD}$           | -50°C to 150°C                   |      |       | ±0.25% | %F3U  |

| Overall Accuracy – Analog 3), 4)                     |                       | -25°C to 85°C                    |      |       | ±0.35% | 0/500 |

| (only IC, without sensor bridge)                     | $AC_{outA}$           | -50°C to 150°C                   |      |       | ±0.5%  | %FSO  |

<sup>1)</sup> Note: This is  $\pm$  8 LSBs for the 14-bit analog-to-digital conversion. This results in absolute accuracy to 11-bits on the conversion result. Nonlinearity is typically better at temperatures less than 125°C.

<sup>2)</sup> When using a pull-down resistor as load resistor, the power loss detection diagnostic for loss of VSS cannot be assured at RL=5k; RL=10k is recommended for this configuration.

Not included is the quantization noise of the DAC. The 12-bit DAC has a quantization noise of  $\pm \frac{1}{2}$  LSB = 0.61mV (@ 5V VDD) = 0.0125%.

<sup>4)</sup> Analog output range 2.5% to 95%.

## 1.4. Analog Inputs versus Output Resolution

The ZSSC3015 has a fully differential chopper-stabilized pre-amplifier with 4 programmable gain settings. The output of the pre-amplifier is input to a 14-bit charge-balanced ADC. Span, offset, temperature, and nonlinearity correction are performed in the digital domain. Then the resulting corrected bridge value can be output in analog form through a 12-bit DAC or as a 16-bit serial digital packet. The resolution of the output depends on the input span (bridge sensitivity) and the analog gain setting programmed. Digital gains can vary from [0,32). Analog gains available are 6, 24, 48, and 96.

Note: At higher analog gain settings, there will be higher output resolution, but the ability of the ZSSC3015 to handle large offsets decreases. This is expected because the offset is also amplified by the analog gain and can therefore saturate the ADC input.

The following tables outline the guaranteed minimum resolution for a given bridge sensitivity range.

Table 1.1 ADC Resolution Characteristics for an Analog Gain of 6

| Analog Gain 6               |      |                                  |                              |                    |  |  |

|-----------------------------|------|----------------------------------|------------------------------|--------------------|--|--|

| Input Span [mV/V]           |      | Input Span [mV/V] Allowed Offset |                              | Minimum Guaranteed |  |  |

| Min                         | Тур  | Max                              | (+/- % of Span) <sup>1</sup> | Resolution [Bits]  |  |  |

| 57.8                        | 80.0 | 105.8                            | 38%                          | 12.4               |  |  |

| 50.6                        | 70.0 | 92.6                             | 53%                          | 12.2               |  |  |

| 43.4                        | 60.0 | 79.4                             | 73%                          | 12.0               |  |  |

| 36.1                        | 50.0 | 66.1                             | 101%                         | 11.7               |  |  |

| 28.9                        | 40.0 | 52.9                             | 142%                         | 11.4               |  |  |

| 21.7                        | 30.0 | 39.7                             | 212%                         | 11.4               |  |  |

| 1) In addition to Tco, Tcg. |      |                                  |                              |                    |  |  |

Table 1.2 ADC Resolution Characteristics for an Analog Gain of 24

|                     |          | Analo | g Gain 24                                                                              |                    |

|---------------------|----------|-------|----------------------------------------------------------------------------------------|--------------------|

| Input Span [mV/V]   |          |       | Allowed Offset                                                                         | Minimum Guaranteed |

| Min                 | Тур      | Max   | (+/- % of Span) <sup>1</sup>                                                           | Resolution [Bits]  |

| 18.1                | 25.0     | 33.1  | 17%                                                                                    | 12.7               |

| 14.5                | 20.0     | 26.5  | 38%                                                                                    | 12.4               |

| 7.2                 | 10.0     | 13.2  | 142%                                                                                   | 11.4               |

| 3.6                 | 5.0      | 6.6   | 351%                                                                                   | 10.4               |

| 1.8                 | 2.5      | 3.3   | 767%                                                                                   | 9.4                |

| 0.9                 | 1.2      | 1.6   | 1670%                                                                                  | 8.4                |

| 1) In addition to T | co, Tcg. |       | low shadowed fields indicate that for the pain setting, the quantization noise is high |                    |

<sup>© 2016</sup> Integrated Device Technology, Inc.

Table 1.3 ADC Resolution Characteristics for an Analog Gain of 48

| Analog Gain 48                                                                                                                                                                                  |                   |      |                              |                    |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------------------------------|--------------------|--|--|

|                                                                                                                                                                                                 | Input Span [mV/V] |      | Allowed Offset               | Minimum Guaranteed |  |  |

| Min                                                                                                                                                                                             | Тур               | Max  | (+/- % of Span) <sup>1</sup> | Resolution [Bits]  |  |  |

| 10.8                                                                                                                                                                                            | 15.0              | 19.8 | 3%                           | 13.0               |  |  |

| 7.2                                                                                                                                                                                             | 10.0              | 13.2 | 38%                          | 12.4               |  |  |

| 4.3                                                                                                                                                                                             | 6.0               | 7.9  | 107%                         | 11.7               |  |  |

| 2.9                                                                                                                                                                                             | 4.0               | 5.3  | 194%                         | 11.1               |  |  |

| 1.8                                                                                                                                                                                             | 2.5               | 3.3  | 351%                         | 10.4               |  |  |

| 1.0                                                                                                                                                                                             | 1.4               | 1.85 | 678%                         | 9.6                |  |  |

| 0.72                                                                                                                                                                                            | 1.0               | 1.32 | 976%                         | 9.1                |  |  |

| In addition to Tco, Tcg.  Important Note: The yellow shadowed fields indicate that for these input spans with the selected analog gain setting, the quantization noise is higher than 0.1% FSO. |                   |      |                              |                    |  |  |

Table 1.4 ADC Resolution Characteristics for an Analog Gain of 96

| Analog Gain 96    |     |      |                              |                    |  |  |  |

|-------------------|-----|------|------------------------------|--------------------|--|--|--|

| Input Span [mV/V] |     |      | Allowed Offset               | Minimum Guaranteed |  |  |  |

| Min               | Тур | Max  | (+/- % of Span) <sup>1</sup> | Resolution [Bits]  |  |  |  |

| 4.3               | 6.0 | 7.9  | 21%                          | 12.7               |  |  |  |

| 2.9               | 4.0 | 5.3  | 64%                          | 12.1               |  |  |  |

| 1.8               | 2.5 | 3.3  | 142%                         | 11.4               |  |  |  |

| 1.0               | 1.4 | 1.85 | 306%                         | 10.6               |  |  |  |

| 0.72              | 1.0 | 1.32 | 455%                         | 10.1               |  |  |  |

# 2 Circuit Description

# 2.1. Signal Flow and Block Diagram

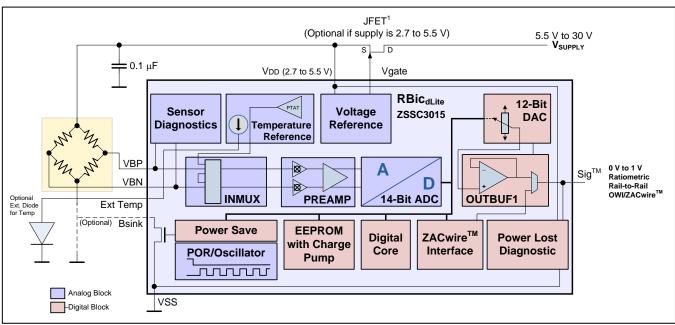

The ZSSC3015 resistive bridge sensor interface ICs were specifically designed as cost-effective solutions for sensing in building automation, automotive, industrial, office automation, and white goods applications. The ZSSC3015 employs IDT's high precision bandgap with proportional-to-absolute-temperature (PTAT) output; low-power 14-bit analog-to-digital converter (ADC, A2D, A-to-D); and an on-chip digital signal processor (DSP) core with EEPROM to precisely calibrate the bridge output signal.

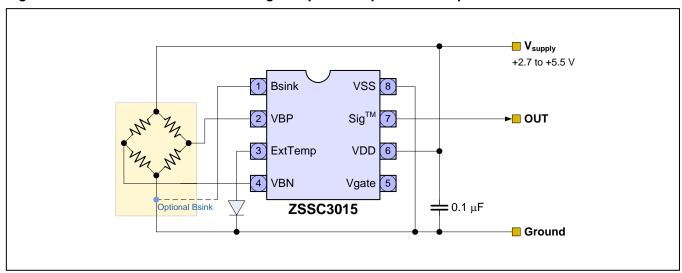

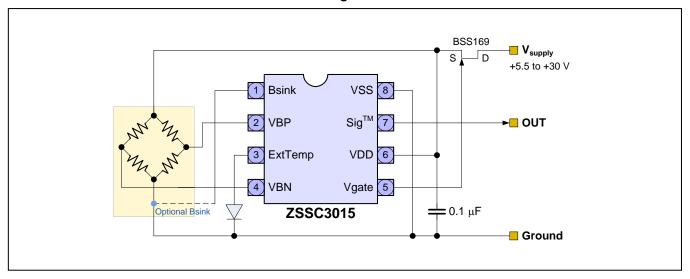

Three selectable outputs, two analog and one digital, offer the ultimate in versatility across many applications. The ZSSC3015 rail-to-rail ratiometric analog  $V_{out}$  signal (0V to ~5 V  $V_{out}$  @  $V_{DD}$ =5V) suits most building automation and automotive requirements (12-bit resolution). Typical office automation and white goods applications require the 0 to ~1V  $V_{out}$  signal, which in the ZSSC3015 is referenced to the internal bandgap. The ZSSC3015 is capable of running in high-voltage (5.5 to 30 V) systems when combined with an external JFET.

Direct interfacing to μP controllers is facilitated via IDT's single-wire serial ZACwire™ digital interface.

Figure 2.1 ZSSC3015 Block Diagram

# 2.2. Analog Front End

## 2.2.1. Bandgap/PTAT and PTAT Amplifier

The highly linear Bandgap/PTAT section provides the PTAT signal to the ADC, which allows accurate temperature conversion. In addition, the ultra-low ppm Bandgap section provides a stable voltage reference over temperature for the operation of the rest of the ZSSC3015. If the bridge is not near the ZSSC3015, an external diode can be used for temperature measurement/compensation.

The temperature signal (internal PTAT or external diode) is amplified through a path in the PREAMP block and fed to the ADC for conversion. The most significant 12-bits of this converted result are used for temperature measurement and temperature correction of bridge readings. When temperature is output in Digital Mode, only the most significant 8 bits are given.

When external temperature is selected, add a diode from the ExtTemp pin to ground. The diode is biased with approximately 50µA during temperature measurement cycles. The voltage level on ExtTemp is amplified through the PREAMP section and converted by the ADC. Ensure that the ExtTemp signal is in the range of 150mV to 800mV to prevent saturation of the ADC. If the selected diode has a sensitivity in the range of 1.9mV/°C to 3.25mV/°C, a corrected temperature output (in Digital Mode) can be achieved for a 200°C temperature span (-50°C to 150°C).

## 2.2.2. Bridge Supply

The voltage-driven bridge is usually connected to  $V_{DD}$  and ground. As a power savings feature, the ZSSC3015 also includes a switched transistor to interrupt the bridge current via pin 1 (Bsink). The transistor switching is synchronized to the analog-to-digital conversion and released after finishing the conversion. To utilize this feature, the low supply of the bridge should be connected to Bsink instead of ground.

Depending on the programmable update rate, the average current consumption (including bridge current) can be reduced to approximately 20%, 5%, or 1%. Note this feature has no power savings benefit if using the fastest update rate mode.

#### 2.2.3. PREAMP Block

The differential signal from the bridge is amplified through a chopper-stabilized instrumentation amplifier with very high input impedance designed for low noise and low drift. This pre-amp provides gain for the differential signal and re-centers its DC to V<sub>DD</sub>/2. The output of the PREAMP section is fed into the ADC. The calibration sequence performed by the digital core includes an auto-zero sequence to null any drift in the pre-amp state over temperature.

The pre-amp can be set to a gain of 6, 24, 48, or 96 through EEPROM. See Pamp\_Gain in section 3.6.

The inputs to the pre-amp from (VBN/VBP pins) can be reversed via an EEPROM configuration bit. See "flip polarity" under A2D\_Offset in section 3.6.

## 2.2.4. Analog-to-Digital Converter (ADC)

A 14-bit 2<sup>nd</sup> order charge-balancing ADC is used to convert signals coming from the pre-amplifier. The converter, designed in full differential switched capacitor technique, is used for converting the various signals in the digital domain.

This principle offers the following advantages:

- High noise immunity because of the differential signal path and integrating behavior

- Independence from clock frequency drift and clock jitter

- Fast conversion time due to second order mode

Parameters of the ADC can be controlled with EEPROM settings given in section 3.6.

Four selectable values for the zero point of the input voltage allow conversion to adapt to the sensor's offset parameter. With the Flip Polarity Mode and the negative digital gain options, this results in seven possible zero point adjustments (not eight because the -1/2,1/2 offset setting is the same regardless of gain polarity).

The conversion rate varies with the programmed update rate. The fastest conversation rate is 1k samples/s. Based on a best fit, the integral nonlinearity (INL) is less than  $4 LSB_{14Bit}$ .

## 2.3. Digital Signal Processor

A digital signal processor (DSP) is used for processing the converted bridge data as well as performing temperature correction and computing the temperature value for output on the digital channel.

The digital core reads correction coefficients from EEPROM and can correct for the following:

- · Bridge Offset

- Bridge Gain

- Variation of Bridge Offset over Temperature (Tco)

- Variation of Bridge Gain over Temperature (Tcg)

- A single second-order effect (SOT) (Second Order Term)

The EEPROM contains a single SOT that can be applied to correct one and only one of the following:

- 2<sup>nd</sup> order behavior of bridge measurement

- 2<sup>nd</sup> order behavior of Tco

- 2<sup>nd</sup> order behavior of Tcg

If the SOT applies to correcting the bridge reading, then the correction formula for the bridge reading is represented as a two-step process as follows:

$$ZB = Gain \_B(1 + \Delta T * Tcg) * (BR \_Raw - / + Offset \_B + \Delta T * Tco)$$

(1)

$$RB = ZB(1.25 + SOT * ZB) \tag{2}$$

Where:

BR = Corrected Bridge reading that is output as digital or analog on Sig<sup>™</sup> pin

**ZB** = Intermediate result in the calculations

**BR\_Raw** = Raw Bridge reading from ADC

**T\_Raw** = Raw Temp reading converted from PTAT signal or external diode

Gain\_B = Bridge Gain term

Offset\_B = Bridge Offset term

Offset\_B\_sign = Sign bit for Bridge Offset term

Tcg = Temperature Coefficient Gain

Tco = Temperature Coefficient Offset

$\Delta T = (T_Raw - T_{SETL})$

T<sub>SETL</sub> = T\_Raw reading at which low calibration was performed (typically 25°C)

SOT = Second Order Term

If the **SOT** applies to correcting the 2<sup>nd</sup> order behavior of **Tco**, then the formula for bridge correction is as follows:

$$BR = Gain\_B(1 + \Delta T * Tcg) * [BR\_Raw - / + Offset\_B + \Delta T(SOT * \Delta T + Tco)]$$

(3)

If the **SOT** applies to correcting the 2<sup>nd</sup> order behavior of Tcg, then the formula for bridge correction is as follows:

$$BR = Gain\_B[1 + \Delta T(SOT * \Delta T + Tcg)] * [BR\_Raw - / + Offset\_B + \Delta T * Tco]$$

(4)

The bandgap reference gives a very linear PTAT signal, so temperature correction can always simply be accomplished with a linear gain and offset term.

Corrected Temperature Reading:

$$T = Gain_T(T_Raw + Offset_T)$$

(5)

Where:

**T\_Raw** = Raw Temperature reading converted from PTAT signal or external diode

Offset\_T = Offset Coefficient for Temperature

Gain\_T = Gain Coefficient for Temperature

#### 2.3.1. **EEPROM**

The EEPROM contains the calibration coefficients for gain and offset, etc., and the configuration bits, such as output mode, update rate, etc. The ZSSC3015 also offers 3 user-programmable storage bytes for module traceability. When programming the EEPROM, an internal charge pump voltage is used; therefore a high voltage supply is not needed. The EEPROM is implemented as a shift register. During an EEPROM read, the contents are shifted 8 bits before each transmission of one byte occurs. The charge pump is internally regulated to 12.5 V, and the programming time is 6ms.

See section 2.6.1 regarding EEPROM signatures for verifying EEPROM integrity.

Note: EEPROM writing can only be performed at temperatures lower than 85°C.

#### 2.3.2. One-Wire Interface – ZACwire™

The ZSSC3015 communicates via a one-wire serial interface. There are different commands available for the following:

- Reading the conversion result of the ADC (Get\_BR\_Raw, Get\_T\_Raw)

- · Calibration commands

- Reading from the EEPROM (dump of entire contents)

- Writing to the EEPROM (trim setting, configuration, and coefficients)

# 2.4. Output Stage

### 2.4.1. Digital to Analog Converter (Output DAC) with Programmable Clipping Limits

A 12-bit DAC based on sub-ranging resistor strings is used for the digital-to-analog output conversion in the analog ratiometric and absolute analog voltage modes. Options during calibration configure the system to operate in either of these modes. The design allows for excellent testability as well as low power consumption.

The DAC allows programming a lower and upper clipping limit for the output signal (analog and digital). See Up\_Clip\_Lim and Low\_Clip\_Lim in section 3.6. The internal 14-bit calculated bridge value is compared against the 14-bit value formed by {11,Up\_Clip\_Lim[6:0],11111} for the upper limit and {00,Low\_Clip\_Lim[6:0],00000} for the lower limit. If the calculated bridge value is higher than the upper limit or less than the lower limit, the analog output value is clipped to this value; otherwise it is output as is.

**Example for the upper clipping level:** If the Up\_Clip\_Lim[6:0] = 0000000, then the 14-bit value used for the clipping threshold is 11000000011111. This is 75.19% of full scale. Since there are 7 bits of upper clipping limit, there are 127 possible values between 75.19% and 100%. Therefore the resolution of the clipping limits 0.195%.

**Example for the lower clipping level:** If the Low\_Clip\_Lim[6:0] = 1111111, then the 14-bit value used for the clipping threshold is 00111111100000. This is 24.8% of full scale. Since there are 7 bits of lower clipping limit, there are 127 possible values between 0 and 24.8%. Therefore the resolution of the lower clipping limit is 0.195%.

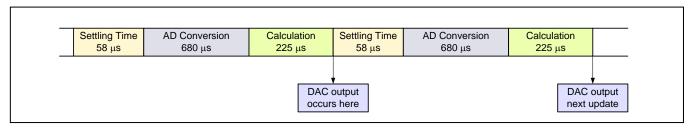

Figure 2.2 shows the data timing of the DAC output for the update rate setting 00. Refer to the ZSSC3015 Response Time Spreadsheet for details.

Figure 2.2 DAC Output Timing for Highest Update Rate

## 2.4.2. Output Buffer and Output Short Circuit Protection

A rail-to-rail op amp configured as a unity gain buffer can drive resistive loads (whether pull-up or pull-down) as low as  $5k\Omega$  and capacitances up to 15nF (for pure analog output). In addition, to limit the error due to amplifier offset voltage, an error compensation circuit is included which tracks and reduces offset voltage to < 1mV.

The output of the ZSSC3015 output can be permanently shorted to VDD or VSS without damaging the device. The output driver contains a current-limiting block that detects a hard short and limits the current to a safe level. The output short circuit protection current can vary from a minimum of 3mA to a maximum of 20mA depending on operating conditions. Output short circuit protection can be enabled via Diag\_cfg (EEPROM [102:100]). Enabling this protection is recommended when using the analog output. See Table 3.6 for settings.

### 2.4.3. Voltage Reference Block

A linear regulator control circuit is included in the Voltage Reference block to interface with an external JFET to allow operation in systems where the supply voltage exceeds 5.5V. This circuit can also be used for over-voltage protection. The regulator set point has a coarse adjustment controlled by the JFET\_cfg EEPROM bits that can adjust the set point around 5.0 or 5.5V. (See Table 3.6 for bit locations and section 2.3.1 regarding writing to the EEPROM.). The 1V trim setting (see below) can also act as a fine adjust for the regulation set point. The 5V reference can be trimmed within +/-15mV.

Note: If using the external JFET for over-voltage protection purposes (i.e., 5V at JFET drain and expecting 5V at JFET source), there will be a voltage drop across the JFET; therefore ratiometricity will be slightly compromised depending on the rds(on) of the chosen JFET. A J107 is the best choice because it has only an 8mV drop worst case. If using as regulation instead of over-voltage, a MMBF4392 or BSS169 also works well.

The Voltage Reference block uses the absolute reference voltage provided by the bandgap to produce two regulated on-chip voltage references. A 1V reference is used for the output DAC high reference when the part is configured in 0-1V Analog Output Mode. For this reason, the 1V reference must be very accurate and includes trim so that its value can be trimmed within +/- 3mV of 1.00V. The 1V reference is also used as the on-chip reference for the JFET regulator. The regulation set point of the JFET regulator can be fine-tuned using the 1V trim.

The reference trim setting is selected with the 1V\_Trim/JFET\_Trim bits in EEPROM. See Table 3.6 for bit locations. Table 2.1 shows the order of trim codes with 0111 for the lowest reference voltage and 1000 for the highest reference voltage.

**Important:** Optimal reference trim is determined during wafer-level testing and final package testing. Back-up copies of these bits are stored in bits in the CUST\_ID0 bits for applications requiring accurate references. In this case, see section 5 for important notes and instructions for verifying the integrity of the 1V\_Trim/JFET\_Trim bits and if necessary, restoring the value from the CUST\_ID0 bits before calibration.

Table 2.1 1V Reference Trim (1V vs. Trim for Nominal Process Run)

| Order                     | 1Vref/<br>5Vref_trim3 | 1Vref/<br>5Vref_trim2 | 1Vref/<br>5Vref_trim1 | 1Vref/<br>5Vref_trim0 |

|---------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Highest Reference Voltage | 1                     | 0                     | 0                     | 0                     |

|                           | 1                     | 0                     | 0                     | 1                     |

|                           | 1                     | 0                     | 1                     | 0                     |

|                           | 1                     | 0                     | 1                     | 1                     |

|                           | 1                     | 1                     | 0                     | 0                     |

|                           | 1                     | 1                     | 0                     | 1                     |

|                           | 1                     | 1                     | 1                     | 0                     |

|                           | 1                     | 1                     | 1                     | 1                     |

|                           | 0                     | 0                     | 0                     | 0                     |

|                           | 0                     | 0                     | 0                     | 1                     |

|                           | 0                     | 0                     | 1                     | 0                     |

|                           | 0                     | 0                     | 1                     | 1                     |

|                           | 0                     | 1                     | 0                     | 0                     |

|                           | 0                     | 1                     | 0                     | 1                     |

|                           | 0                     | 1                     | 1                     | 0                     |

| Lowest Reference Voltage  | 0                     | 1                     | 1                     | 1                     |

# 2.5. Clock Generator / Power-On Reset (CLKPOR)

If the power supply exceeds 2.5V (maximum), the reset signal de-asserts and the clock generator starts operating at a frequency of approximately 570kHz (±10%). The exact value only influences the conversion cycle time and communication to the outside world but not the accuracy of signal processing.

## 2.6. Diagnostic Features

The ZSSC3015 offers a full suite of diagnostic features to ensure robust system operation in the most "mission-critical" applications. If the part is programmed in Analog Output Mode, then diagnostic states are indicated by an output below 2.5% of VDD or above 97.5% of VDD. If the part is programmed in Digital Output Mode, then diagnostic states will be indicated by a transmission with a generated parity error.

Table 2.2 gives a summary of the diagnostic features, which are explained in detail in the following sections. EEPROM settings that control diagnostic functions are given in section 3.6.

Table 2.2 Summary of Diagnostic Features

| Detected Fault                            | Analog<br>Diagnostic Level | ZACwire™ Diagnostic    | Delay in Detection                             |

|-------------------------------------------|----------------------------|------------------------|------------------------------------------------|

| EEPROM signature                          | Lower                      | Generates parity error | 11ms after power-on <sup>†</sup>               |

| Loss of bridge positive                   | Upper                      | Generates parity error | 2ms                                            |

| Loss of bridge negative                   | Upper                      | Generates parity error | 2ms                                            |

| Open bridge connection                    | Upper                      | Generates parity error | 2ms                                            |

| Bridge input short                        | Upper                      | Generates parity error | 2ms                                            |

| ExtTemp pin open                          | Lower                      | Generates parity error | 300ms                                          |

| ExtTemp pin shorted to PWR/GND            | Lower                      | Generates parity error | 300ms                                          |

| ExtTemp pin shorted to BP/BN <sup>‡</sup> | Upper                      | Generates parity error | 3ms                                            |

| Loss of VDD                               | Lower                      | Transmissions stop     | Dependent on R <sub>L</sub> and C <sub>L</sub> |

| Loss of VSS                               | Upper                      | Transmissions stop     | Dependent on R <sub>L</sub> and C <sub>L</sub> |

## 2.6.1. EEPROM Integrity

The contents of the EEPROM are protected by an 8-bit LFSR signature (linear feedback shift register). This signature is regenerated and stored in EEPROM every time EEPROM contents are changed. This signature is generated and checked for a match after Power-On Reset prior to entering Normal Operation Mode. If the generated signature fails to match, the part will output a diagnostic state on the output.

In addition to an extensive temporal and code interlock mechanism used to prevent false writes to the EEPROM, the ZSSC3015 offers an EEPROM lock mechanism for high-security applications. When EEPROM bits 105:103 are programmed with "011" or "110," this 3-bit field will disable the VPP charge pump and will not allow further writes to the EEPROM.

#### 2.6.2. Sensor Connection Check

Four dedicated comparators permanently check the range of the bridge inputs (BP/BN) to ensure they are within the envelope of 0.8V to 0.85\*VDD during all conversions. The two sensor inputs have a switched ohmic path to ground and if left floating, would be discharged. If any of the wires connecting the bridge break, this mechanism will detect it and put the ZSSC3015 in a diagnostic state. This same diagnostic feature can also detect a short between BP/BN and the ExtTemp signal if an external diode is being used for temperature measurement. See Table 2.2 in section 2.6 for more information.

\_\_\_

<sup>\*</sup> All timings assume nominal operating frequency of 570kHz.

<sup>&</sup>lt;sup>†</sup> Assumes standard command window. If fast startup is enabled, the delay is 4ms.

<sup>&</sup>lt;sup>‡</sup> A short from ExtTemp to BP/BN might not be detected in some circuit configurations.

#### 2.6.3. Sensor Short Check

If a short occurs between BP/BN (bridge inputs), it would normally produce an in-range output signal and therefore would not be detected as a fault. This diagnostic mode, if enabled, will deliberately look for such a short. After the measurement cycle of the bridge, it will deliberately pull the BP bridge input to ground for  $4\mu$ sec. At the end of this  $4\mu$ sec window, it will check to see if the BN input "followed" it down below the 0.8V comparator checkpoint. If so, a short must exist between BP/BN, and the ZSSC3015 will output a diagnostic state. The bridge will have a minimum of  $480\mu$ sec recovery time prior to the next measurement. See Table 2.2 in section 2.6 for more information.

The bridge resistance must be taken into account if the Sensor Short diagnostic feature is used. At  $V_{DD} = 2.7V$ , the minimum bridge resistance is  $0.3K\Omega$ , and at  $V_{DD} = 5V$ , the minimum bridge resistance is  $0.6K\Omega$ .

#### 2.6.4. Power Loss Detection

If the power or GND connection to the module containing the sensor bridge and ZSSC3015 is lost, the ZSSC3015 will output a diagnostic state if a pull-up or pull-down terminating resistor greater than or equal to  $5k\Omega$  is connected in the final application. This diagnostic mode only functions when the part is configured in Analog Output Mode. For more information, see Table 2.2 in section 2.6.

### 2.6.5. ExtTemp Connection Checks

When external temperature is selected and connection checking is enabled, the part performs range checking on the converted temperature value. If the internal ADC reading of the temperature is less than 1/32 of full scale or greater than 63/64 of full scale then a diagnostic state is asserted. If the ExtTemp pin is shorted to ground, the ADC reads less than 1/32. Because 100µA is sourced onto the ExtTemp pin during conversions, it naturally pulls up during these times. If the ExtTemp pin is open, it produces an ADC reading greater than 63/64 of full scale. Both these bad connection conditions would be detected and result in a diagnostic output. If internal temperature is selected or sensor connection check is not enabled, then this diagnostic check is not enabled. See Table 2.2 in section 2.6 for more information.

# 3 Functional Description

# 3.1. General Working Mode

The command/data transfer takes place via the one-wire Sig<sup>™</sup> pin using the ZACwire<sup>™</sup> serial communication protocol.

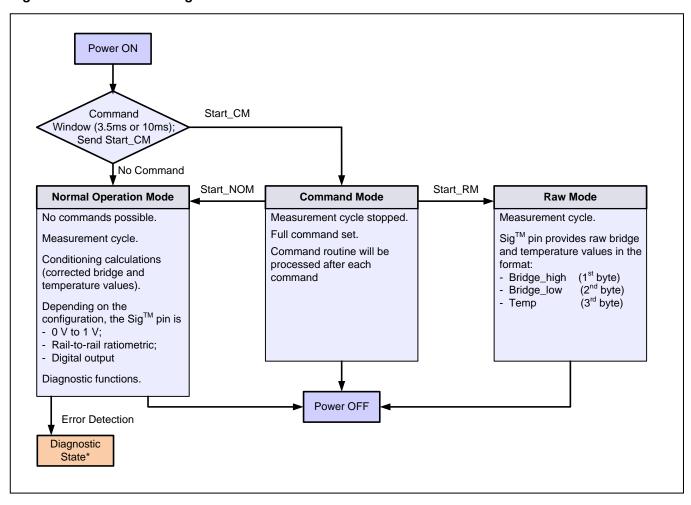

After power-on, the ZSSC3015 provides a command window for 3.5ms or 10ms. (The command window length depends on the setting of the Fast\_Startup EEPROM bit; see section 3.6). During the command window, the ZSSC3015 is waiting for a Start\_CM command. Without this command, the Normal Operation Mode (NOM) starts. In this mode, raw bridge values are converted and the corrected values are presented on the output in analog or digital format (depending on the configuration stored in EEPROM). If the ZSSC3015 receives the Start\_CM command during the command window, it remains in Command Mode (CM). The CM allows changing to one of the other modes via command. (See section 3.4 for command encoding.) If the Start\_RM command is sent, the ZSSC3015 enters the Raw Mode (RM). Without correction, the raw values are transmitted to the digital output in a predefined order. The RM can only be stopped by a power down. Raw Mode is used by the calibration software for collection of raw bridge and temperature data so the correction coefficients can be calculated.

If diagnostic features are enabled and a diagnostic fault is detected, diagnostic states are indicated as follows depending on the programmed mode:

- In Analog Output Mode:

Diagnostic states are indicated by an output below 2.5% of VDD or above 97.5% of VDD.

- In Digital Output Mode:

Diagnostic states will be indicated by a transmission with a generated parity error.

For more details, see section 2.6.

Figure 3.1 General Working Mode

<sup>\*</sup> See section 2.6.

# 3.2. Normal Mode Sample Rate

When the ZSSC3015 is in Normal Operation Mode, the output rate depends mainly on the settings for the update rate and Output Mode. Table 3.1 shows the nominal sample rate for analog output across update rate settings for Analog Output Mode. See section 3.3.4 for information on reading the ZSSC3015 and the overall update and transmission time when in Digital Mode. The average response time shown in Table 3.1 accounts for 1.5 samples at nominal frequency and temperature. The worst-case response time accounts for process and temperature deviation on the oscillator. The worst case only occurs if the input changes immediately prior to a special measurement. See the ZSSC3015 Response Time Spreadsheet for details on the average and worst-case response time depending on the ZSSC3015 configuration.

Table 3.1 Update Rate for Analog Output

| Update Rate Setting | Sample Rate | Average Response Time | Worst Case Response Time | Unit |

|---------------------|-------------|-----------------------|--------------------------|------|

| 00                  | 0.96        | 1.44                  | 3.3                      | ms   |

| 01                  | 4.4         | 6.68                  | 15.7                     | ms   |

| 10                  | 20.2        | 31.58                 | 72.4                     | ms   |

| 11                  | 105.2       | 171.02                | 377.4                    | ms   |

# 3.3. ZACwire™ Communication Interface

## 3.3.1. Properties and Parameters

Table 3.2 ZACwire™ Parameters

| Parameter                                          | Symbol                  | Min | Тур | Max | Unit     | Comments                                                                                                                                                               |

|----------------------------------------------------|-------------------------|-----|-----|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZACwire™ frequency 1)                              | f <sub>ZAC</sub>        | 30  | 36  | 40  | kHz      | Command Mode or<br>Update Rate = 0 or 1                                                                                                                                |

|                                                    |                         | 7   | 9   | 10  |          | Update Rate = 2 or 3                                                                                                                                                   |

| Pull-up resistor (on-chip)                         | R <sub>ZAC,pu</sub>     |     | 30  |     | kΩ       | On-chip pull-up resistor switched on during Digital Output Mode and during Command Mode (first 3ms after power up)                                                     |

| Pull-up resistor (external)                        | R <sub>ZAC,pu_ext</sub> | 150 |     |     | Ω        | If the master communicates via a push-pull stage, no pull-up resistor is needed; otherwise, a pull-up resistor with a value of at least $150\Omega$ must be connected. |

| ZACwire™ rise time                                 | t <sub>ZAC,rise</sub>   |     |     | 5   | μs       | Any user RC network included in Sig <sup>™</sup> path must meet this rise time                                                                                         |

| ZACwire <sup>™</sup> line resistance <sup>2)</sup> | RzACload                |     |     | 3.9 | kΩ       |                                                                                                                                                                        |

| ZACwire™ load capacitance 2)                       | C <sub>ZAC,load</sub>   | 0   | 1   | 15  | nF       |                                                                                                                                                                        |

| Voltage low level 3)                               | $V_{ZAC,low}$           |     | 0   | 0.2 | $V_{DD}$ | Rail-to-rail CMOS driver                                                                                                                                               |

| Voltage high level 3)                              | V <sub>ZAC,high</sub>   | 8.0 | 1   |     | $V_{DD}$ | Rail-to-rail CMOS driver                                                                                                                                               |

<sup>1)</sup> Output frequency only. The master should communicate with the ZSSC3015 at 20kHz to 52kHz when it is in Command Mode.

# 3.3.2. Bit Encoding

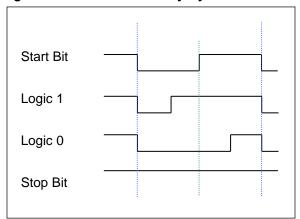

Figure 3.2 Manchester Duty Cycle

Start bit = 50% duty cycle used to set up strobe time

Logic 1 = 75% duty cycle

Logic 0 = 25% duty cycle

Stop Bit = The ZACwire<sup>TM</sup> bus will be held high for 1 bit length between consecutive data packets.

See *Technical Note – ZACwire*  $^{TM}$  *Communication* for more details on the ZACwire  $^{TM}$  protocol.

<sup>2)</sup> The rise time must be  $t_{ZAC,rise} = 2 * R_{ZACload} * C_{ZACload} * 5 \mu s$ . If using a pull-up resistor instead of a line resistor, it must meet this specification. The absolute maximum for  $C_{ZACload}$  is 15nF.

<sup>3)</sup> No verification in mass production; the parameter is guaranteed by design and/or quality observation.

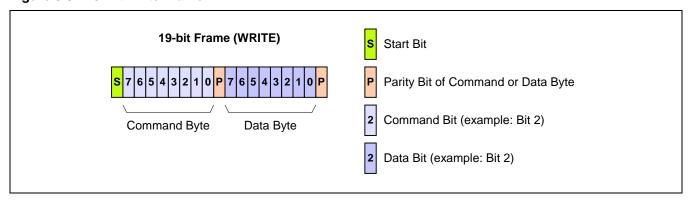

## 3.3.3. Write Operation from Master to ZSSC3015

The calibration master sends a 19-bit packet frame to the ZSSC3015.

Figure 3.3 19-Bit Write Frame

The incoming serial signal will be sampled at a 570kHz clock rate. This protocol is very tolerant to clock skew, and can easily tolerate a wide range of baud rates. The incoming baud rate should be in the 8kHz to 52kHz range (36kHz nominal).

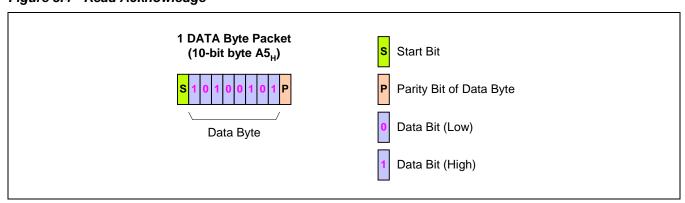

# 3.3.4. ZSSC3015 Read Operations

The incoming frame will be checked for proper parity on both command and data bytes, as well as for any edge time-outs prior to a full frame being received.

After a command/data pair is received, the ZSSC3015 will perform that command. After the command has been successfully executed by the ZSSC3015, it will acknowledge success by a transmission of an A5<sub>HEX</sub> byte back to the master. If the master does not receive an A5<sub>H</sub> transmission within 130ms of issuing the command, it must assume the command was either improperly received or could not be executed.

Figure 3.4 Read Acknowledge

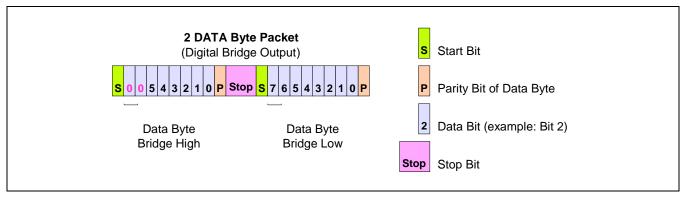

The ZSSC3015 transmits 10-bit bytes (1 start bit, 8 data bits, 1 parity bit). During calibration and configuration, transmissions are normally either  $A5_{HEX}$  or data.  $A5_{HEX}$  indicates successful completion of a command. There are two different digital output modes configurable (digital output with temperature and digital output with only bridge data). During Normal Operation Mode, if the part is configured for digital output of the bridge reading, it first transmits the high byte of bridge data, followed by the low byte. The bridge data is 14 bits in resolution, so the upper two bits of the high byte are always zero-padded. There is a stop bit time between bytes in a packet. This means that for the time of a bit width, the signal level is high.

Figure 3.5 Digital Output (NOM) Bridge Readings

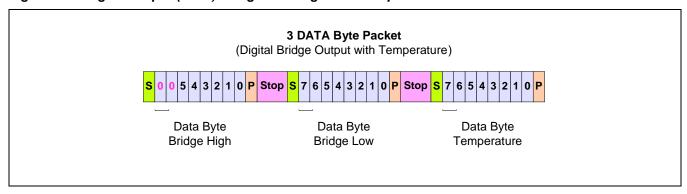

The second option for Digital Output Mode is digital output bridge reading with temperature. It will be transmitted as 3 data packets. The temperature byte represents an 8-bit temperature quantity spanning from -50 to 150°C.

Figure 3.6 Digital Output (NOM) Bridge Readings with Temperature

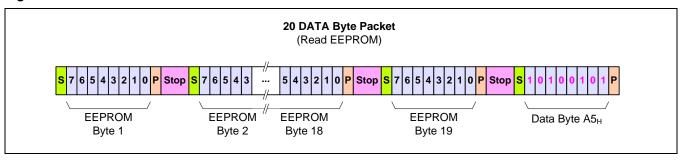

The EEPROM transmission occurs in a packet with 20 data bytes, as shown in Figure 3.7.

Figure 3.7 Read EEPROM Contents

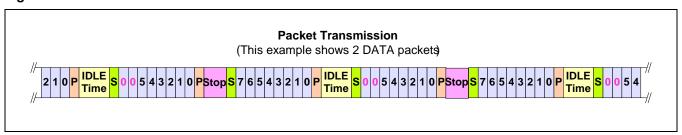

There is a variable idle time between packets. This idle time varies with the update rate setting in EEPROM.

Figure 3.8 Transmission of a Number of Data Packets

Table 3.3 shows the idle time between packets versus the update rate. This idle time can vary by nominal +/-15% between parts and over a temperature range of -50 to 150°C. The idle time is extended by the time of one conversion at each special measurement.

Table 3.3 Idle Time between Packets versus Update Rate

| Update Rate Setting | Idle Time between<br>Packets | Idle Time at Special<br>Measurements every (xx)<br>Packets |

|---------------------|------------------------------|------------------------------------------------------------|

| 00                  | 1ms                          | 1.83ms (128)                                               |

| 01                  | 4.33ms                       | 5.16ms (64)                                                |

| 10                  | 20.3ms                       | 21.1ms (16)                                                |

| 11                  | 106ms                        | 107ms (8)                                                  |

Transmissions from the ZSSC3015 occur at one of two speeds depending on the update rate programmed in EEPROM. If the user chooses one of the two fastest update rates ( $00_{BIN}$  or  $01_{BIN}$ ) then the baud rate of the digital transmission will be 36kHz. However, if the user chooses one of the two slower update rates ( $10_{BIN}$  or  $11_{BIN}$ ), then the baud rate of the digital transmission will be 9kHz.

The total transmission time for both digital output configurations is shown in Table 3.4.

Table 3.4 Total Transmission Time for Different Update Rate and Output Configurations

| Update Rate<br>Setting | Baud Rate* | Idle Time |         | smission Ti |          |         | smission Ti | -        |

|------------------------|------------|-----------|---------|-------------|----------|---------|-------------|----------|

| 00                     | 36 kHz     | 1.0 ms    | 21 bits | 27.7 µs     | 1.6 ms   | 32 bits | 27.7 µs     | 1.9 ms   |

| 01                     | 36 kHz     | 4.33 ms   | 21 bits | 27.7 μs     | 4.9 ms   | 32 bits | 27.7 µs     | 5.2 ms   |

| 10                     | 9 kHz      | 20.3 ms   | 21 bits | 111.1 µs    | 22.6 ms  | 32 bits | 111.1 µs    | 23.9 ms  |

| 11                     | 9 kHz      | 106 ms    | 21 bits | 111.1 µs    | 108.3 ms | 32 bits | 111.1 µs    | 109.6 ms |

<sup>\*</sup> Typical values. See Table 3.2 for details.

For lower update rates, the output is followed by a power-down as shown in Figure 3.9.

Figure 3.9 ZACwire™ Output Timing for Lower Update Rates

|  | Calculation 225 μs | ZACwire <sup>™</sup><br>Output | Power Down<br>(determined by<br>Update Rate) | Power-On<br>Settling<br>114 µs | Settling Time<br>58 μs | ADC Conversion 680 μs | Calculation<br>225 μs | ZACwire <sup>TM</sup><br>Output |

|--|--------------------|--------------------------------|----------------------------------------------|--------------------------------|------------------------|-----------------------|-----------------------|---------------------------------|

|--|--------------------|--------------------------------|----------------------------------------------|--------------------------------|------------------------|-----------------------|-----------------------|---------------------------------|

It is easy to program any standard microcontroller to communicate with the ZSSC3015. IDT can provide sample code for a MicroChip PIC<sup>®</sup> microcontroller.

#### 3.3.5. High Level Protocol

The ZSSC3015 will listen for a command/data pair to be transmitted for the 3.5ms or 10ms (depending on the setting of the Fast\_Startup EEPROM bit; see section 3.6) after the de-assertion of its internal Power-On Reset (POR). If a transmission is not received within this time frame, then it will transition to Normal Operation Mode (NOM). In the NOM, it will output bridge data in 0-1V analog, rail-to-rail ratiometric analog, or digital depending on how the part is currently configured.